以太网数据转发约束的高速LDPC 码设计

2016-12-05李霈霈周志刚那美丽

李霈霈,周志刚,那美丽

(中国科学院 上海微系统与信息技术研究所,上海200050)

以太网数据转发约束的高速LDPC 码设计

李霈霈,周志刚,那美丽

(中国科学院 上海微系统与信息技术研究所,上海200050)

为了灵活支持多种高速以太网接口,将低密度奇偶校验(LDPC)编码运用在以太网数据转发,取消传统数据包解码,提出了LDPC并行编码架构。在考虑1G到100G以太网物理层编码码字长度约束的基础上,分别设计了针对1G、10G、100G接口中最大通道速率的LDPC(192,120),LDPC(594,462),LDPC(1188,990)码字,实现了信道编码处理的低时延。仿真结果表明,构造的准循环LDPC码误码性能优,系统的处理时延小(考虑了编码时延和译码时延)。LDPC编码时延在0.58~1.17 μs之间,译码时延在3.20~4.26 μs之间,可以满足不同以太网接口的最大通道编译速率。

以太网接口;数据转发;并行编码架构;编码时延;译码时延

以太网是现有局域网采用的最通用的通信协议标准。海量数据的交互对网络带宽的需求不断在拓展,以太网的传送速度也正以10倍速向前发展,经历了从10 Mbps到100 Mbps 到1 Gbps到10 Gbps到100 Gbps的递进[1]。如此巨大的数据传输速率用光缆是很容易支持的,但是光缆的可用性是受到限制的,发展高速率无线通信替代有线解决方案成为了大势所趋。

纠错码被用来提高信道传输的可靠性,因为它可以检测并纠正信号传输过程中引入的错误。好的纠错码技术已成为提供通信系统可靠传输的一种手段。低密度奇偶校验码(LDPC)具有优异的译码性能,将LDPC作为信道纠错码可以保证通信系统正确的高速通信[2]。

传统以太网的数据传输中,以太帧经过数据包的解码处理,然后连接到发送链路的纠错码模块进行信道编码。

文中提出以太网数据转发约束的LDPC码字,根据以太网物理层串行收发编码方式,设计LDPC信息位与码长,将以太网接口数据包直接传送给LDPC编码器,取消MAC解码,

1 系统框架

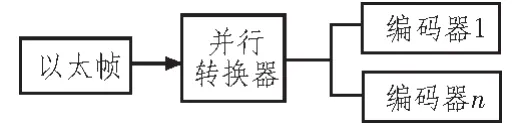

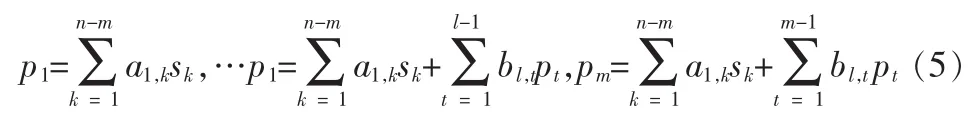

传统的编码框架主要包括以太帧、缓冲器、数据包解码和编码器部分。以太帧以串行的方式输入到数据包解码模块,然后拆分并重新打包输出到编码器中进行编码。本文在传统编码框架基础上取消了数据包解码过程,以并行转换的方式将以太网的数据包直接并行送入编码器,不进行解析。这将大大降低系统的处理时延。基于并行架构的编码框架如图1所示。

图1 并行架构的以太网数据传输的编码框架

针对文中考虑1G-100G以太网接口的最大通道速率传输,信道编译码字选择受限于以太网物理层编码码字长度。LDPC码字信息位数选择为以太网物理层编码码字长度的整数倍,这可以将以太网数据包直接送入编码器进行编码,免去了以太网数据包的解析过程。1 GE物理层采用8B/10B的编码方式[3],使用单通道结构,通道编译的信息位数为10 bit,选择信息位数为10的倍数的LDPC码字;10 GE和100 GE物理层采用64B/66B的编码方式[4],使用双通道并行结构,每通道编译33 bit信息位,选择信息位数为33的倍数的LDPC码字。

2 以太网数据转发约束的LDPC码字构造

以太网数据转发约束的LDPC码采用准循环码字,QCLDPC码字可以有效的减小信道误码,而且由于其结构的特殊性,使其编译码具有复杂度低、存储空间少、码的设计灵活和硬件实现简单等优点[5]。定义QC-LDPC码的校验矩阵H 由c×t个循环子矩阵组成,其中c、t均为正整数,且有c≤t。

Ai,j(1≤i≤c,1≤j≤t)是大小为b×b的循环子矩阵,且每个循环矩阵Ai,j的行(列)重相对其大小b而言都较小。

LDPC码字信息位长度主要从接口物理层编码码字长度考虑。在对应关系上,LDPC码字信息位长度应为接口物理层编码码字长度的整数倍。LDPC码率主要从满足通道速率考虑。

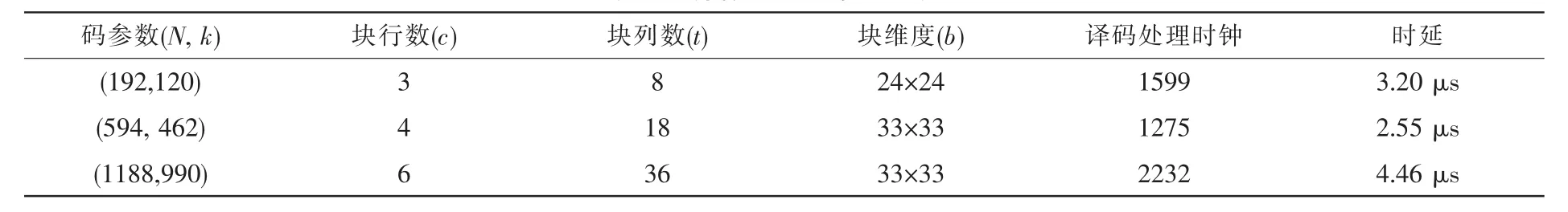

表1 数据转发约束的LDPC码矩阵参数

要构造具有良好的纠错性能的LDPC码,必须满足3个条件,分别是无短环、无低码重码字、码间最小距离要尽可能大。环的存在使得迭代过程中的独立性假设不能成立,译码的最优性能得不到满足。校验矩阵H中有任何4个“1”分别在矩形的4个顶点上,则围线构成了一个4环。

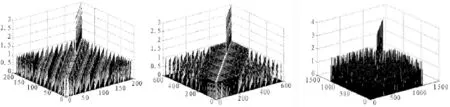

为了便于检验文中所设计的LDPC码字无四环,在高斯信道下,采用BPSK调制方式,用Matlab软件对设计的LDPC码字仿真并给出性能曲线。引用文献[6]中的检验算法。假设辅助矩阵O为:O=HTH,当且仅当辅助矩阵O中除对角线元素外输出项值均为1时,校验矩阵H没有四环。

图2 3种设计的码字辅助矩阵O元素值分布

3种设计的LDPC码字的辅助矩阵元素值分析如图2。Matlab仿真结果表明,矩阵O的非对角线均为1元素,QCLDPC的校验矩阵H中无四环存在。这证明了构造的LDPC码字为好码,并为其实现良好的误码性能提供了理论基础。

3 LDPC码编译码器设计与实现

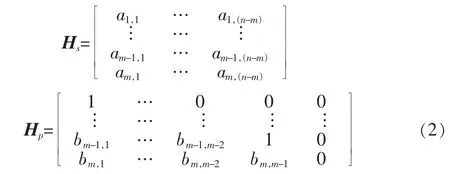

对于高速以太网接口下设计的LDPC码字,其基础校验矩阵的结构形式如式(2)。首先将校验矩阵变换为H=[HsHp],Hs和Hp分别对应编码序列的信息位和校验位部分[7]。

定义编码后的码字矢量x=(s,p)。码字x满足:

编码运算在二元域中,可以得到

代入式(2),可得

式中:V为设计调蓄容量,m3;ri为降雨强度曲线上对应降雨历时ti的降雨强度,mm/h;rc为调蓄池出流过流能力值对应的降雨强度,mm /h;ti为任意降雨历时,s;α为径流系数,hm2;A为流域面积,hm2.

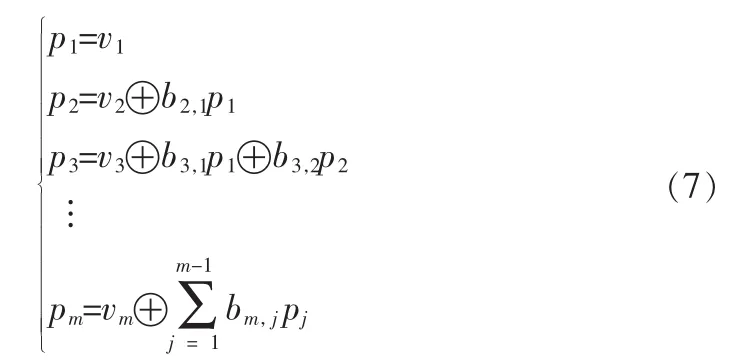

整个编码过程分为两个子过程:乘法过程和前向迭代过程。

设向量vT=Hs×sT,vT可以通过Hs与(s1,s2,…,sm)T相乘得到,这个过程称为乘法过程[8]。

Hp是H矩阵变换中下三角矩阵,在计算pT时,比较直接的方法是先求矩阵Hp的逆矩阵,然后计算等式。然而,矩阵的逆是一个复杂的运算,求逆的过程可能破坏了矩阵的稀疏性,那么得到的计算复杂度将和码长的二次方成正比。在此,较好的解决方法是利用Hp的下三角特性,采用前向迭代的方法。等式的计算只需要异或操作就可以实现,如下式

图3 编码整体框架图

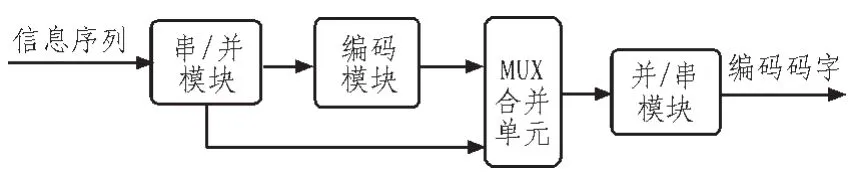

在整体框架上[9],信息序列首先进行串并转换,然后送入相应编码器中,编码模块基于校验矩阵的编码算法,已知信息序列求得码字的校验部分,然后将信息序列和校验比特合并得到全部码字。最后,并串转换恢复成编码码字数据流。

表2 编码码字的计算时钟周期及时延

10 G以太网接口下,QC-LDPC编码器的时延为0.71 μs,这也与许多商用LDPC码字IP的编码时延相当[10]。

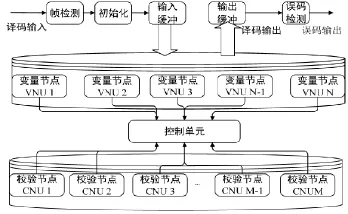

部分并行的译码器结构可以实现很高的数据吞吐率,在高速传输的系统中我们给出以下译码结构。VNU代表Log-BP算法中变量节点处理单元,CNU代表校验节点处理单元。

图4 部分并行的LDPC译码框架

如图4译码整体框架[11-13],硬件译码器由数据输入缓冲模块、变量节点处理模块、校验节点处理模块和判决结果输出缓冲模块4个模块共同组成。以码字(192,120)为例,校验矩阵是由3×8个子矩阵组成,每个子矩阵均为循环阵,变量节点VNU N=8,校验节点CNU M=3。

译码器设计的时延主要来自于VNU和CNU单元[14]。分析评估最大时延的公式如下,CNU运算一次需要m个时钟周期,VNU运算一次需要n个时钟周期,那么并行迭代一次所需要总的时钟周期为m+n。下表给出了20次迭代的情况下,根据子矩阵划分的大小,使用功能时钟500 MHz时对应的译码处理时间。

在500 MHz功能时钟下,译码器的最大延迟为4.46μs,文中的设计在时延较小的情况下获得了较大的译码吞吐量。

4 性能仿真及分析

文中在Matlab环境下对表1中设计的LDPC码字进行了仿真。信道选择为AWGN信道,调制方式为BPSK,得到的误码率曲线如图5所示。

表3 并行译码器的处理时延

图5 误码率曲线

图5表明3种码字的误码率均可以在信噪比小于8 dB时达到10-6。码长较长的码字编码增益更大。在误码率为10-6时,LDPC III码字的增益比LDPC II提高0.3 dB,比LDPC I的增益提高0.5 dB。因此,良好的纠错性能使得设计的码字可以运用在高速通信系统中。

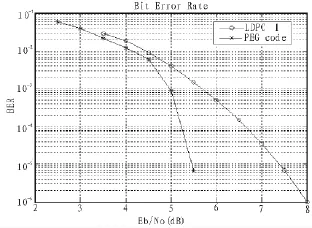

图6 LDPC I和PEG误码率比较

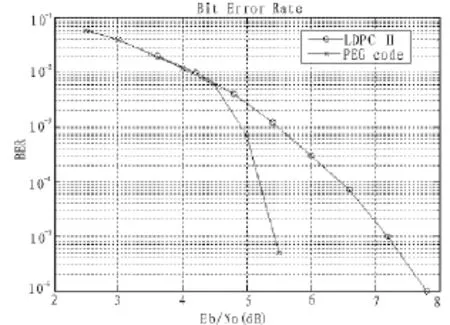

为了进一步比较码字性能,将3种LDPC码字误码率和PEG法构造的码字误码率比较。PEG法是随机构造的码一种。PEG(Progressive Edge-Growth)方法在构造上使变量节点的局部环长最大。在二分图上,前i-1个变量节点的边已经构造出来,在构造下一个变量节点的边时,每次向二分图上添加一条边,新添加的边使得经过第i个变量节点的最小环长最大[15-17]。

图7 LDPC II和PEG误码率比较

图8 LDPC III和PEG误码率比较

由图6,7和8看出,在相同码率,相同对数似然比BP算法,相同迭代次数时,QC-LDPC码字的错误平层远低于PEG-LDPC码,该特性可以满足高速通信系统中低错误平层的要求,实现以太网接口的长距离传输。

5 结 论

文中在考虑1G-100G以太网物理层编码码字长度的基础上,设计了针对最大速率的3种以太网数据转发约束的QC-LDPC码字,实现了接口信道编码处理的低时延。仿真结果表明,3种LDPC码字编码增益较高,且低于PEG-LDPC码的错误平层。编码以及并行译码框架的分析,编码时延在0.58~1.17 μs之间,译码时延在3.20~4.26 μs之间,可以满足不同以太网接口的最大通道编译速率。

[1]王小军.100G以太网技术概述 [J].江苏广播电视大学学报,2010,5(21):61-64.

[2]高明.LDPC编码调制研究[D].杭州:浙江大学,2008.

[3]李玉伟,潘明海.8B/10B编码对高速传输的影响分析[J].信息安全与通信保密,2011(3):41-43.

[4]Roy R,Hajduczenia M,Kramer G,et al.10G-EPON efficiency[C]//Proceedings of the 3rd international conference onAdvancednetworksandtelecommunicationsystems. IEEE Press,2009:16-18.

[5]Li Z,Chen L,Zeng L,Lin S.Efficient Encoding of Quasi-CyclicLow-DensityParity-CheckCodes[J].IEEE Transactions on Communications,2006,54(1):71-81.

[6]Xiao Y,Lee M H.Low complexity MIMO-LDPC CDMA systems over multipath channels[J].IEICE Transactions on Communications,2006,89(5):1713-1717.

[7]Sun X R,Zeng Z,Yang Z.A novel low complexity LDPC encoder based on optimized RU algorithm with backtracking [C]//Multimedia Technology(ICMT),2010 International Conference on.IEEE,2010:1-4.

[8]范志明.基于LDPC的编码调制理论及其硬件设计的研究[D].北京邮电大学,2014.

[9]庄梦溪.高速LDPC码编译码器的研究与实现[D].西安电子科技大学,2012.

[10]802.11n/802.11ac LDPC Decoder RTL Data sheet,2009-11 Blue Rum Consulting Limited,2011.

[11]Mankar M V,Patil A,Asutkar G M.Single mode quasicyclic LDPC decoder using modified belief propagation[C]// Communications and Signal Processing(ICCSP),2014 International Conference on.IEEE,2014:862-866.

[12]Liu K,Lin S,Abdel-Ghaffar K.A Revolving Iterative Algorithm for Decoding Algebraic Cyclic and Quasi-Cyclic LDPC Codes[J].Communications,IEEE Transactions on,2013,61(12):4816-4827.

[13]Park Y S,Blaauw D,Sylvester D,et al.Low-Power High-Throughput LDPC Decoder Using Non-Refresh Embedded DRAM[J].IEEE Journal of Solid-State Circuits,2014,49 (3):783-794.

[14]朱嘉.LDPC码的实现及其应用[D].上海交通大学,2007.

[15]Yang X,Wang L,Li Y.Performance of Q-ary PCGC based on PEG algorithm[C]//Intelligent Signal Processing and Communication Systems,2007.ISPACS 2007.International Symposium on.IEEE,2007:1-4.

[16]戚磊,韩喆,陈双,等.S7-1200以太网通信的真空造浪测控系统设计与实现[J].工业仪表与自动化装置,2016(3):31-34.

[17]赵中玉,刘文莉.基于以太网的发电机组测试负载系统设计[J].工业仪表与自动化装置,2016(5):64-67.

High speed LDPC code design for ethernet data transmission

LI Pei-pei,ZHOU Zhi-gang,NA Mei-li

(Shanghai Institute of Microsystem and Information Technology,Chinese Academy of Sciences,Shanghai 200050,China)

This paper presented interface-aware Low Density Parity Check(LDPC)codes in parallel encoding framework to support high-speed Ethernet data transmission and cancel the packets decoding process.Considering constraints of encoded codeword length of 1G to 100G Ethernet physical layer,LDPC(192,120),LDPC(594,462),LDPC(1188,990)codes aiming the maximum channel rate for 1G,10G and 100G Ethernet interface were designed to reach low latency in channel coding process.The simulation results claimed that LDPC codes have excellent performance and minimum processing delay in system,taking encoding delay and decoding delay into consideration.The encoding delay of 0.58~1.17 μs and the decoding delay of 3.20~4.26 μs could meet the maximum code rate for different channels in Ethernet interfaces.

Ethernet interface;data transmission;parallel encoding framework;encoding delay;decoding delay

TN911.22

A

1674-6236(2016)22-0001-04

2016-04-06稿件编号:201604052

国家高技术研究发展计划(863计划)(SS2015AA011307);上海市自然科学基金(15ZR1447600)

李霈霈(1991—),女,安徽马鞍山人,硕士研究生。研究方向:毫米波高速通信中LDPC编译码技术。使通信系统具有更小时延(考虑编码时延和译码时延)。