基于Sobel算法图像边缘检测的FPGA实现

2016-12-02杜正聪宁龙飞

杜正聪,宁龙飞

(1.攀枝花学院 电气信息工程学院,四川 攀枝花 617000;2.西华大学 机械工程学院,四川 成都 610039)

基于Sobel算法图像边缘检测的FPGA实现

杜正聪1,宁龙飞2

(1.攀枝花学院 电气信息工程学院,四川 攀枝花 617000;2.西华大学 机械工程学院,四川 成都 610039)

针对嵌入式软件无法满足数字图像实时处理速度问题,提出用硬件加速器的思想,通过FPGA实现Sobel边缘检测算法。通过乒乓操作、并行处理数据和流水线设计,大大提高算法的处理速度。采用模块的硬件设计,保证了系统的可移植性和系统的扩展性。最后使用Verilog HDL编程实现算法处理,并用Modelsim和 MATLAB进行了仿真和验证。

FPGA;Sobel边缘检测;硬件加速器

0 引言

图像的边缘检测是数字图像处理领域的一项关键技术,是图像分割、运动检测、目标跟踪、人脸识别等技术的基础[1]。随着电子信息技术的高速发展,图像的边缘检测在航天、工业、医学、军事等领域有着广泛的应用和发展[2]。在这些应用中,通常选用ARM和DSP等作为处理器,通过嵌入式软件来处理信息,但随着待处理信息量越来越大,算法复杂度越来越高,单核处理器处理速度已不能满足某些系统的需求。

本文在研究Sobel算法[3]的基础上,针对嵌入式软件无法满足实时数据处理速度的要求,引入硬件加速器的思想,采用RAM+FPGA硬件结构,通过嵌入式软件提供从机接口,控制加速器进行工作,硬件加速器(FPGA)通过模块化设计,采用流水线设计和乒乓操作大幅提高实时处理数据速度,实现图像的边缘检测。从机接口一般通过嵌入式软件读写寄存器来完成。

1 边缘检测和Sobel算法

边缘检测是分析视频和图像的重要方法,主要检测和确定图像在哪些区域上亮度发生突变,这些亮度突变的区域通常就是物体的边缘。

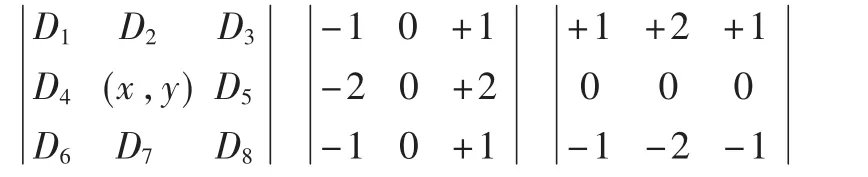

以灰度图像为例,分辨率为M×N的图像由M×N个像素组成。Sobel检测法把中心像素点和离它最近的 8个像素点每个乘以一个系数后相加,类似卷积的过程来估计每个像素点x、y方向上的导数值。该系数通常用一个卷积表(Convolution Mask)来表示。分别用于计算x和y方向导数值的Sobel卷积表 Dx和 Dy如下所示[4]:

把每个像素值分别乘以卷积表中对应的数,再把相乘得到的9个数相加就得到了x方向和y方向的偏导数值Dx和Dy。然后,利用这两个偏导数值计算中心像素点的导数。

计算公式如下:

由于开平方和平方函数都是单调的,实际计算幅度的最大值、最小值与近似以后计算的最大值、最小值发生在图像的同一个地方。并且,与计算平方和开平方相比,计算绝对值所用的硬件资源少得多。若要找到导数幅值的最大值和最小值,对式(1)作如下简化:

需要重复地计算图像中每个像素位的导数幅值。但是,注意到环绕图像边缘的像素点并没有一个完整的相邻像素组来计算偏导数和导数,所以要对这些像素进行单独处理。最简单的方法就是把图像中边缘像素点的导数值|D|设置为0。

2 Sobel边缘检测法的硬件实现

2.1Sobel加速器结构

硬件加速实质上是通过增加运算并行性达到加速的目的,常常采用硬件复制和流水线的方法。

边缘检测加速器系统的原理框图如图1所示。视频或图像数字信号通过 I/O控制器输入,保存在存储器中;在RAM处理器控制下运行的硬件加速器,读入存储器中存储的帧图像(数据),并进行边缘检测算法实现,最后将得到相应的导数图像写入存储器。在实际应用中,选取硬件加速器对时耗大的算法进行加速,大大降低其他处理器(如 DSP、ARM 等)的负担。

图1 硬件加速器系统的原理框图

I/O控制器和加速器通过DMA(Direct Memory Access)方式直接发起对内存的访问而不通过处理器,大大加快访问内存的速度。为避免多个设备同时访问内存发生冲突,在系统中引入仲裁器。仲裁器的仲裁策略为:唯一申请者获得资源。这样,ARM(CPU)对加速器进行配置,配置待处理数据源地址和目标地址,然后启动加速器,释放总线资源;ACC在接收到启动命令之后,要申请资源,完成算法实现后,用中断的方式反馈给RAM(CPU),同时释放资源。

2.2基于FPGA的硬件加速器

图像边缘检测数据具有数据量大,可并行处理及重复操作等特点,用FPGA可实现硬件并行处理信息;通过流水线设计技术和乒乓操作的架构设计,可以进一步提高实现算法组合逻辑处理速度和系统处理信息的吞吐量,因此FPGA对处理图像边缘检测数据有着天然的优势。本文采用面向流处理的加速器处理按照顺序到达的数据流。

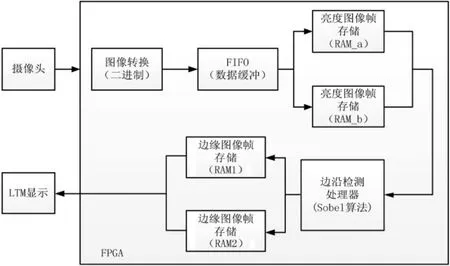

系统基于Altera公司的Cyclone IV系列FPGA,采用从顶向下模块化设计方法,利用攀岩法建模,具有良好的移植性和系统扩展性。图2为边缘检测实时处理图。

图2 边缘检测实时处理系统

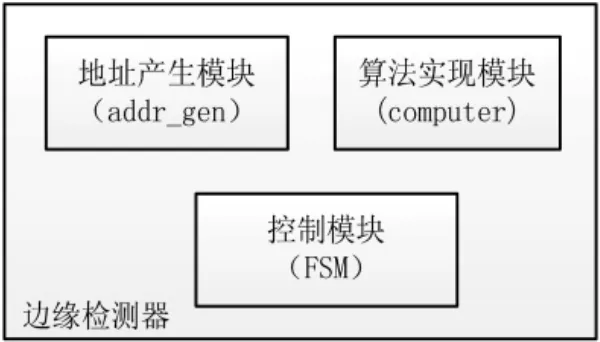

图3为硬件加速器模块设计图。设计中将系统数据流和控制流分开进行,这样在设计数据流时就不必在意数据何时输入何时输出的问题,而把这些问题转移到控制流设计阶段中去。在控制流设计阶段系统地考虑数据流的控制,将使得电路设计更加系统,修改更加方便。控制流的设计一般借助于状态机(FSM)。

图3 硬件加速器模块设计

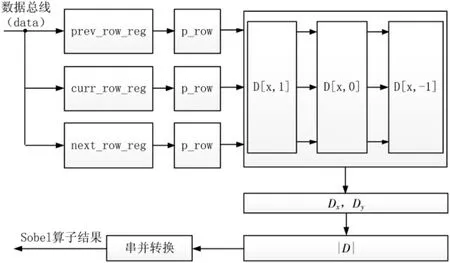

以实现分辨率600×400的8 bit灰度图片为例,系统设计数据总线位宽 32 bit,通过总线分时复用,分别从memory取数据,放置32 bit*_row_reg寄存器,为减少产生无效数据,增加硬件设计的复杂性,等待数据分别装满*_row_reg寄存器,才开始移位计算Sobel算子结果,这就造成移位时不能写入数据,写入数据时不能移位,产生大量的等待时间。本文通过插入*_row移位寄存器,把写数据和移位分开处理,实现系统的全线流水。

对于Sobel算法单元,为了节约资源和提高处理速度,有些设计采用分布式算法,利用查找表代替乘法器进行乘法运算[5],这样无法做到对任意随机数据的处理。本文为避免使用乘法器,通过移位实现乘法运算。数据流水进入产生的无效数据设置为左边界,数据流水排除的无效数据设置为右边界,顶行和末行为无效行设置上下边界。图4为Sobel算法架构图。

3 系统仿真和结果分析

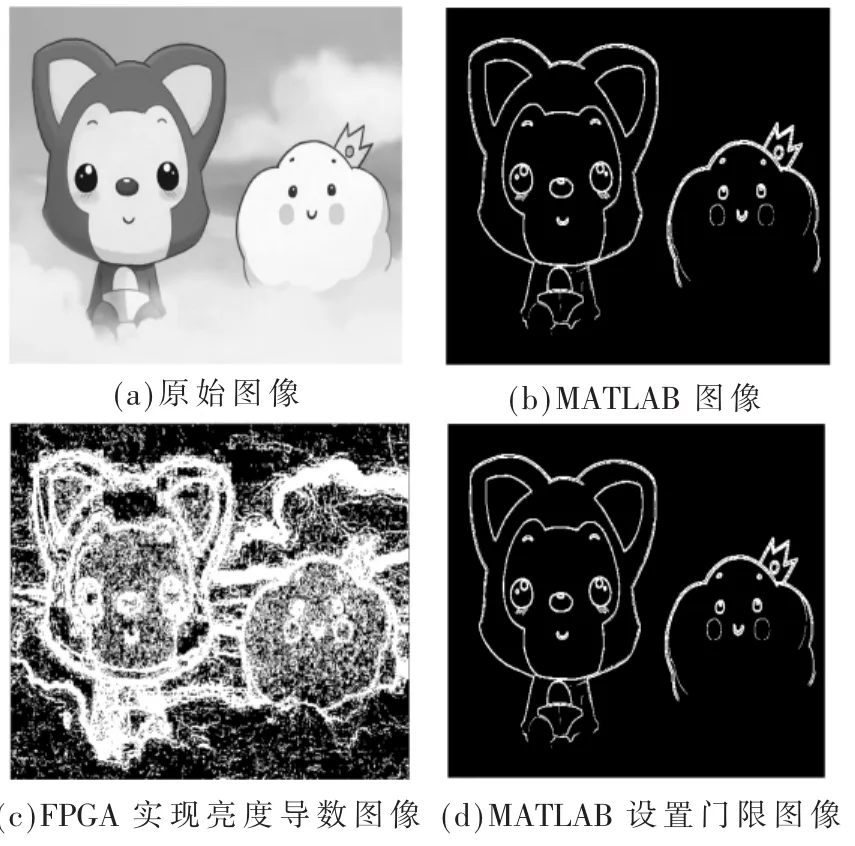

本文采用600×400的灰度图像作为研究对象,仿真和验证结果如图5所示。

通过MATLAB将灰度图片imag1.bmp(任意格式)处理转换成 imag.txt文件,存储在 Memory中,用 Verilog实现 Sobel算法,Modelsim仿真数据生成 data.txt文件,再利用MATLAB将data.txt文件通过门限处理转换成图片tes.bmp。用MATLAB直接调用Sobel函数处理初始灰度模式图片,生成图片imag2.bmp,比较两图片,验证FPGA处理的正确性。

图4 Sobel算法实现架构

从仿真结果和实验所得图像来看,该设计很好地完成了Sobel算法的边缘检测任务,使用RAM+FPGA加速器结构,以 50 MHz(实验仿真使用值)时钟驱动为例,处理一幅600×400图像,所需时间为19.2 ms,每秒可处理图像208幅,满足实时系统要求,解决单核处理器运算时间长的问题。解放控制单元去实现更复杂的控制和功能。

图5 仿真和验证结果

4 结论

本文基于FPGA引用硬件加速器思想,解决嵌入式软件无法满足信息的实时性处理问题,用 Verilog编程硬件实现图像数字信号读写、Sobel算法实现,完成图像边缘检测;通过 FPGA乒乓操作、并行处理和流水线设计完成数据量大、重复率高的图像边缘检测数据处理,大大提高了系统效率,达到了实时性要求。同时引用模块化的设计方法,自顶向下利用攀岩法建模,使得设计具有良好的可移植性和系统可扩展性,具有极大的实用价值。

[1]何俊峰.基于视觉原理的图像边缘检测算子研究[D].武汉:华中科技大学,2006.

[2]Yu Yuanhui,Chang Chinchen.A new edge detection approach based on image context analysis[J].SCI,Image and Vision Computing,2006,24:1090-1102.

[3]林伟,周剑扬.图像边缘检测高速数字滤波器设计与实现研究[J].现代电子技术,2006(6):26-29.

[4]吴海彬,何祖恩,李文锦.基于改进Sobel算子的图像边缘检测及其嵌入式实现[J].机床与液压,2009,37(10):133-136.

[5]叶敏,周文晖,顾伟康.基于 FPGA的实时图像滤波及边缘检测方法[J].传感技术学报,2007,20(3):623-627.

Image edge detection based on Sobel algorithm in FPGA implementation

Du Zhengcong1,Ning Longfei2

(1.Electrical Information Engineering College,Panzhihua University,Panzhihua 617000,China;2.School of Mechanical Engineering,Xihua University,Chengdu 610039,China)

Aiming at the problem that embedded software can′t meet the digital image real-time processing speed,this thesis puts forward the idea of using hardware accelerators,that is,using FPGA hardware to implement Sobel edge detection algorithm.Through Ping-pong operation,parallel processing data and pipeline design,the processing speed of the algorithm is greatly improved.The hardware design of module ensures the portability and scalability of the system.Finally,this thesis applies Verilog HDL programming to realize the algorithm processing and uses Modelsim and MATLAB to make simulation and verification.

FPGA;Sobel edge detection;hardware accelerators

TN911.73;TP391.7

A

10.16157/j.issn.0258-7998.2016.10.023

2016-04-14)

杜正聪(1975-),男,教授,博士,主要研究方向:信号与信息处理。

宁龙飞(1987-),男,硕士,主要研究方向:信号处理和图像边缘检测。

中文引用格式:杜正聪,宁龙飞.基于Sobel算法图像边缘检测的FPGA实现[J].电子技术应用,2016,42(10):89-91,95.

英文引用格式:Du Zhengcong,Ning Longfei.Image edge detection based on Sobel algorithm in FPGA implementation[J].Application of Electronic Technique,2016,42(10):89-91,95.