基于SystemVerilog语言的像素cache验证平台的实现*

2016-12-02韩俊刚李卯良

杨 铮,韩俊刚,李卯良,刘 欢

(1.西安邮电大学 计算机学院,陕西 西安710121;2.西安邮电大学 电子工程学院,陕西 西安710121)

基于SystemVerilog语言的像素cache验证平台的实现*

杨铮1,韩俊刚1,李卯良2,刘欢1

(1.西安邮电大学 计算机学院,陕西 西安710121;2.西安邮电大学 电子工程学院,陕西 西安710121)

以SystemVerilog为基础,对自主研发的GPU“萤火虫2号”中像素cache部分搭建可重用的验证平台。该平台可以自动完成整个验证过程,并将验证结果打印到Linux终端和文件当中,方便程序员检查验证结果。实验结果表明,该验证平台对像素cache的功能验证覆盖率可以达到 100%,并且具有良好的可重用性,能够全面、正确地完成RTL级功能验证,有效地提高了验证的效率和质量。

像素cache;验证平台;SystemVerilog;可重用性

0 引言

集成电路发展日新月异,已经由小规模集成电路阶段发展到了超大规模集成电路阶段,工艺水平也从130 nm到22 nm甚至到14 nm。三星集团最近宣布,将于今年年底实现超越14 nm,达到10 nm的制造工艺。这些进步会使芯片的处理能力更强,体积更小,功耗更低。但伴随着这些进步同时,也会使芯片的验证难度不断增大,验证的工作量也会更多。如今,验证的工作量已经占到了整个SOC研发的70%[1],因此提高验证的效率已经迫在眉睫。

传统的 Verilog验证方法是定向的,需要程序员设计大量的测试激励,然后对波形进行观察检测,这样的方法验证效率低、可重用性差,为此工业界推出了具有面向对象特性、支持约束随机与断言等功能的标准化硬件描述与验证语言SystemVerilog[2-3]。本文基于该语言实现了一种芯片系统功能验证平台,有效地完成了对芯片的RTL级功能验证,突破了传统的验证方法,有效地解决了传统验证方法对芯片验证的充分性不足和效率低下的问题[4]。

1 SystemVerilog语言

SystemVerilog语言吸收了 Verilog、VHDL、C++的概念,还包括验证平台语言和断言语言,也就是说,它将硬件描述语言(HDL)与现代的高层级验证语言(HVL)结合了起来[5]。正是因为这些优点,使得SystemVerilog语言在RTL验证流程上比传统方式具有更强大的表现能力,而且该语言集成了面向对象和线程间通信等的特点,使得该语言具有更强的灵活性,使程序员在设计验证平台时有更大的发挥空间。同样几个比较著名的验证方法还有如:UVM、OVM、VMM等,本文主要使用SystemVerilog语言来搭建一个可重用的验证平台对待测模块(Design Under Test,DUT)像素cache进行全面地验证。

2 SystemVerilog验证平台实现

2.1像素cache简介

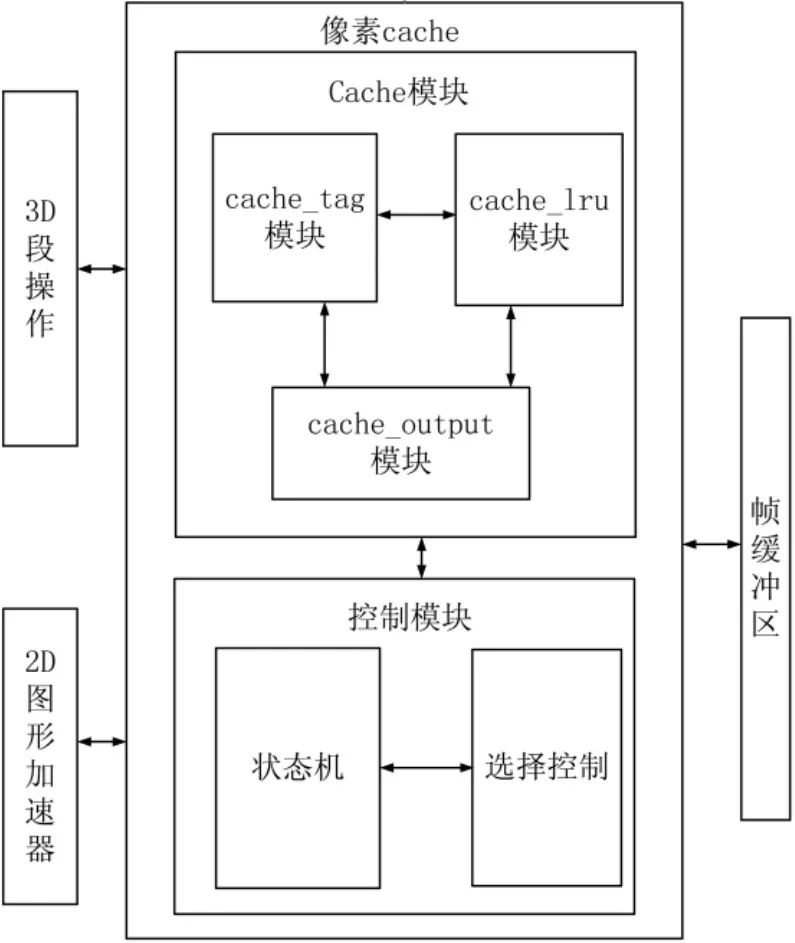

像素cache是GPU中的重要组成部分,这个模块的算法是否正确和功能是否全面直接关系到GPU处理图像的正确性及快慢与否。因此,该模块的功能验证和覆盖率验证就显得至关重要。本文的像素cache模块在我校工程中心自主研发的GPU“萤火虫2号”中连接着像素处理单元(FOP)以及像素RAM两个模块,目的是保证两者之间能够快速准确地传输数据和指令。像素cache模块架构如图1所示。

图1 像素cache的架构

该像素cache包含2个模块,分别是cache模块和控制模块。

2.2cache模块

cache模块包含 3个模块,cache_tag模块、cache_output模块和cache_lru模块,它们分别完成了cache地址选择、输出和算法实现的功能。

2.2.1cache_tag模块

该模块主要实现的功能就是地址运算,将接收到的地址和cache内部存储的地址进行比较来判断是否命中。

2.2.2cache_lru模块

该模块主要实现了整个cache的核心内容,实现了cache的替换算法。本文中的像素cache采用的是最近最少使用的替换算法。

2.2.3cache_output模块

这个模块主要功能就是根据 cache_lru模块输出的控制条件,将cache_ram中的数据输出。这部分控制条件包括2D刷新、读命中、读未命中、写命中和写未命中等。

2.3控制模块

控制模块包含有一个状态机模块和一个选择模块。

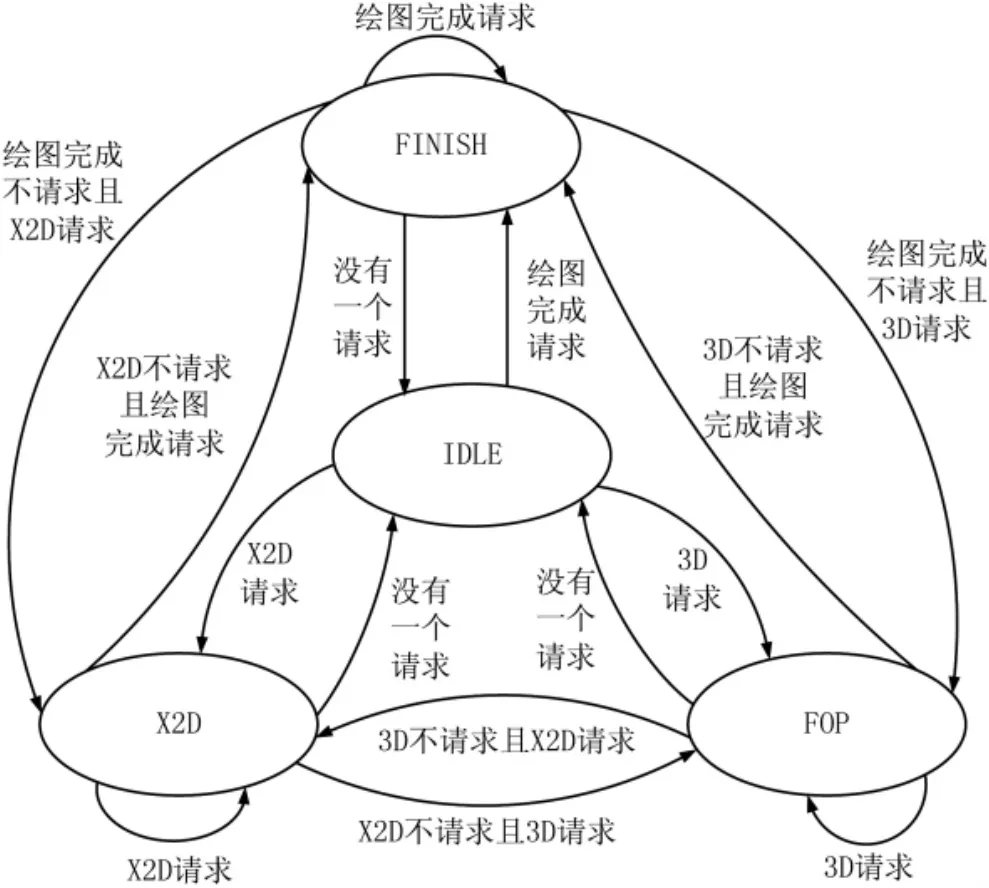

2.3.1状态机模块

状态机完成了处理各个请求的状态跳转,该模块将整个像素cache操作划分为如图2的4个状态,这4个状态分别完成了初始化、2D图形处理加速状态、3D段操作状态和结束状态。

图2 像素cache的控制状态机

2.3.2选择模块

该模块根据状态机跳转输出的选择信号选择3D段操作或者 2D图形加速并且把相应的信号传递给 cache模块,然后进行相应的处理。

2.4像素cache验证平台设计

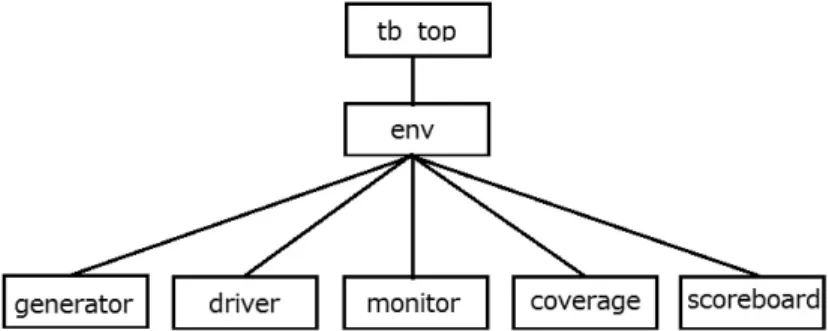

本文设计的验证平台架构图如图3所示。

图3 SV验证平台设计框架

该平台主要包括了顶层模块和一些功能模块。其中tb_top模块是顶层模块,也是整个验证平台的入口,该模块实例化了 env模块和interface模块;env模块是环境模块,该模块实例化了generator、driver、monitor等的功能模块,这些功能模块在env模块中分别完成自己的任务;interface模块是接口模块,该模块定义了整个像素 cache模块验证环境中需要控制和验证的接口;generator模块是整个验证环境中测试激励的产生器,该模块会根据需求产生包括 2D操作、3D操作、写读写、写读等激励,并且将激励以邮箱的方式传送给其他模块;driver模块是驱动模块,该模块接收 generator模块传来的激励,然后根据像素 cache的时序处理这些接口信号;monitor模块是监视器模块,该模块会监视整个验证过程中的信号,如数据、地址、功能,包括像素 cache模块中间产生的信号,并将监视到的有用信号以邮箱的方式传送给其他模块;scoreboard模块是计分板,该模块接收monitor模块传来的有用数据,并根据需求把结果打印到终端和文件中,以供程序员对比检查,如果出现错误,该模块会打印出问题所在位置和时间,并中断整个验证流程;coverage模块是覆盖率模块,该模块接收每一次激励信号,并分析该激励属于哪一类测试,最终统计所有结果,计算出整个验证过程中的功能覆盖率和数据的覆盖率并打印到终端和文件中,以供程序员对比检查。

2.5验证过程和预期目标

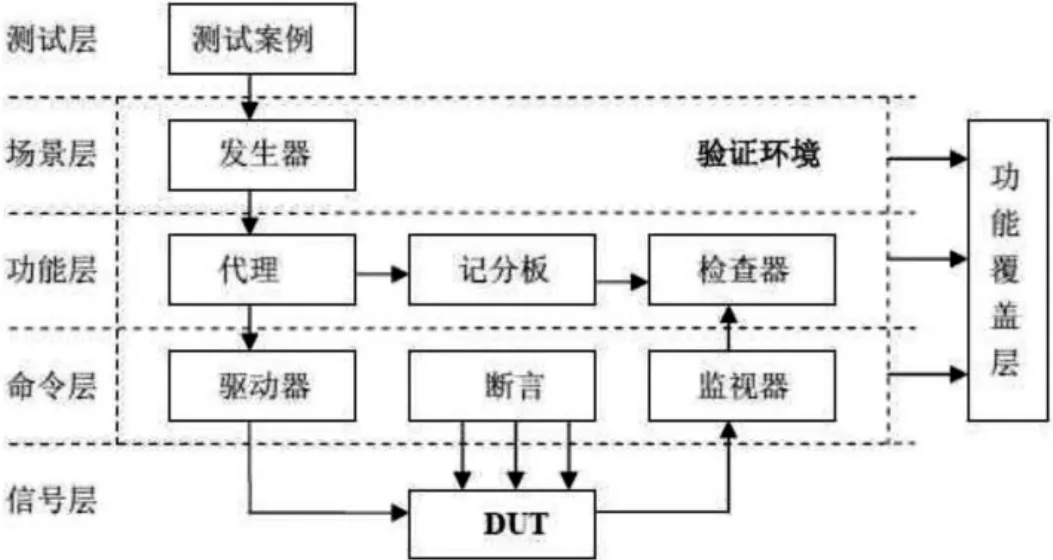

整个验证平台和DUT以如图4[6]方式进行搭建。

图4 DUT与验证环境平台

首先根据DUT模块的功能和反馈信号,将DUT输入分为如下几类:2D图形加速的写、写后读、写后写后读、读、读后读、读后写后读;3D段操作的写、写后读、写后写后读、读、读后读、读后写后读等输入信号。然后将输入数据128位和地址32位进行随机产生,最终目标要保证功能覆盖率达到100%,并且数据和地址能够正确无误地进行传输。

3 结果分析

3.1输出报告

经过随机产生的100 000组测试激励,在VCS终端会打印出执行报告,随机挑出一条报告进行分析,如图5。

图5 随机抽取的一条报告

图中第200次随机验证中 Driver读取 generator产生的随机激励成功,并分析该次随机验证的分类。分别经过driver,scoreboard,monitor模块操作,最终分析得出,该次随机验证属于3D端操作中的读类型,读的数据为如图5中的128位的值,地址为32’h675745fd。本次随机验证时间从99330000ps开始到99790000ps结束,数据和地址均与预期结果一直,传输结果正确。

整个验证过程产生的报告如图6所示。

图6 验证结果报告

根据图6中报告可知,经过100 000次随机激励与测试,所得的结果满足预期要求,能够完全覆盖2D图形加速和3D段操作中的所有8种预期情况,功能覆盖率达到 100%;数据和地址也是随机产生,经过 100 000次的随机化产生激励,数据和地址基本达到全面覆盖。

3.2波形图

图7是使用DVE工具产生的部分验证波形,从波形中可以看出,每个验证激励均为随机产生,并且结果与预期的一致,没有出现错误。

图7 验证结果波形图

4 总结

本文基于SV语言搭建了一个能够全面验证像素cahce的平台,并且详细地介绍了该平台各个模块及架构。随后利用VCS软件对像素cache进行了全面验证测试。实验结果表明,该平台针对像素cache模块实现了功能上全面覆盖,能够准确地检测出像素 cache模块中出错的地方,并且及时报错,从覆盖率和正确性上均达到了预期目标。由于本文设计的验证平台与待测模块在架构上是独立的,所以该平台具有很好的可重用性,只需对部分模块进行修改便可以用于验证其他同类型的待测模块。

[1]山蕊,蒋林,李涛.基于SystemVerilog的可重用验证平台[J].电子技术应用,2013,39(5):128-131.

[2]王鹏,刘万和,刘锐,等.基于 SystemVerilog可重用测试平台的实现[J].电子技术应用,2015,41(2):61-64.

[3]P-IEEE.Standard for SystemVerilog-Unified hardware design,Specification,and verification language[J].Copyright 2009:isbn,2009:1-1285.

[4]黄凤英.基于 SV语言的 RFID标签芯片数字系统验证平台设计[J].中国集成电路,2016,25(3):30-34.

[5]SPEAR C.Systemverilog for verification[M].SystemVerilog for Verification.2012:253-266.

[6](美)克里斯·斯皮尔.SystemVerilog验证[M].北京:科学出版社,2009.

Implementations of the pixel cache validation platform based on SystemVerilog language

Yang Zheng1,Han Jungang1,Li Maoliang2,Liu Huan1

(1.School of Computer Science,Xi′an University of Posts&Telecommunications,Xi′an 710121,China;2.School of Electronic Engineering,Xi′an University of Posts&Telecommunications,Xi′an 710121,China)

Based on SystemVerilog,build a reusable verification platform for GPU"Firefly 2nd"pixel cache which is the independent research and development of school.The platform can automatically complete the verification process,and print the results to a Linux terminal and file to facilitate the programmer checks to verify the results.Experimental results show that the functional verification coverage verification platform for pixel cache can be 100%and have good reusable,fully and correctly complete RTL-level verification,and effectively improve the efficiency of the verification and quality.

pixel cache;verification platform;SystemVerilog;reusable

TP302.1

A

10.16157/j.issn.0258-7998.2016.10.012

国家自然科学基金重点资助项目(61136002);教育部科学研究计划重点资助项目(2111180)

2016-05-12)

杨铮(1990-),男,硕士研究生,主要研究方向:软件工程。

韩俊刚(1943-),男,教授,主要研究方向:软件和硬件形式化验证、图形处理器和计算机体系结构。

中文引用格式:杨铮,韩俊刚,李卯良,等.基于 SystemVerilog语言的像素cache验证平台的实现[J].电子技术应用,2016,42 (10):51-53,61.

英文引用格式:Yang Zheng,Han Jungang,Li Maoliang,et al.Implementations of the pixel cache validation platform based on SystemVerilog language[J].Application of Electronic Technique,2016,42(10):51-53,61.