基于软硬件协同技术的AHB-PCI测试平台*

2016-12-02韩俊刚李卯良史少旭

刘 欢,韩俊刚,李卯良,杨 铮,李 明,史少旭

(1.西安邮电大学 计算机学院,陕西 西安 710121;2.西安邮电大学 电子工程学院,陕西 西安 710121)

基于软硬件协同技术的AHB-PCI测试平台*

刘欢1,韩俊刚1,李卯良2,杨铮1,李明2,史少旭2

(1.西安邮电大学 计算机学院,陕西 西安 710121;2.西安邮电大学 电子工程学院,陕西 西安 710121)

针对AHB-PCI的桥接电路,搭建了一个测试其功能的平台。该平台主要由软件和硬件协同完成。硬件部分实现了两个符合AHB标准的RAM,一个作为主机,能够请求总线;另一个作为从机,可以接收数据。软件方面通过驱动程序对PCI部分进行相应配置和读写。通过实际测试比较,使用该方法搭建的平台比在modelsim上的仿真验证平台在正确性验证上更有保障。

AHB;PCI;软硬协同;验证平台

0 引言

半个世纪以来,集成电路设计规模和设计复杂度不断增加[1]。在这个过程中,集成电路片上设计对总线的要求也在不断地提高。目前计算机中采用较多的总线标准有AMBA总线、ISA总线、SPI总线、PCI总线等。其中PCI总线作为一种系统总线在计算机上得到广泛应用[2],而AMBA总线由于其高性能、高带宽的特点在片内总线市场占有率最高,成为一种最流行的工业标准片内总线结构[3]。

AMBA Rev2.0规范中包含两级总线[4]:AHB(Advanced High Performance Bus)系统总线和 APB(Advanced Peripheral Bus)外围总线。其中,AHB总线采用地址/数据分离的流水式操作,支持突发传送,分裂事务传送特性和多个主设备的总线管理,具有高带宽、高性能特性,适合于嵌入式处理器与高性能外围设备,片内存储器及接口功能单元的连接[5]。

PCI总线之所以成为局部总线的主流[6],是由一些显著特点决定的,如运行速度快、可扩展性好、兼容性好、稳定可靠等特点。

本文利用软硬件协同的技术,搭建了一个对AHBPCI[7]桥功能验证的平台。与常用的 Verilog验证相比,本文中的方法更能保证硬件的正确性,减少了从仿真到综合中由于综合工具优化导致功能验证的不一致性,同时节约了开发周期。

1 AHB-PCI桥的结构

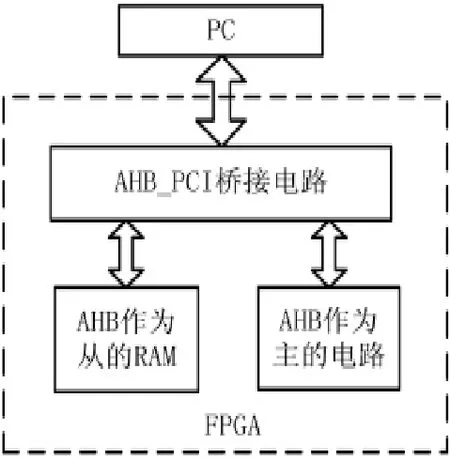

AHB-PCI桥实现AHB到PCI的协议转换。主要包括两部分,即AHB一端作为主机,完成AHB到PCI的信号转换;另一个PCI一端作为主机,能够实现PCI相关寄存器的配置和数据的传输。两个模块均需要进行时钟的同步。拓扑结构如图1所示。

图1 AHB-PCI桥拓扑结构

图中最大矩形方框为AHB_PCI桥转换电路的顶。它由模块I和模块II两个模块构成。当有一个AHB主设备 (例如图形处理器 )启动一个事务时 ,其目标为一个挂接在PCI总线上的从设备,则模块 I负责相应的协议转换和数据缓冲,并在PCI总线上启动一个适当的事务。而当有一个PCI主设备启动一个事务时 ,其目标为一个挂接在AHB总线上的从设备(例如片上存储器),模块II负责相应的协议转换和数据缓冲,并在AHB总线上启动一个适当的事务。

2 基于FPGA的软硬件协同的测试平台

2.1测试平台概述

本文所完成的测试平台主要目的是对AHB-PCI桥的功能进行测试,并确保符合标准的协议。系统上电后,通过软件对PCI相应寄存器进行配置,然后对AHB作为从设备进行读写操作,最后启动AHB作为主设备,对PCI作为从的一端进行读写。通过这样不断地操作,完成对桥的功能验证。平台使用操作系统版本Red Hat2.16.0,vivado版本 15.4,FPGA为 Xllinx的 7vx690tffg1930-1,带有PCI插槽的主机。

2.2基于FPGA的测试平台设计与实现

2.2.1测试平台的结构

基于FPGA的测试平台所实现的所有测试电路必须可综合。测试平台主要由软件和硬件两部分构成。软件部分主要实现对PCI一端通过驱动程序进行驱动,实现PCI主从的时序,硬件部分主要由两个符合AHB标准的RAM构成。平台硬件结构如图2所示。

2.2.2测试软件设计

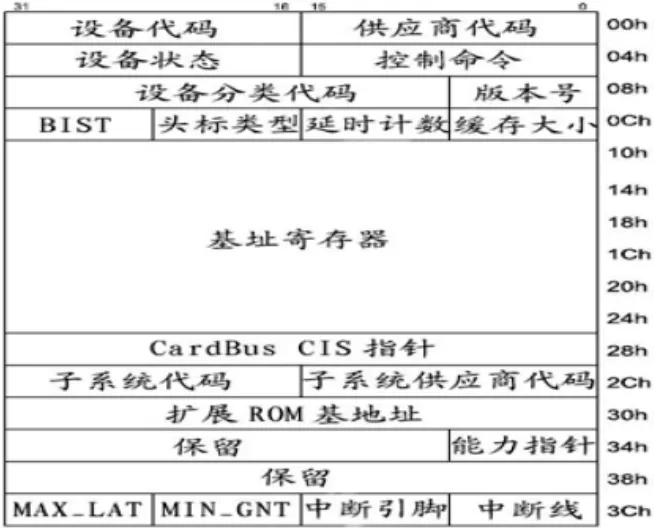

在系统中所有的PCI设备,包括PCI-PCI桥接器在内,都有一个需要配置的数据结构,它通常位于 PCI配置地址空间中。PCI的配置头是用于系统标识与控制设备。配置头在PCI配置空间的位置取决于系统中PCI设备的拓扑结构。例如将一个PCI网卡插入不同的PCI插槽,虽然其配置头的位置会变化,但是对整个系统没影响,系统将找到挂接在其上的每个 PCI设备与桥接器,并使用配置头中的信息来配置寄存器。如图3所示为普通PCI的配置寄存器分布。

图2 基于FPGA的测试平台结构

图3 普通PCI配置头标区

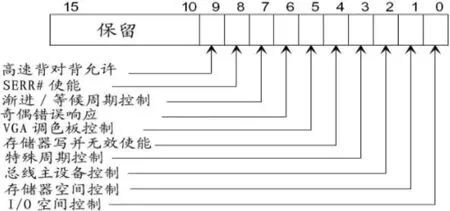

命令寄存器是一个必备的寄存器,该寄存器可读/写,格式如图4所示。根据使用中的需要将该寄存器利用驱动程序配置为0x0246,bit 1写为1,存储器地址空间使能,接受以该设备为目标的存储器事务;bit 2写为1,总线主设备使能,允许该设备发出请求,占用总线;bit 6奇偶校验使能;bit 10写为0,中断使能,允许产生INTX的中断消息。

图4 命令寄存器

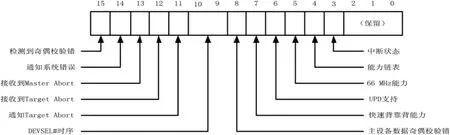

状态寄存器为只读寄存器,记录PCI总线有关的状态信息,格式如图5所示。

在一般 PCI设备中,除了拥有配置空间外,还具有两个物理空间:memory空间和I/O空间。想要访问这两个地址空间,就必须使用配置空间中的基址寄存器。一般PCI设备或桥中涉及3种基址寄存器:内存空间基址寄存器、I/O空间基址寄存器和扩展ROM基址寄存器。

Linux内核提供了3种数据结构来描述PCI控制器、PCI设备以及PCI总线。其中PCI控制器用pci_controller结构来描述,PCI总线用 pci_bus结构来描述,PCI设备用pci_dev结构来描述。PC对PCI进行初始化流程如下:

图5 状态寄存器

(1)Linux分配数据结构pci_contoller,并且初始化,包括 PCI的 memory/io空间和访问 PCI配置空间所需的handler。

(2)PCI设备的枚举:扫描系统上所有PCI设备,包括PCI桥,并初始化它们的配置空间(硬件上的初始化)。

(3)用数据结构将PCI设备信息联系起来,在系统中构建PCI树(软件上的初始化)。

(4)加载PCI设备的驱动程序。

驱动程序通过读取和配置相应的寄存器,对PCI进行配置操作和对memory/io空间的访问。

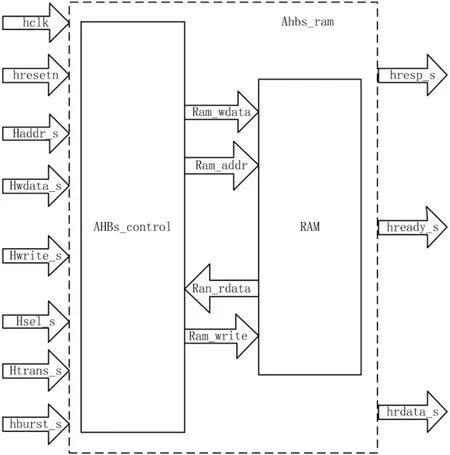

2.2.3AHB作从RAM的硬件电路设计

AHB作为从的RAM由AHB控制部分和RAM部分构成。其中RAM由vivado的IP核生成。控制部分主要是根据AHB的时序生成RAM的读写时序并对桥做出相应的操作。结构如图6所示。

图6 ahbs_ram结构

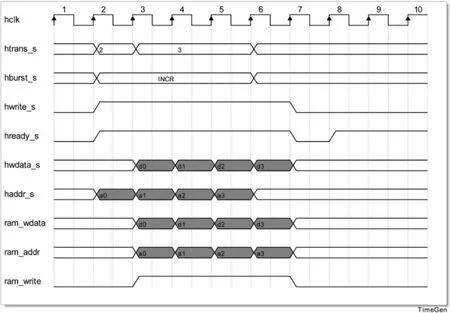

该RAM支持AHB的所有传输类型,接受的传输字大小为32 bit,即hsize_s为010b。写时序如图7所示,写时序以一个INCR的传输类型为例,写4个32 bit的数据。整个传输过程hwrite_s为高,表示桥对RAM进行写操作。开始传输时,主机会将htrans_s的信号置为 2,表示非连续传输,并且发送地址a0和传输类型hburst_s,如果hready_s为高即从机准备好,则将 htrans_s信号置为3,表示连续传输,并发送第二个地址a2和第一个地址对应的数据d1,此时RAM控制部分将地址a0发给ram_addr,并将数据d0发给ram_wdata,ram_write置高,将数据写入 RAM,直到等到传输完成,所有信号置为默认状态。

图7 ahbs_ram写时序

如图8所示为读时序,读时序以一个INCR的传输为例,读取4个32 bit的数据。整个传输过程中hwrite_s为低,表示桥对RAM进行读操作。开始传输时,主机会将htrans_s的信号置为2,表示非连续传输,并且发送地址a0和传输类型 hburst_s,如果hready_s为高即从机准备好,则将 htrans_s信号置为 3,表示连续传输,否则信号持续直到 hready_s拉高,从机准备好接受第一个地址,控制部分将地址传送给 ram_addr,RAM一拍后出数据,将数据传给hrdata_s,如此往复,直到传输完成,所有信号置为默认状态。

图8 ahbs_ram读时序

控制部分内部实现了一个同步的FIFO。该 FIFO的主要功能是统计AHB作为从进行的读写次数,将这个计数器的值发送给AHB作为主的硬件电路,这样方便软件对作主电路的控制。

2.2.4AHB作主RAM的硬件电路设计

AHB作主的硬件电路主要由AHB作为主的控制部分和RAM部分构成。这部分的RAM是由vivado的IP核生成,保证存储数据的正确性。控制部分生成AHB需要的时序和RAM的读写时序。

用状态机实现生成AHB作主的时序,如图9所示。初始状态为IDLE,当 AHB作为从的计数器由9变为10的时候,触发一个上升沿,此时发送请求占用总线信号hbusreq_m,等到桥接电路回馈一个授权信号hgrant_m和从机准备好传输信号 hready_m,则将状态转到TRANS_ NONSEQ,并将本次传输数据的计数器置零,否则维持本状态。当状态机处于TRANS_NONSEQ时,会判断传输数据的计数器和本次要传输的数据是否相等,如果相等则进入状态TRANS_END,否则进入状态TRANS_SEQ。在TRANS_SEQ的状态时,处理办法和在状态TRANS_NONSEQ相同。状态TRANS_END完成本次传输,状态机进入初始状态。

图9 AHB做主的状态机

该部分硬件能够实现AHB传输类型中比较常用的几种传输方式,单一传输(single)、增量传输(INCR)、4个数据增量传输(INCR4)、8个数据增量传输(INCR8)、16个数据的增量传输(INCR16)。每次传输的开始由ahbs_ram中的计数器进行控制,即用软件操作作从的读写数据,来启动AHB作主的电路。

3 测试结果与分析

利用该平台在FPGA上对AHB-PCI桥进行验证,使用vivado15.4进行综合,添加Debug core对信号进行采样,生成bit,在FPGA上验证。实验进行了大量的测试,测试结果与预期的一致,下面对其中的一部分进行介绍。

(1)PCI的写操作:软件由驱动发出对 PCI进行写操作,从测试波形可以看出,所采的地址和数据与软件发出的一致,从而测试了桥PCI到AHB的写通路正确。

(2)PCI的读操作:软件由驱动对PCI进行读操作,从测试波形可以知道,软件所读出来的数据和开始写入的数据一致,从而测试了桥PCI到AHB的读通路正确。

(3)AHB的写操作:此处AHB的触发由 ahbs_ram中的计数器进行控制,所以利用软件写固定个数,触发了一次写操作,实验结果波形可以看出写操作的传输类型为INCR,传输了32个32 bit的数据。利用软件读取该部分存储的值,和硬件写入的值一致,从而测试了桥AHB到PCI的写通路正确。

(4)AHB的读操作:同写操作一样,软件做相应的操作,触发一次读操作,实验结果波形可以看出来,本次读操作的传输类型为INCR,读取了32个 32 bit的数据,利用软件写入的数据和波形上读取的数据一致,从而测试了桥AHB到PCI的读通路正确。

4 总结

本文运用软件与硬件相结合的技术搭建的测试平台对AHB-PCI桥进行了功能验证。该平台相对于modelsim搭建的测试平台在硬件的验证中更有说服力,利用FPGA对功能验证,极大地保证了硬件的正确性,节约了开发时间。平台运用软硬件协同技术,对于同类的硬件测试具有非常大的借鉴意义。

本文的方法可以测试硬件的基本功能和硬件的正确性,而未能将硬件功能测试完全,可利用 System Verilog搭建平台解决这个问题。

[1]詹文法,李丽,程作仁,等.一种基于总线的可重用验证平台研究[J].电子技术应用,2006,32(5):92-96.

[2]史茂森,邵翠萍,龚龙庆.一种 PCI总线 Master模块接口设计[J].计算机技术与发展,2012,22(7):207-210.

[3]颜伟成,陈朝阳,沈绪榜.AMBA-AHB总线接口的设计与实现[J].计算机与数字工程,2005,33(10):130-136.

[4]AMBA(tm)Specification.Revision 2.0.May,1999.http://www.arm.com/.

[5]王晨旭,桑胜田,王进祥,等.AHB-PCI桥的设计及其验证方法[J].微处理机,2004,2(1):8-13.

[6]李鉴.PCI系列总线及其应用[J].现代电子技术,2002,135(2):76-79.

[7]PRASHANT D,PITHADIYA N,VAIBHAV C,et al.Designing PCI/AHB bridge[J].International Journal for Scientific Research&Development,2013,1(2):388-390.

Built AHB-PCI test platform based on hardware/software codesign

Liu Huan1,Han Jungang1,Li Maoliang2,Yang Zheng1,Li Ming2,Shi Shaoxu2

(1.School of Computer Science,Xi′an University of Posts and Telecommunications,Xi′an 710121,China;2.School of Electronic Engineering,Xi′an University of Posts and Telecommunications,Xi′an 710121,China)

According to AHB-PCI bridge circuits,builted a platform to test its functionality.The platform was based on hardware/software codesign.Hardware consists of two-AHB standard RAM,one as the master to request bus,another as the slave to

ata.Software through the driver to configure the PCI,read and write.Through testing,platform was builted using this method of simulation platform than on the modelsim more secure in the verification correct.

AHB;PCI;hardware/software codesign;verification platform

TP302

A

10.16157/j.issn.0258-7998.2016.10.009

国家自然科学基金重点资助项目(61136002);教育部科学研究计划重点资助项目(2111180)

2016-05-10)

刘欢(1991-),男,硕士研究生,主要研究方向:计算机系统结构。

韩俊刚(1943-),男,教授,主要研究方向:软件和硬件的形式化验证、图形处理器和新型计算机体系结构。

中文引用格式:刘欢,韩俊刚,李卯良,等.基于软硬件协同技术的 AHB-PCI测试平台[J].电子技术应用,2016,42 (10):40-43.

英文引用格式:Liu Huan,Han Jungang,Li Maoliang,et al.Built AHB-PCI test platform based on hardware/software codesign[J].Application of Electronic Technique,2016,42(10):40-43.