大动态大带宽数字接收机设计实现*

2016-12-01何勤

何 勤

(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

大动态大带宽数字接收机设计实现*

何 勤

(中国电子科技集团公司第三十八研究所,安徽 合肥 230088)

大动态数字接收机是机场场面监视雷达的重要组成部分。论证了大动态、大带宽系统参数的选取,数字滤波器的MATLAB仿真设计,采用16位模数转换器,大容量FPGA构建数字接收机平台,解决了大动态、大带宽采样及其数字下变频处理问题,并高速光纤传输数据,给出设计分析及测试结果,该结果表明, 信噪比满足系统动态范围的要求。该电路相对于模拟接收机有较高的性能,为现代雷达提供了一种高性能的数字接收机的解决方案,具有广泛的应用前景。

场面监视雷达;数字下变频;FPGA;数字滤波器

0 引言

机场SMR是一种监视机场场面目标状态的微波监视装备,能够检测机场场面区域内所有目标。它作为民航机场提高机场运行效率的重要保障设施,全面覆盖机场场面区域。据国际民航组织ICAO相关标准,机场SMR不仅具有检测机场活动区域(跑道和滑行道)运动、静止目标的能力,还需具有一定的非活动区域目标监视能力。它具有较高距离和方位分辨率,所以机场SMR采用大带宽信号和大水平尺寸的天线来实现距离和方位高分辨率,必然要求接收机具有大的动态范围以保证对各类目标回波的可靠处理检测。作为接收系统的后端数字接收机部分主要完成对模拟回波信号进行模数变换,并数字下变频到基带成IQ正交信号再实时传输给信号处理,因此数字接收机也要与接收通道匹配,满足大动态、大带宽的要求,本设计作为项目需求而专门设计的一款数字接收机电路。

1 设计思路

数字接收机采用直接中频采样加数字I、Q分离的A/D变换技术。与传统的模拟I/Q正交鉴相解调相比,中频采样具有很高的幅度平衡性和相位正交性,从频域分析,对输入回波镜像信号的抑制度可以做得很高,同时可以避免模拟解调中不可根本解决的直流温漂。直接中频采样的实现方式中具有数字内插和数字混频滤波两种方式。数字内插难以达到较高的镜像抑制度,本系统中采用模数转换A/D加数字滤波的方式来实现。

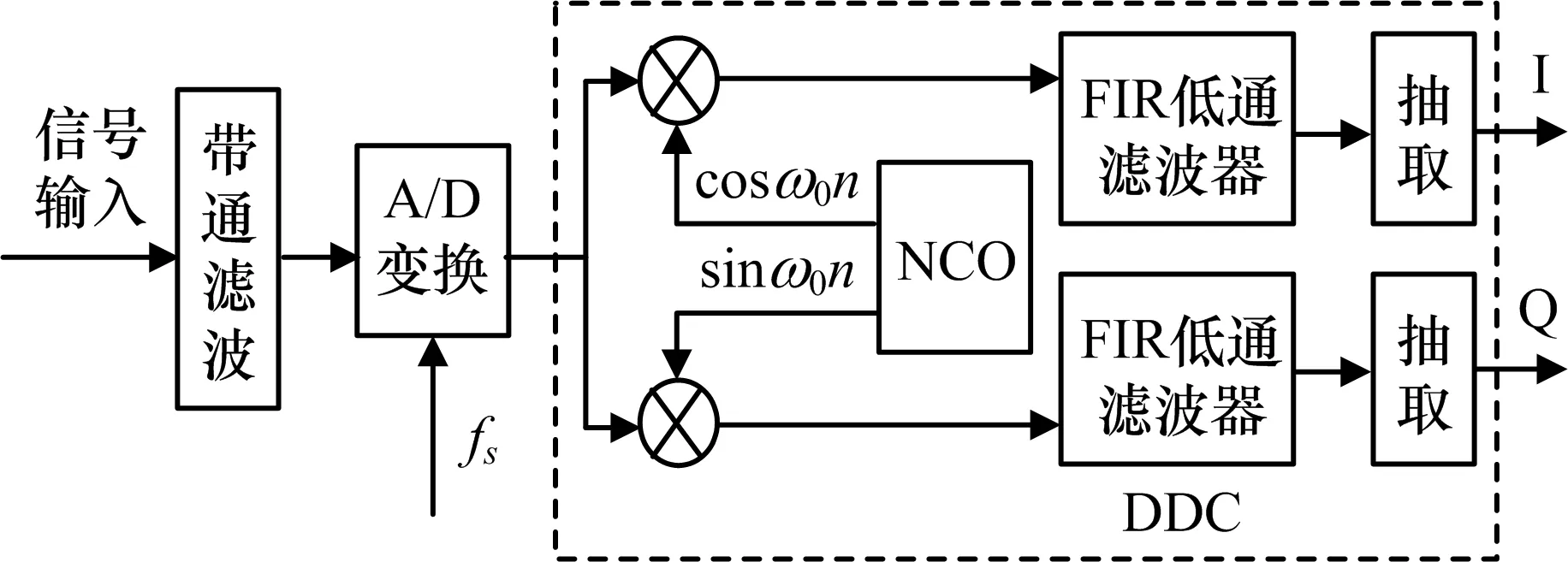

该数字接收机模块(单路)的原理框图如图1所示。模块组成主要包括大动态模数转换器A/D和大容量FPGA。A/D采样后的数据作数字下变频,整个模块的数字下变频及其它数字化工作都在FPGA中实现。数字下变频包括数字本振(NCO)、数字混频、数字滤波器和抽取器。

图1 数字接收机组成框图

如图1所示,一般的数字接收机工作时,将接收通道经放大,滤波后的中频信号进行模数变换,进入FPGA,数字混频器产生正交的两路数字本振信号,与数字中频信号相乘后,进行数字滤波处理,这时的数字滤波器可以是积分梳状滤波器CIC,半带滤波器HB,有限冲击响应滤波器FIR,酌情考虑使用滤波器组合来完成数字滤波,滤波后根据电路需要降速抽取,抽取到所需的数据率,得到正交的基带IQ数据。滤波的目的是防止抽取降速可能发生混叠,数字滤波器多采用多相数字滤波器,可高效地同时完成滤波和抽取工作。基带IQ数据按要求进行数据融合,打包通过TTL接口或转换成光信号通过光接口传输出去。

2 系统工作参数论证分析

在雷达系统中,对于复杂的脉冲信号的有效带宽B,有效带宽越宽距离分辨力越好。实际应用中,机场SMR必须架高工作以克服机场固定物的遮蔽,则发射波束与地面有一夹角,该角为擦地角γ。实际地面距离分辨力ρre与径向(斜距)距离分辨力ρra及擦地角(的关系为:

(1)

式中,k为距离向加权系数,γ=9.9°

机场SMR系统要求地面距离分辨力优于3m,选取地面距离分辨力ρre=3m,取k=1.3,则径向距离分辨力为:

(2)

则系统带宽:

(3)

所以,选取系统的工作带宽为70MHz。

(4)

n取能满足fS≥2B的最大正整数,B=fH-fL,则用fS进行等间隔采样所得到的信号采样值能准确地确定原信号。信号中频可在各那奎斯特带内选取,依据信号带宽70MHz,根据式(4),在不发生混叠情况下可考虑选取中频120MHz,200MHz,…,由于信号中频频率越高,信号相对于采样时钟的孔径抖动效应越明显,采样后信噪比越低,因此选取信号中频为120MHz。

数字中频的动态范围主要取决于ADC的分辨率,采样率和系统噪声,系统噪声是固定的,采样率确定后,动态范围就看AD的分辨率了,通常情况ADC信噪比可由式表示:

(5)

式中,N是ADC位数;fs是采样频率;B是信号带宽。式中第三项是信噪比得益,本系统中当fs=160MHz,B=70MHz时,得益是0.6dB,得益不高,因此SNR取决于AD位数N,尽量选位数高的AD。目前既满足高的采样位数,又要满足大带宽采样的需求的,可用作数字中频接收机的AD位数,可选16-bit的AD,AD的量化噪声较小,因而理想状况下的信噪比较高,但实际系统的噪声要大于量化噪声功率。一般系统噪声占AD位数四位左右,这样SNR理论上有74dB左右,满足系统要求的大于接收机的线性动态65dB,能够与前端接收机匹配上。

3 电路器件参数设计

模数转换器件选用National公司的ADC16DV160,该器件是双通道16bit,最高160MSPS的模数转换器,满足系统中对分辨率和带宽的要求,具有DDR LVDS输出,是差分,流水线结构,又具有数字误码修正和在片采样保持电路,保证较大的采样带宽,上电自校准,独特的片内时钟稳定器保证最小的时钟抖动,确保芯片最佳的动态性能。AD芯片的输入是差分端口,差分接口能有效抗干扰,需要将模拟信号转换成差分形式,我们将信号输入设计成交流耦合,通过传输变压器转化成差分,从传输变压器的频率响应可以看出,变压器相当于一个带通滤波器,传输变压器具有较低的寄生电容,而设计中采用两级变压器级联,进一步减少初次级的寄生电容,减少了阻抗失配带来的性能下降。

大动态、高信噪比的采样,要求高质量的时钟,时钟抖动要小,设计中选取时钟管理芯片AD9516,该芯片包含低相噪锁相环路,具有多路,多接口模式输出,只要输入一个基本的20MHz时钟,即可锁定输出模块所要求的AD采样时钟,FPGA工作时钟,时序同步时钟,时钟抖动达一两百fsrms,确保了A/D数据转换的性能。

按照图1中流程,信号采样后,要经过数字下变频处理的数字混频,滤波,抽取,得到基带的正交IQ信号,数字下变频处理在FPGA中进行,为保证充足的硬件资源和处理速度,采用ALTERA公司的EP2SGX90系列芯片,该芯片具有大容量、大内存等特点,并具有光纤接口。FPGA的数字下变频用硬件描述语言Verilog编程实现,NCO产生正余弦样本和输入数据进行混频,输出IQ两路信号送至FIR滤波器分别进行抽取滤波,NCO,DDC程序设计可以使用IP核,IP核的生成,需要进行各项参数设置,其中数字滤波器的设置,可通过专门的软件设计产生,导入滤波器的系数文件,由于Quartus II软件设计的滤波器较粗略,所以使用MATLAB的滤波器工具设计和仿真。

4 数字滤波器设计

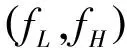

对于数字滤波器设计,由于带宽较大,而且采样率只有160MHZ,只两倍抽取,因此不可能采用CIC等多滤波器级联的形式,因而采用一级FIR滤波器。通过Matlab软件仿真,当要求达到65dB信噪比时,滤波器阶数至少要70阶,一般阶数越大,滤波效果越好,但相应的延时也越大,本雷达工作重频较高,因此延迟较大,会增加雷达工作开销,影响整机的工作效能,综合考虑滤波器阶数取为96阶。

选择等稳波滤波器,设计参数如下:通带35MHz,通带起伏0.1dB,阻带衰减75dB,滤波器的Matlab设计如图2所示:

图2 数字滤波器频响图

滤波后,进行两倍抽取,数据率降为80Msps。FIR滤波器采用固定系数模式,充分利用芯片内的乘法器,不过多耗用FPGA的逻辑单元,需乘法器(18bit×18bit)48个,I/Q两路加用作数字混频器的两个乘法器,共需98个片内乘法器。选用的FPGA是EP2SGX90有逻辑单元共90960个,总RAM存储位4520448bit,嵌入式乘法器(18bit×18bit)192个。

处理的数据要通过光纤传输,若按16bit,160MHZ时钟传输,IQ两路数据从一根光纤交替传输,传输的速率为:16×10/8×160=3200Mbps,所以选用一款4Gbps的多模双向光模块能够实现数据的传输。该光模块还可接收控制信号,控制数字接收机的工作状态、模式。

5 结果分析

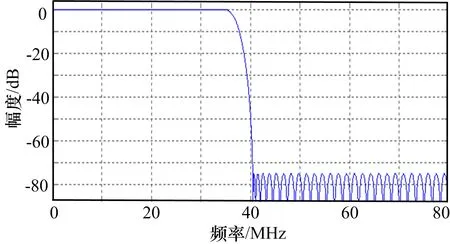

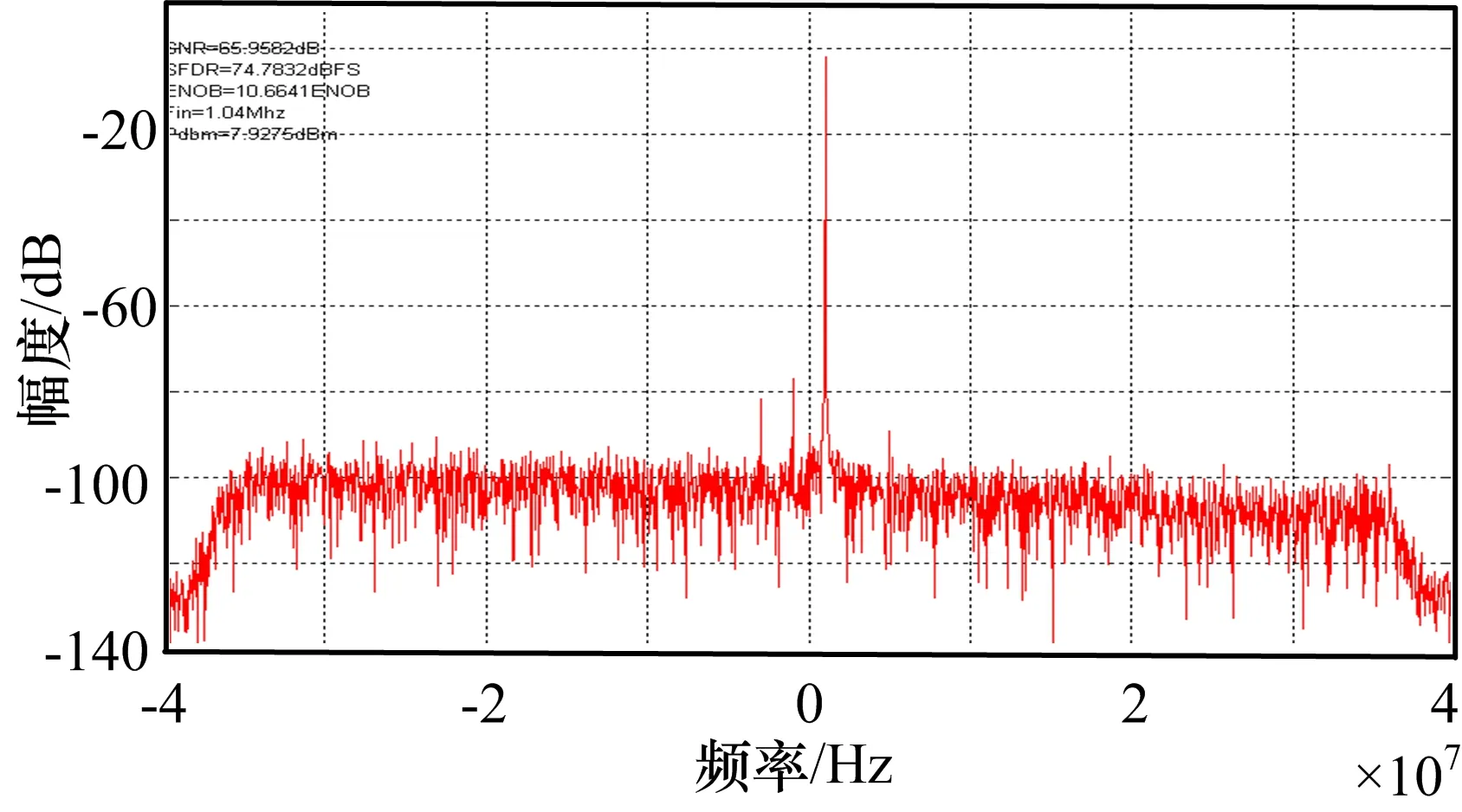

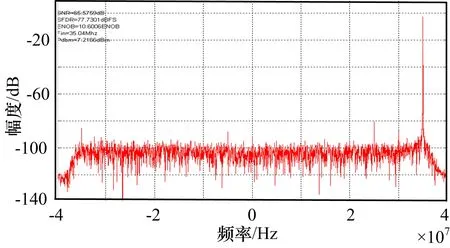

通过Quartus II软件,运行Signal Tap工具观测信号波形的状况,并导出经数字下变频处理后的IQ数据,用MATLAB软件作FFT分析信号质量。如图3、图4所示。

图3 单频121MHz,带宽70MHz,采样时钟160MHz频谱图

图4 单频155MHz,带宽70MHz,采样时钟160MHz频谱图

测试结果显示:当单频121MHz,带宽70MHz时,信噪比SNR为66dB,无杂散动态范围为74.8dBFS;当单频155MHz,带宽70MHz时,信噪比SNR为65.6dB,无杂散动态范围为77.7dBFS。带内起伏在1dB以内,该结果满足系统要求。

6 结束语

大动态数字接收机较好地解决了大动态和大带宽信号的采样及数字下变频处理的问题,性能稳定,配置灵活,已成功地运用于机场SMR系统中,为后续的机场SMR产业化工作提供了有力的技术保障。■

[1] James T.宽带数字接收机[M].北京:电子工业出版社,2002.

[2] 杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[3] 姜宇柏,游思晴,等.软件无线电原理与工程应用[M].北京:机械工业出版社,2007.

[4] 马晓岩,向家彬,等.雷达信号处理 [M].长沙:湖南科学技术出版社,1999.

[5] 王世一.数字信号处理(修订版)[M].北京:北京理工大学出版社,2004.

[6] Samir P. Verilog HDL数字设计与综合[M].北京:电子工业出版社,2004.

[7] Uwe MB.数字信号处理的FPGA实现[M].北京:清华大学出版社, 2003.

[8] 吴继华,王诚.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2005.

Design and implementation of wideband dynamic digital receiver

He Qin

(No.38 Research Institute of China Electronic Technology Corporation, Hefei 230088, Anhui, China)

The high dynamic digital receiver is the important component of Surface Movement Radar (SMR).The selection of high dynamic ,wideband radar system operating parameter are discussed. Simulation design of digital filter with MATLB software which uses 16-bit analog convertor and large capacity FPGA to resolve the problem of high dynamic, wide bandwidth range and digital down conversion. And the data transmission with high speed fiber gives the design analysis and measurement result that the SNR meets the requirement of dynamic range for the system. The module has higher performance than analog receiver, which provides the resolving scheme of high performance digital receiver for modern radar, and it has wide future application.

surface movement radar;digital down conversion;FPGA;digital filter

国家科技支撑计划(No.2011BAH24B05)

2016-07-04;2016-09-07修回。

何勤(1966-),男,高工,主要研究方向为雷达数字化接收机。

TN97

A