基于CBGA的多通道DDS封装隔离度设计

2016-11-30常登辉刘树凯何善亮

常登辉,刘树凯,田 浩,何善亮

(成都振芯科技股份有限公司,四川 成都610041)

基于CBGA的多通道DDS封装隔离度设计

常登辉,刘树凯,田浩,何善亮

(成都振芯科技股份有限公司,四川 成都610041)

介绍了一种基于陶瓷球栅阵列(CBGA)技术的多通道直接数字合成器(DDS)封装结构设计,提出了一种改进隔离度的CBGA基板实现形式,并利用 Ansoft HFSS软件进行了基板隔离度的优化仿真,最后对所提出的设计进行了实物测试。测试结果与仿真结果基本一致,表明所提出的封装优化设计成功地提高了多通道DDS的隔离度,为高隔离度的多通道DDS产品工程设计提供了参考。

通道隔离度;直接数字频率合成器;串扰;陶瓷球栅阵列

0 引言

在现代雷达系统中,直接数字频率合成器(Direct Digital Synthesizer,DDS)是实现雷达波形产生与发射波束控制最常用的方案之一。基于DDS技术的波形产生系统不仅可以方便地产生各种雷达波形,还可以在数字域灵活地对阵列天线进行相位和幅度加权,实现发射波束快速、高精度的控制,从而实现雷达波形产生、波形捷变与幅相控制的一体化设计[1]。

对于多通道DDS芯片而言,通道隔离度指标至关重要。当DDS通道隔离度较低时,通道间相互干扰较大,造成所生成的波形频谱纯度降低,甚至成为频谱中主要谐波点,因而大大影响了雷达系统的辨别能力和抗干扰能力。

目前国际与国内在多通道DDS方面的文献多集中在其杂散抑制方法的研究与探讨上[2-3],鲜有文献对其通道隔离度的提高和优化进行分析。本文从封装的角度出发,提出了一种应用于多通道DDS的CBGA封装设计,并对该封装的DDS通道隔离度的影响因素进行了分析,给出实际设计中的解决措施和仿真结果,最后通过对器件的实际测试验证了优化设计的有效性。测试结果表明,基于本文设计方法得到的4通道DDS产品的通道隔离度大于-65 dB,可满足雷达系统应用需求。

1 CBGA封装结构设计

随着集成电路封装的不断发展,封装类型越来越多,一般根据所需封装芯片的引脚数和性能确定具体的形式。本文提出的4通道DDS芯片由于有149个引脚而采用了CBGA的封装形式。该类型的封装具有气密性好、可靠性高及散热性能好的优点。图1为4通道DDS所设计的CBGA封装基板结构示意图。该封装结构主体由多层陶瓷基板制作而成,依照管壳厂商提供的设计规则,基板的叠层结构由上而下依次为键合指层、电源和地、信号、电源和地、电源、地。整个键合线引脚分布在同一个台阶上,可与半导体芯片所对应的引脚采用引线键合的方式实现电学连接。这样CBGA的封装结构由基板、陶瓷外壳、键合线及其它材料组成。

图2为利用Cadence SPB软件设计的CBGA基板布线示意图。其中关键信号走线的长度在5~7mm之间,加上键合线长度,走线的物理尺寸大于所对应工作波长的十分之一。接下来采用HFSS仿真设计方法,将图2中的模型通过 Ansoft Link软件导入到 HFSS中,对 CBGA基板设计进行优化。

图1 CBGA封装叠层图

图2 CBGA基板布线示意图

2 CBGA封装隔离度优化与设计

从封装的角度来说,串扰效应是导致多通道DDS隔离度变差的主要原因。串扰是指两条信号线通过之间互感和互容的耦合引起的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。在多通道DDS器件中,通道隔离度是串扰的一种特殊表现方式,是DDS输出端性能好坏的一个重要指标[4-6]。

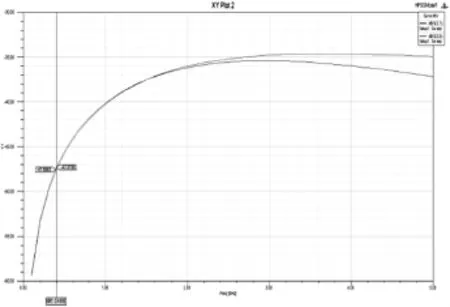

根据图3封装在HFSS中的模型,首先对BGA基板进行仿真,提取了8个端口的S参数[7]。多通道隔离度仿真结果如图4所示,S27为通道间的隔离度仿真结果,从图中可以看出,在频率400 MHz处隔离度为-47 dB,通道间的隔离效果较差,不能满足系统设计要求。

图3 输出通道的走线分布

图4 原始走线情况下的隔离度仿真结果

通过分析4个输出通道的基板走线,为了提高通道隔离度,采取了增大通道间距离和分割参考平面这两种优化方法。优化方法以及优化后的仿真结果与原始走线仿真结果对比如下文所述。

2.1增大通道间距离

为了减小串扰,提高通道隔离度,将通道OUT0和OUT1差分对间的一个焊球作为GND,这样两个差分对间的距离增大约1mm。另外为了减小信号回流路径,在差分信号过孔的两侧增加地回流过孔,地回流过孔的孔径与信号过孔孔径相同,优化后基板模型如图5所示。

图5 拉大通道间距离后的基板

仿真得到的隔离度结果如图6所示。可以看出,在400 MHz处,隔离度为-56 dB,与原走线相比,隔离度提高了9 dB,这是由于增大通道间的距离导致微带线间的互感系数降低,因此可以在一定程度上改善通道间的隔离度。

图6 拉大距离后的隔离度仿真结果

2.2分割参考平面

另一种通道隔离度改善的优化方式是将包裹信号层上下的地参考平面在两个通道之间分割开,优化后的模型如图7所示。

图7 参考平面分割后的基板

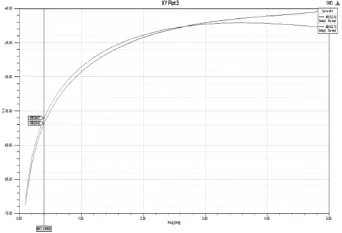

由于把包裹信号层的地参考平面分割开来能够缩短地回流路径,降低参考平面之间的耦合,因而隔离度得到了提高,仿真结果如图8所示。从图8中可以看出,隔离度有明显的改善,约为-72 dB,相对于增大通道间距离,隔离度提高了约16 dB。

图8 参考平面分割后的隔离度仿真结果

通过优化仿真对比发现,通道间的参考平面是影响通道间隔离度的主要因素,另外增大通道间距离和在通道间放置地回流孔对隔离度也有一定的改善。

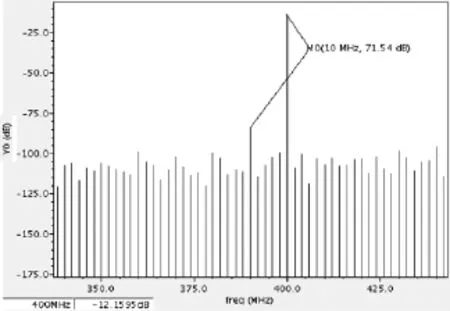

提取上述优化方式改进后的CBGA封装RLC等效电路,采用cadence ADE对带上封装寄生的多通道DDS芯片进行仿真,其通道隔离度仿真值约为-71.54 dB(如图9所示),与图8的仿真结果高度一致。

图9 通道隔离度仿真结果

3 实测结果

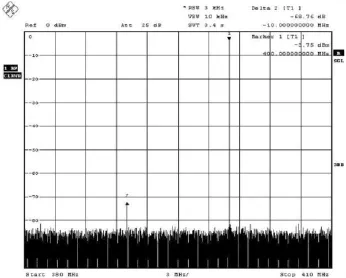

采用R&S公司的频谱分析仪FSW和信号源N5171B对该DDS芯片进行测量,测试平台如图10所示。通过配置控制字使通道OUT0输出400 MHz,通道OUT1输出390 MHz,测量通道OUT0中400 MHz信号和390 MHz的信号输出幅度,二者的差值即为通道隔离度。图11为通道隔离度的实测结果,隔离度约为-69 dB,实测结果和仿真结果基本一致,从而证实了基于CBGA技术的多通道DDS封装隔离度设计的有效性和实用性。

图10 测试平台

图11 通道隔离度测试结果

4 结论

本文提出了一种应用于多通道DDS的CBGA封装设计,并利用 Ansoft HFSS软件对多通道 DDS产品的CBGA封装进行了隔离度仿真,然后提出了优化方法并再次加以仿真验证,最后通过实测验证了所提出的优化设计及仿真方法的有效性,为高隔离度的多通道DDS产品工程设计提供了参考。

[1]张明友.数字阵列雷达和软件化雷达[M].北京:电子工业出版社,2008.

[2]何善亮,马骁,田浩,等.一种基于二次项逼近的DDS算法及其实现[J].电讯技术,2012(12):1946-1951.

[3]张熙,王晓峰,邵春晖.基于DDS技术的杂散分析及抑制方法[J].微计算机信息,2008(14):295-297.

[4]Eric Bogation.Signal and power Integrity-Simplified[M]. Prentice Hall PTR,2009.

[5]尹昌刚.PCB板级串扰仿真改善 ADC无杂散动态范围指标[C].ANSYS 2011中国用户大会优秀论文,2011.

[6]AD5379[EB/OL].http://www.analog.com/cn/products/digital-to-analog-converters/da-converters/ad5379.html.

[7]李明洋.HFSS电磁仿真设计应用详解[M].北京:人民邮电出版社,2010.

Design of multi-channels DDS packaging isolation based on CBGA

Chang Denghui,Liu Shukai,Tian Hao,He Shanliang

(Chengdu CORPRO Technology Co.,Ltd.,Chengdu 610041,China)

A CBGA(Ceramic Ball Grid Array)technology of multi-channels DDS(Direct Digital Synthesizer)packaging structure was introduced in this paper,proposed an improved isolation of the CBGA substrate form and used Ansoft HFSS software simulation to optimize the substrate before and after the isolation.The real test of the proposed design was carried out finally.The test results were in good accordance with simulation results,which show that the proposed optimization design can improve the isolation of multi-channel DDS and provide reference for the design of high-isolation DDS.

channel isolation;DDS;crosstalk;CBGA

TN402

A

10.16157/j.issn.0258-7998.2016.05.010

常登辉(1987-),通信作者,男,硕士,工程师,主要研究方向:模拟集成电路设计,E-mail:changdh2010@163.com。

刘树凯(1987-),男,硕士,工程师,主要研究方向:高速CMOS混合信号集成电路设计。

田浩(1981-),男,博士,高级工程师,主要研究方向:雷达信号处理及微电子集成电路抗幅照加固设计研究。

中文引用格式:常登辉,刘树凯,田浩,等.基于 CBGA的多通道 DDS封装隔离度设计[J].电子技术应用,2016,42 (5):36-38,41.

英文引用格式:Chang Denghui,Liu Shukai,Tian Hao,et al.Design of multi-channels DDS packaging isolation based on CBGA[J]. Application of Electronic Technique,2016,42(5):36-38,41.