基于FPGA的数字频率计设计

2016-11-25郭心伟刘小浩张国栋

余 果,郭心伟,刘小浩,张国栋,马 骁

(陕西师范大学 物理学与信息技术学院,陕西 西安 710119)

基于FPGA的数字频率计设计

余 果,郭心伟,刘小浩,张国栋,马 骁

(陕西师范大学 物理学与信息技术学院,陕西 西安 710119)

随着电子技术的发展,快速准确获得各种电子信号的频率显得越来越重要。但传统的频率计大多采用单元电路或单片机进行设计,存在测频范围窄,测量精度低,操作复杂和功能单一等问题。此数字频率计主要由AGC模块、整形模块、FPGA处理及显示模块组成,利用时钟脉冲计数的方式,实现正弦波和矩形波信号的频率、矩形波信号的占空比和输入的两路同频周期矩形波信号时间间隔的测量功能。该数字频率计测频范围宽,测量精度高,操作简单,稳定可靠。

数字频率计;时钟脉冲计数;FPGA;频率

数字频率计是计算机、通信设备和音视频等科研生产领域必不可少的测量仪器,它是一种用十进制数字来显示被测信号频率的数字测量仪器[1]。以往的频率计大多数是采用单元电路或单片机技术进行设计的。本文在QuartusⅡ9.0开发环境下,借助强逻辑,弱算法的FPGA器件,用Verilog HDL语言设计了一种高精度计数式频率计[2],较传统的单元电路设计更灵活,更具可编程性,大大简化了电路结构的复杂性,提高了电路的稳定性。同时为设计者提供了一种与结构无关的设计环境,使设计者能方便的进行设计输入、快速处理和器件编程。

1 系统组成

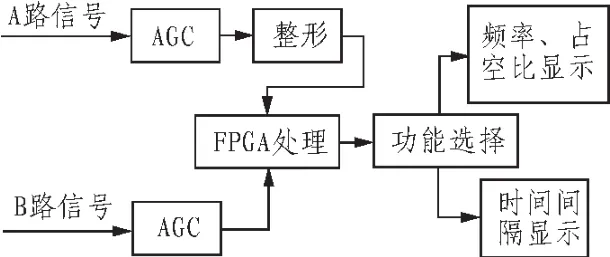

文中所述数字频率计主要由AGC模块、整形模块、FPGA处理模块、功能选择模块及显示模块组成,如图1所示。它具有频率、占空比和时间间隔测量功能,频率测量范围为10 Hz~10 MHz,占空比测量范围为10%~90%,时间间隔测量范围为0.1 us~100 ms,测量相对误差的绝对值小于0.1%。

不同的功能实现,输入的信号也不相同。实现频率、占空比测量功能时只输入幅度在50 mV~1.5 V范围的A路信号。输入的A路信号经过AGC模块后其峰峰值可稳定在4V左右,然后由整形模块处理成矩形波信号送给FPGA。A路信号输入正弦波信号时,可实现频率测量;输入矩形波信号时,可实现频率、占空比测量。实现时间间隔测量功能时,输入为A、B两路同频同周期的且幅度在50 mV~1 V范围的矩形波信号。

该数字频率计的频率、占空比和时间间隔测量功能的程序在FPGA处理模块中是同时进行的,而所得结果则是在同一个显示屏上分开显示的。功能选择模块会根据输入信号的不同,控制显示屏显示频率、占空比的数值或是时间间隔的数值。只有A路信号输入时,显示屏显示频率或占空比数值;A、B两路信号同时输入时,显示屏显示时间间隔数值。

图1 数字频率计系统组成

2 硬件电路设计

硬件电路对输入信号做放大及整形处理,使输入信号变为FPGA可检测到的信号后送入FPGA进行后续的运算。

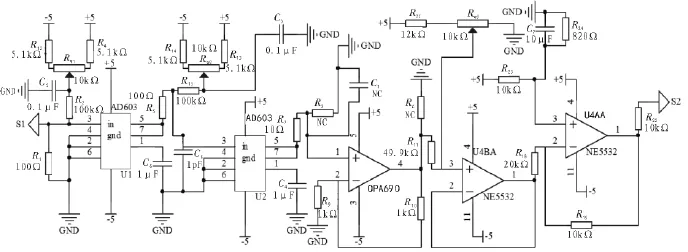

为了使输入正弦信号电压有效值在50 mV~1.5 V、频率在10 Hz~10 MHz之间时,输出矩形波电压的幅度稳定在2 V,我们采用如图2所示的AGC电路和TL3016整形电路。AGC及自动增益控制,其原理是控制信号随输入信号幅度的变化而变化,使信道输出幅度检波后的直流值与参考电压之间的误差值尽量减少到最小值[3]。AGC电路由两级AD603程控放大电路、增益控制电路组成。AD603程控放大电路由三级电路构成,即第一级调偏电路、第一级AD603程控放大电路,第二级调偏电路、第二级程控放大电路,以及末级放大电路。为了使通带内输出平坦,在第一级和第二级之间加入低通滤波。通过调节增益控制电路中的可变电阻RW3,能够实现增益的手动控制。最终,AGC输出的放大后的正弦信号S2送入TL3016整形电路转换化成矩形波。当输入信号为矩形波时,情况如上描述。

图2 AGC电路

3 软件设计

3.1 频率测量方案选取

在频率测量方法中,常用的有直接测频法、直接测周法、倍频法和等精度测频法等。其中直接测频法是以待测信号为计数脉冲在闸门信号持续时间内进行计数从而直接得出待测信号频率的方法[4]。但是这种方法在低频段误差较大,而该数字频率计所测信号频率范围很广,因此在低频段采用直接测周法进行频率测量。直接测周法则是以时钟信号为计数脉冲在闸门信号持续时间内进行计数从而得到待测信号的周期,再取倒数得到待测信号频率[5]。为了保证精度,需要找到两种方法转换的临界频率。当待测信号频率高于此临界频率时,采用直接测频法进行测量;反之,则采用直接测周法测量。经过多次实验,确定该临界频率为60 kHz。

3.2 总体结构

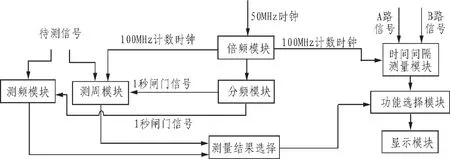

文中所述的数字频率计软件部分的总体结构由测周模块、分频模块、测频模块、功能转换模块、时间间隔测量模块、倍频模块以及显示模块组成,如图3所示。

图3 数字频率计软件部分总体结构图

倍频模块通过调用altera FPGA内部的pll将50 MHz时钟信号倍频到100 MHz,作为时钟信号分别送入测周模块、时间间隔测量模块以及分频模块;分频模块得到1秒闸门信号及清零信号分别送入测周模块和测频模块。测周模块与测频模块同时工作得到两组数据,并对其分别进行处理可得两个频率值。在频率测量结果选择模块中,分别让这两个频率值与实验所得的临界测量频率60 kHz作比较,若两个频率值均小于60 kHz,则采用测周模块所得频率值为最终结果输出;否则采用测频模块所得频率值为最终输出。在计算占空比时,采用测周模块所得数据。实现时间间隔测量功能时,送A、B两路矩形波信号给时间间隔测量模块,可得到两路信号的时间间隔。选择模块则通过开关按键控制显示模块显示频率、占空比或时间间隔。

3.3 核心部分设计

3.3.1 频率和占空比测量

在频率测量中,为了保证测量精度,系统采用直接测频法和直接测周法相结合的方式。占空比测量则采用直接测周法。下面对两种方法分别进行说明。

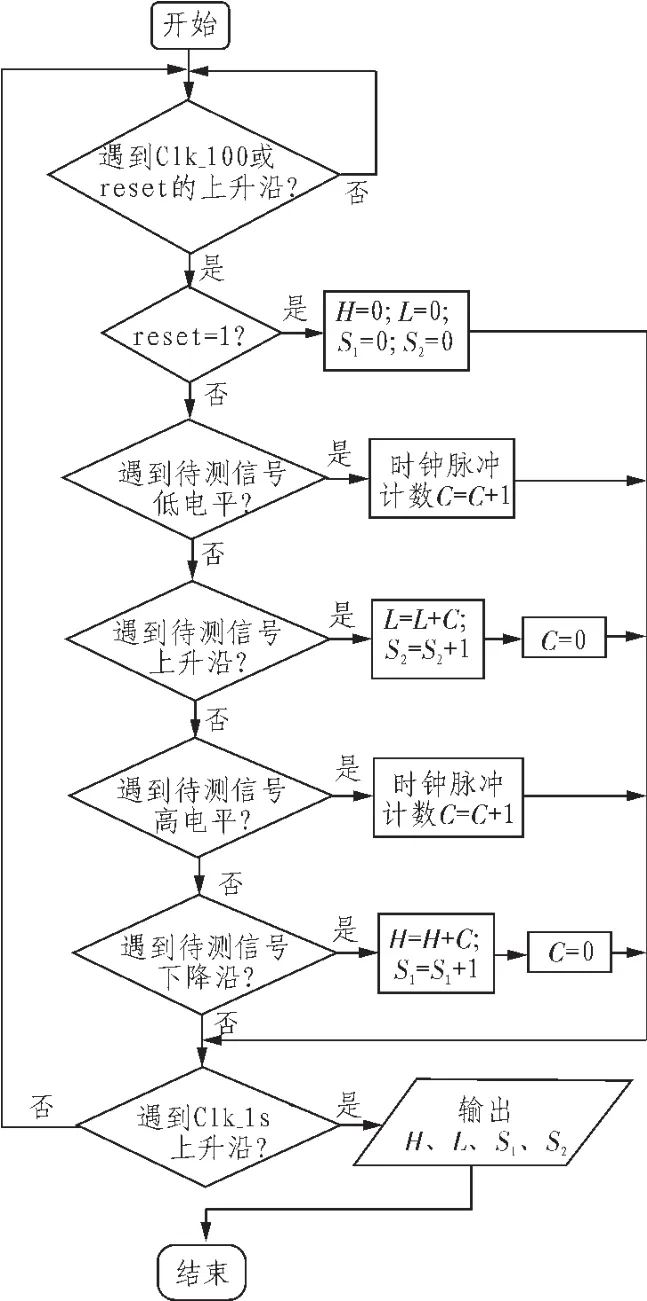

1)测周模块

测周模块程序流程图如图4所示。通过等精度思路,利用脉冲(脉冲频率Clk_100=100 MHz)计数的方式,在闸门信号(Clk_1s)持续1 s的时间内,在待测信号的上升沿启动正电平周期计数,下降沿启动负电平周期计数,并同时对到来的正负电平次数做累加记录,最终分别得到高电平时总脉冲计数值(H)、低电平时总脉冲计数值(L)、总高电平数(S1)以及总低电平数(S2)。

依据H、L、S1、S24个输出值,可知每个高电平持续时间内平均脉冲数F1=H÷S1,每个低电平持续时间内平均脉冲数F2=L÷S2。将求得的高低电平持续时间内的脉冲均值数求和F=F1+F2,再与时钟脉冲周期相乘可得待测信号周期,取倒数即可测出待测信号频率;同时高电平持续时间内平均脉冲数F1与高低电平持续时间内的脉冲均值数之和F相除,可得占空比。

2)测频模块

该模块与测周模块同步工作。宽度为1秒的闸门信号作为计数器的时钟使能信号,而被测信号则作为计数器的时钟输入。当闸门信号为高电平时,允许计数器计数;当闸门信号为低电平时,禁止计数器计数,则1秒的闸门信号持续时间内计数器的计数值即为被测信号的频率。同时为了保证测频准确,在每次闸门信号开通前提供给测频模块一个清零脉冲信号,让计数器处于零状态,保证计数器每次都从零开始计数。

3.3.2 时间间隔测量

时间间隔测量模块是测量两路信号的间隔时间的hdl描述,为总线型选择器结构。依然利用时钟脉冲计数的思想,在第一路信号上升沿到来时开始计数,在第二路信号上升沿到来时停止计数,然后读出计数值,使其再与时钟脉冲周期相乘可得两路信号时间间隔。

4结 论

本设计可实现频率范围10 Hz~10 MHz、幅度范围50 mV~1.5 V的正弦波信号的频率及矩形波信号的频率和占空比的测量功能,还可实现频率范围100 Hz~1 MHz、幅度范围50 mV~1 V的两路同频周期方波信号的时间间隔的测量功能。经多次实验验证,测量结果相对误差的绝对值小于0.1%。

图4 测周模块程序流程图

[1]张博,曹学岩,房亮.基于VHDL的简易数字频率计的设计[J].技术与应用,2013,29(6):29-34.

[2]屈宝鹏,张喜凤,李想.基于VHDL的高精度数字频率计的设计与实现[J].现代电子技术,2013,36(18):144-147.

[3]胡展威,田克纯,熬发良.数字通信系统中AGC电路设计与实现[J].广西通信技术,2011,18(3):27-31.

[4]陈治国,李剑勇,冯海兵等.基于CPLD直接测频法的数字频率计设计[J].徐州工程学院学报:自然科学版,2011,26(1):22-28.

[5]徐秀妮.基于VHDL语言的全同步数字频率计的设计与研究[D].西安:长安大学,2011.

[6]潘松,黄继业,潘明.EDA技术实用教程——Verilog HDL版[M].北京:科学出版社,2013.

Design of digital cymometer based on FPGA

YU Guo,GUO Xin-wei,LIU Xiao-hao,ZHANG Guo-dong,MA Xiao

(School of Physics&Information Technology,Shaanxi Normal University,Xi'an 710119,China)

As the development of electronic technology,it's more and more important to obtain accurate frequencies of various kinds of electronic signals rapidly.But traditional cymometer is mainly designed by unit circuits or SCM (Single Chip Microcomputer),which has narrow frequency measurement range and low measurement accuracy.The digital cymometer is made up of AGC module,plastic module,disposing and displaying module.It has functions of frequency measuring,duty ratio measuring and time interval measuring by clock counting.The digital cymometer is stable and accessible.The digital cymometer has wide frequency measurement range and high measurement accuracy.

digital cymometer;clock counting;FPGA;frequency

TN014

A

1674-6236(2016)18-0057-03

2015-09-14 稿件编号:201509094

陕西省自然科学基金项目资助(2014JQ2-6032);中央高校基金项目资助(GK201503018)

余 果(1993—),女,河南郑州人。研究方向:信号与信息处理。