基于SOPC的定时器控制数码管显示

2016-11-22王侠郭海涛

王侠,郭海涛

(内蒙古大学 电子信息工程学院,内蒙古 呼和浩特 010020)

基于SOPC的定时器控制数码管显示

王侠,郭海涛

(内蒙古大学 电子信息工程学院,内蒙古 呼和浩特 010020)

提出一种控制数码管显示的有效方法,这种方法基于一种特殊的嵌入式系统-SOPC可编程片上系统,以SOPC的应用为基础平台,利用Quartus II软件构建硬件系统,并利用NiosⅡDES软件编程,使其运行在DE1上,通过程序的控制使数码管显示,从而实现时钟的功能。实验结果表明,基于SOPC的系统环境下,可以利用定时器控制数码管显示。此外,还可以根据不同的用户需求实现不同的功能,方便了对数码管的控制,使其控制过程更加简洁有效。

SOPC;定时器;数码管;SOPC Builder

数码管是一种半导体发光器件,对其不同的管脚输入相应的电流,会使其发亮,从而显示出数字。由于价位低、使用简单等优势,其在现代工业控制、医疗器械及家电领域应用极为广泛。而随着显示数字位数的不断增加,传统的基于单片机、外部锁存器和外部译码器的设计显得愈发的复杂和繁琐,设计成本也相应的增加,显示抖动的问题愈发严重。而利用FPGA硬件的并行性操作可以完全消除抖动问题,同时提高设计的可靠性,简化设计,降低成本,因此对其进行进一步的研究很有必要[1]。

基于FPGA的可编程片上系统SOPC(system on progra mmable chip)技术是当前电子系统设计领域最前沿的技术。SOPC软核处理器克服了硬核处理器的价格偏高、处理器结构不可更改、无法集成多个处理器等缺陷,具有提升系统的性能、降低集成成本和延长产品的生命周期等优势[2]。定时器是NiosⅡ处理器系统中的一个具有控制启动、停止和复位等作用的基本单元。

在一个实际系统中,通常需要多个LED数码管。多个LED数码管不可能同时点亮,动态显示指的是多个LED数码管的轮流点亮。但其轮流点亮的速度非常快,利用人的“视觉暂留”效应,人眼分辨不出其动态闪烁,所以在人眼看来数码管上显示的是稳定的数字,在人看来各数码管是同时发光的。用定时器控制数码管显示的原理就是通过在添加组件时配置的定时脉冲来产生中断,这样在Nios II DES集成开发环境下就可以通过相应的软件代码来捕捉定时中断并记录数据,为显示提供前提。七段数码管作为FPGA开发板上标准的附带器件,其使用方法已有一套标准,文中针对于DE1(Development and Education Board)提供的七段数码管特性设计相应的逻辑模块,通过SOPC Builder坏境下的用户逻辑接口工具完成封装,最后实现在Nios II DES环境下的使用。

1 SOPC系统介绍

本文主要用到了 SOPC系统的 Nios软核处理器、Interval Timer定时器和PIO并行输入/输出3个主要部件。

1.1 Nios 软核处理器

单片机、ARM等出厂时处理器固定在芯片上,而Nios II处理器和它们不同,出厂时的FPGA是空白的,里面并没有处理器,所以Nios II处理器被称为软核处理器。Nios II处理器是需要用户利用软件进行配置的。Nios II处理器是指令总线与数据总线相独立的哈佛结构、支持32路中断输入;与普通处理器不同的是可以自定义指令,这在一些高速数据运算中有很大的优势。

1.2 IntervalTimer 定时器

Interval Timer核是SOPC Builder自带的Nios II基本外设,是avalon总线与外部接口或外部逻辑的连接模块;Nios II系统可以通过avalon主外设简单的通过读和写控制寄存器以及状态寄存器与该核实现通信,从而控制定时器的各种操作。

1.3 PIO 并行输入/输出

并行输入/输出是Avalon总线的从端外设,提供了通用I/O端口和Avalon总线之间的地址映象接口。这里说的I/O端口既可以与片上用户其他逻辑相连接,又可以与FPGA的外围器件相连接。每个PIO核可提供最多32个I/O端口,PIO核可以根据需要配置成输入模式,输出模式及双向模式,对于输入模式还可以对处理器产生中断请求。PIO核是SOPC Builder自带的IP核,可以很方便集成到Nios II系统中,是常用的Nios II外设之一,其在系统中可以与蜂鸣器,led等外设相连接。

1.4 SOPC系统开发环境

SOPC是Altera公司提出的一种灵活、高效的SOC解决方案,是一种新的软硬件协同设计的系统设计技术。SOPC系统设计主要包括以32位Nios软核处理器为核心的嵌入式系统的硬件配置,硬件设计、硬件仿真、软件调试等部分[3]。所用的基本软件有:QuarutsⅡ,SOPC Builder,NiosⅡDES。

2 基于SOPC的数码管显示的硬件实现

2.1 系统硬件结构

基于SOPC的定时器控制数码管显示所用到的组件有Nios II processor,JTAG UART,Interval Timer,System ID Peripheral,HEX_pio,Oh-chip Memory和4个LED(占用28个PIO)。

本设计使用的PIO是与外部的LED数码管连接,由于其连接的方式是直接连接,没有片选,所以我们需要设置4组PIO,用来控制4个数码管的显示,每个数码管用7个段选控制,所以我们总共需要28个输出PIO来控制数码管的显示。

2.2 硬件系统的构建

在SOPC Builder中硬件系统的构建可分为以下几个步骤:首先,设置时钟的频率参数为25 MHz;其次,添加片内存储器,选择片内存储器类型为RAM;使用的资源为M4K;数据位宽为32,总存储器大小为12 kbykes;然后添加Nios II处理器,硬件乘法器选择None,复位向量和异常向量存储器均选择前面添加的片上存储器。更改指令缓存为2 kbyke;配置定时器,更改预置为Full—featured;添加JTAG UART,均选用默认装置;配置4个7位并行输出的PIO,数据位宽选择7;最后,自动分配基地址,自动分配中断优先级,生成系统。

2.3 硬件系统的编译

硬件系统的编译可分为以下几个步骤:首先,在新建的Verilog文档中添加复位程序并保存,并将该模块例化到顶层文件。复位的内容主要是复位外部输出为低电平有效;复位低电平信号;复位寄存器为低电平有效和异步复位。其次,对系统生成后产生的inst.v文件进行相应的接口例化更改,得到工程顶层模块代码;编译文件并分配管脚;编译整个工程,生成下载用的*.pof文件;将DE1开发板与计算机连接好,给开发板上电;最后,将生成的*.pof文件下载到开发板中。

3 定时器控制数码管显示的软件实现

3.1 软件设计

目前大多数的FPGA采用硬件描述语言进行设计。本次设计采用Verilog HDL语言在系统级使用,在软件级采用的是C语言。利用定时器控制数码管显示的软件程序设计由定义寄存器映射的头文件和在Nios II系统中的驱动程序组成。

3.1.1 头文件的设置

基于SOPC的定时器控制数码管显示所用头文件如下:

#include“system.h”//系统硬件定义头文件

#include“alt_types.h”//数据类型宏定义文件

#include“altera_avalon_pio_regs.h”//PIO外设头文件

#include“altera_avalon_timer_regs.h”//定时器外设头文件

3.1.2 程序设计

对于定时器控制数码管显示的程序设计,可分为3个部分分别是初始化系统、中断函数和循环扫描数码管显示。

首先,初始化系统包括定时器初始化和PIO初始化:

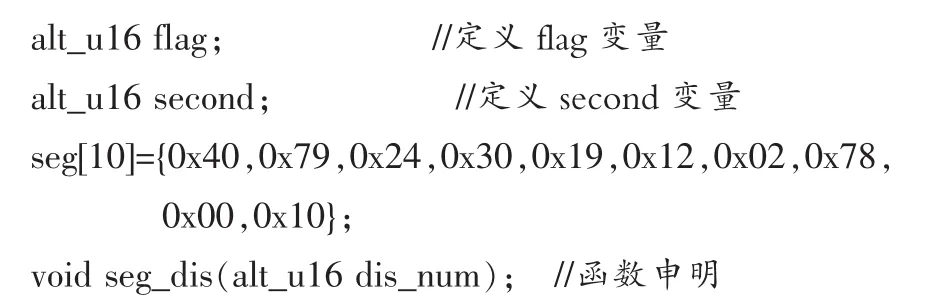

其中,alt_u8 seg[10]是对阿拉伯数字0到9进行定义,根据DE1开发板上有4个数码管显示,可以根据其不同的设置显示控制其每一段的亮灭。由于其是共阳极[4],所以为其任意一段提供一个低电平就可以点亮数码管,提供一个高电平就可以控制数码管不亮。

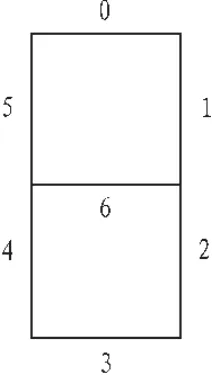

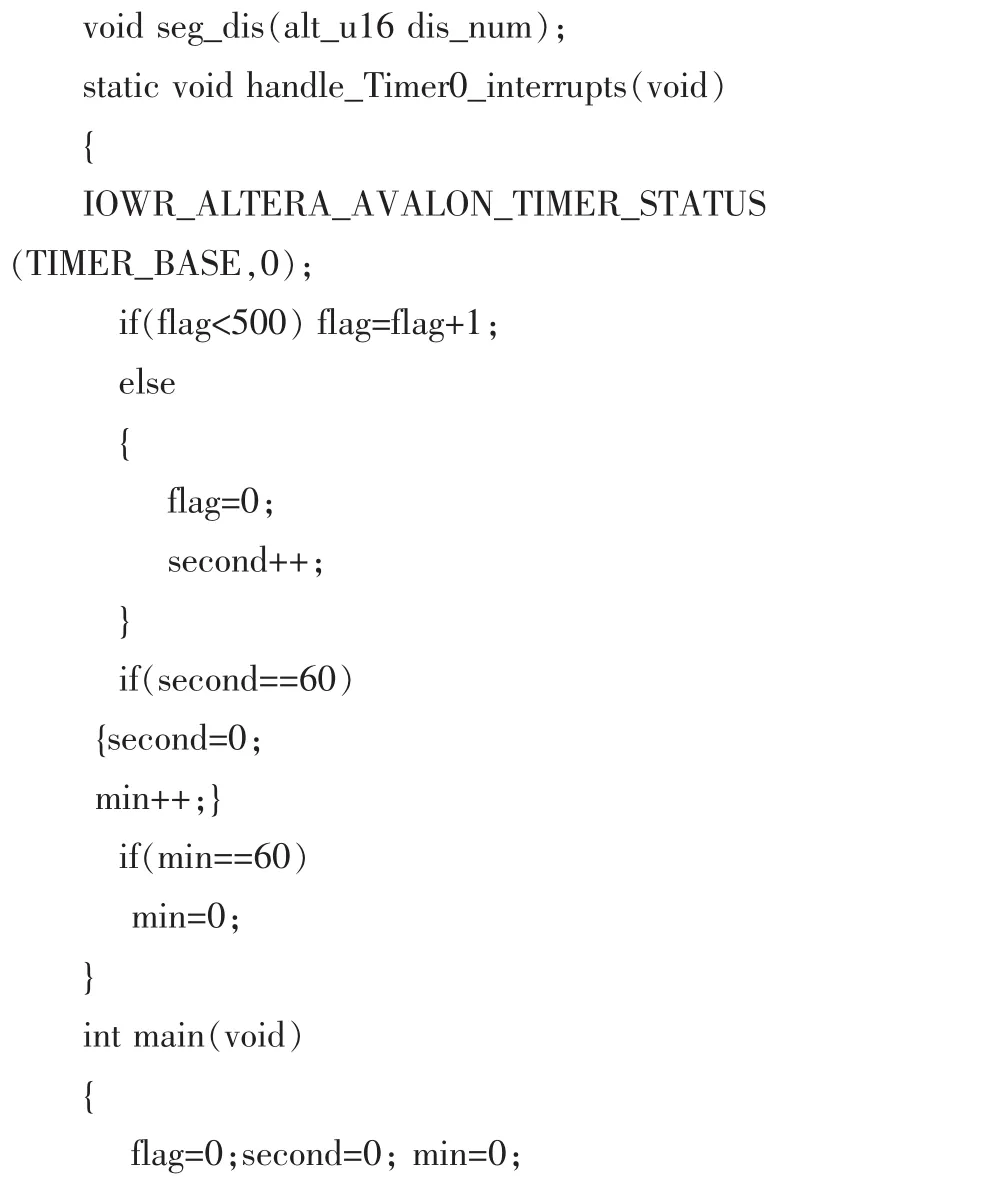

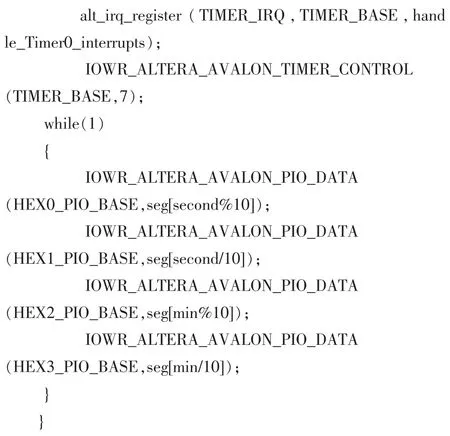

DE1中的七段数码管没有片选,只有位选,这样我们就可以通过程序来直接控制每一位的显示,并且4个数码管可以同时点亮,再根据图1所示的其每一段的位置在数码管上的显示,可以得出阿拉伯数字的二进制表示。

根据图1可以得到:

0的二进制表示为1000000,十六进制表示为0x40;

1的二进制表示为1111001,十六进制表示为0x79;

2的二进制表示为0100100,十六进制表示为0x24;

3的二进制表示为0110000,十六进制表示为0x30;

4的二进制表示为0011001,十六进制表示为0x19;

5的二进制表示为0010010,十六进制表示为0x12;

6的二进制表示为0000010,十六进制表示为0x02;

7的二进制表示为1111000,十六进制表示为0x78;

8的二进制表示为0000000,十六进制表示为0x00;

9的二进制表示为0010000,十六进制表示为0x10。

图1 七段数码管上每一段的位置

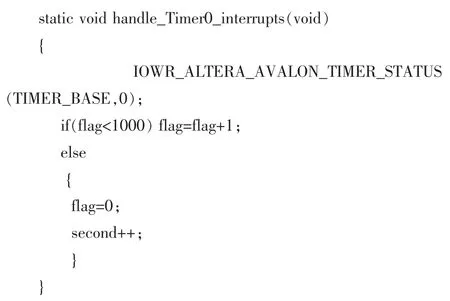

本设计的中断函数如下:

中断函数的思路是:定时器中断默认的周期值是1 ms,如果我们设置中断函数中的flag值为1 000,那么正好可以使每次调用中断函数的值为1 s,也就是每次数码管显示的每两个数值间隔1 s。

最后,是循环扫描数码管显示[5],使其实现秒表功能的程序设计:

3.2 软件实现

软件开发过程是实现基于SOPC的利用定时器控制数码管显示的另一个重要组成部分,利用定时器的原理来实现数码管的不同实现是本设计的难点,首先需要掌握Nios II DES软件的使用,并且能够熟练的操作[6]。本文的软件开发过程由以下几部分组成:

1)在Nios II DES中新建一个 NIOS II Application and BSP from Template工程,

2)对新建的NIOS2软件进行设置。

3)配置工程的系统属性。先设置软件的编译属性;再在新生成的工程中添加C源文件,将编写好的使用定时器控制数码管显示的程序添加到新建文件中;最后,添加利用定时器实现数数功能的程序。

4)编译新生成的工程。

5)将编译之后的程序运行在开发板上,查看结果。

4 结论

实验结果说明根据SOPC系统的开发原理,利用Quartus II软件中的SOPCBuilder开发工具构建硬件系统,在NiosII EDS软件中通过软件程序的控制可以实现数码管的秒表功能。

文中分为两大部分,一部分是设计基于SOPC的定时器控制数码管显示的硬件部分,另一部分是利用定时器控制数码管显示的软件设计。文中利用SOPC系统原理实现了定时器控制数码管的显示,这样大大提高了设计的便捷性并且提升了数字系统的性能。根据不同的用户需求可以通过软件编程来实现不同的功能,这样方便了对数码管的控制,是其控制过程更加简洁有效。

[1]吴厚航.爱上FPGA开发[M].北京:北京航空航天大学出版社,2011.[2]杨军.面向SOPC的FPGA设计与应用[M].北京:科学出版社,2012.

[3]YI Wu.Design of embedded web module based on SOPC[C]//国际会议.中国重庆:2012.

[4]邱锋波.基于FPGA的并行数码管显示控制设计[J].科学技术与工程,2009,9(23):7170-7173.

[5]张行松.LED数码管显示电子钟PLC程序设计原理[J].黄冈师范学院学报,2011,6(31):54-56.

[6]王锐.基于软核NiosⅡ的SOPC数据采集系统的设计[J].计算机测量与控制,2008,16(8):1199-1201.

Digital tube display controlled by a timer based on SOPC

WANG Xia,GUO Hai-tao

(Electronic Information Engineering College,Inner Mongolia University,Hohhot 010020,China)

Put forward an effective method to control the digital tube display,this method is based on a special kind of embedded system-the SOPC system on programmable chip,on the basis of the application of SOPC,about building a digital system that is controlled by a timer in the Quartus II software,and programming in the Nios II EDS software to make it run in DE1,through the control the digital tube display program,realize the function of clock.Experimental results show that the digital can display by the controlling of timer in the system of SOPC.In addition,you can realize different functions according to different requirements of users,it can convenient for controlling the digital tube,and make it more concise and effective.

System On Programmable Chip(SOPC);timer;digital tube;SOPC Builder

TN141.6

A

1674-6236(2016)15-0162-03

2015-07-26 稿件编号:201507169

内蒙古大学高层次人才引进科研资助项目(135123)

王 侠(1990—),女,内蒙古乌兰察布人,硕士研究生。研究方向:嵌入式技术、图像处理。