高性能鱼雷声靶信号处理系统设计与实现

2016-11-21黄凡

黄 凡

(海军驻昆明地区军事代表办事处,昆明650051)

高性能鱼雷声靶信号处理系统设计与实现

黄凡

(海军驻昆明地区军事代表办事处,昆明650051)

针对鱼雷声靶信号处理功能繁多、运算复杂、大数据量及高速实时处理的要求,设计了一种高性能通用鱼雷声靶信号并行处理系统。该系统在以往对鱼雷声靶数字信号处理系统研制的基础上,采用了多ADSP-TS101节点互联的网状分布式并行处理结构,基于CPCI总线和ADSPTS101处理器的高性能,包含通用信号采集并行处理模块、信号产生处理模块和数字信号处理模块。该系统结构简单,具有较好的通用性和扩展性,非常适合鱼雷面尺度声靶对数字信号处理设备大任务量高速实时处理及系统功能扩展的要求。

鱼雷声靶;信号处理;CPCI总线;ADSP-TS101处理器;并行处理;实时处理

1 引 言

随着鱼雷声靶自导技术的发展,鱼雷自导信号体制越来越复杂,这就使得鱼雷声靶对信号处理能力和功能的兼容性要求越来越高[1]。特别是鱼雷线尺度和面尺度声靶的信号处理系统,由于其工作模式繁多以及测量带宽、频率均衡和频率高分辨率带来的大数据量,给系统的通用、实时和准确检测带来了很大难度。以往在设计鱼雷声靶数字信号处理设备时都是针对特定的应用问题去选择合适的信号处理算法,然后根据算法流程确定系统的硬件结构,必然导致当信号处理内容、规模发生变化或者出现新算法时整个硬件系统都要重新设计,造成人力、物力和时间上的浪费。因此研发一种可扩展的高性能通用鱼雷声靶数字信号实时并行处理系统很有必要。一方面,可以通过灵活的软件编程来适应处理问题的变化和算法发展;另一方面,可以通过简单的硬件扩展来适应处理和应用规模的变化;同时也为鱼雷声靶的通用化设计奠定一定的技术基础。

在以往对鱼雷声靶数字信号处理系统研制的基础上[2],采用多ADSP-TS101[3-6]节点互联的网状分布式并行处理结构,设计出了基于CPCI总线和ADSP-TS101处理器的高性能通用鱼雷声靶通用信号采集并行处理模块、信号产生处理模块和数字信号处理模块。这些模块具有通用性、可扩展性好和并行处理效率高等特点。另外可用此模块构成大规模的并行信号处理系统,其简单清晰的系统拓扑结构和接口关系的特点,非常适合鱼雷面尺度声靶对数字信号处理设备大任务量高速实时处理及系统功能扩展的要求。

2 鱼雷声靶信号处理系统结构

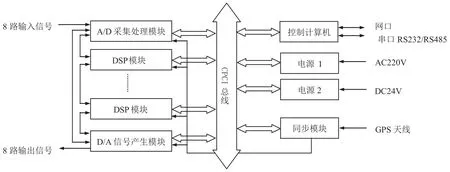

基于CPCI总线设计的并行高速数字信号处理系统是以研华MIC-3042B(主板MIC-3369)的CPCI总线控制计算机为平台,包含通用信号采集处理模块(A/D+DSP)、通用信号产生处理模块(D/A+DSP)、通用数字信号处理模块(8DSP)和GPS同步控制模块。该平台可为用户提供8个扩展插槽,用户可根据项目任务和数字信号处理系统处理任务量的大小增减模块,模块DSP节点之间采用总线或点到点的Link链路口进行互连。

基于CPCI总线的并行高速数字信号处理系统结构框图如图1所示。

图1 高速数字信号处理系统结构框图

3 处理模块设计与实现

在鱼雷声靶数字信号处理系统中,其关键部件是通用A/D信号采集处理模块、DSP模块和D/A信号产生模块,它们都采用6U标准尺寸的基于CPCI通用总线的设计思路,以下就其通用总线、DSP节点选择等进行分析和设计。

3.1CPCI总线接口设计

CPCI总线是一个开放式、国际性技术标准,由PCI总线工业计算机制造商组织PICMG(PCI Industrial Computer Manufacturer Group)负责制定和支持。CPCI总线具有严格的标准和规范,保证其具有良好的兼容性,支持多种处理器和操作系统,符合CPCI规范的扩展卡可插入任何CPCI系统并可靠地工作。CPCI标准将外设组件互连(PCI)标准特性与支持嵌入式应用的坚固机械外形完美结合在一起,其性能特征是专门针对工业环境而量身定制的。简单地说:CPCI总线=PCI总线的电气规范+标准针孔连接器+欧洲卡规范。CPCI基于ICMG2.0规范,其电气特性与PCI总线相同,因此用户的软件和普通PC机兼容,现有的PCI外围卡也可以很容易地移植到CPCI平台上。CPCI使用高密度针孔总线连接器,和使用金手指连接器的PCI卡相比,具有连接更可靠,完全气密的特点,模块的抗震性和抗腐蚀性高。CPCI还支持热插拔,即可在不关机状态下插入或取出板卡,热插拔的优点在于能增强系统性能或诊断系统故障而无需关闭系统,这对军品应用来说十分重要。

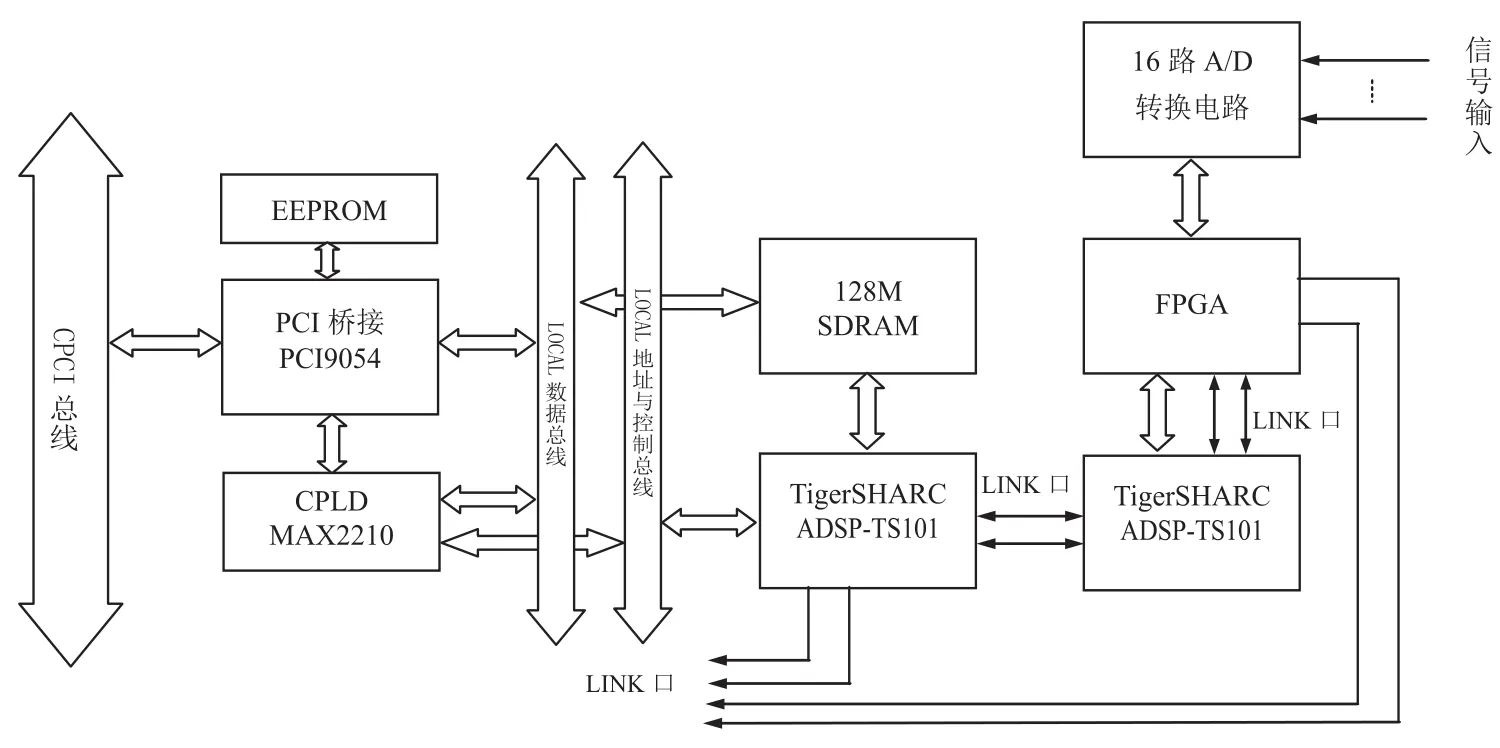

采用DSP处理系统与PCI/CPCI总线接口,能够有效利用PC机资源和大量面向CPCI总线及CPCI总线的处理芯片,降低开发成本,特别是通过PC机的图形界面操作极大方便了DSP系统调试,因而具有很大的应用价值。而连接DSP处理系统与PCI/CPCI总线接口最有效的方法是借助于PCI桥接电路。桥接电路是一种将局部总线转换成CPCI总线的专用接口芯片,它可实现CPCI规范所要求的所有硬件接口信号和配置空间寄存器。采用桥接电路能大大简化CPCI板卡的设计,缩短研发周期。本设计就采用了PLX公司的PCI9054作为桥接芯片,用来实现CPCI主控和CPCI目标(DSP局部总线)相连接功能。由于PCI9054的局部总线控制信号与ADSP-TS101引脚并不兼容,采用ALTERA公司的FPGA芯片将PCI9054的地址线和控制信号转换成与ADSP-TS101控制信号相兼容后,再连至ADSP-TS101的地址总线和控制总线上。ADSP-TS101通过桥接电路与CPCI总线相连的原理框图如图2所示,它能实现比较全的功能,如:支持CPCI主控设备对多DSP的读写,包括单字的读写操作、四字的突发读写操作及持续的突发读写操作。同时也支持局部总线的主处理器通过PCI9054来对CPCI总线上存储器设备、I/O设备所映射的空间进行单字或同步的连续访问。

PC19054与DSP间可以是异步通讯,也可以设计成同步访问模式,其中CPLD所实现的时序逻辑较为关键。EEPROM用于在系统加电启动时向PC19054加载寄存器初始化数据,来完成CPCI的配置。所有的32位PCI/CPCI系统信号直接和PC19054相连,由PC19054管理和协调CPCI的总线信号,使局部总线独立于CPCI标准总线,从而使得两套总线都能并行、高速运作。

图2 CPCI总线与ADSP-TS101桥接原理框图

3.2DSP节点单元

选用ADI公司高性能DSP处理器TigerSHARC ADSP-TS101[7-8]作为系统的核心处理节点,Tiger-SHARC系列处理器为ADI最新推出的具有业界领先性能的DSP。它采用针对通讯的应用基本架构和其它大运算量应用的要求对结构进行了优化的超高性能的超标量结构,这种独特结构集合了RISC,VLIW和标准DSP处理器的优势。TigerSHARC具有很高的时钟频率和深度流水线结构,还能同时支持32位定点和32位浮点数据类型。

ADSP-TS101主要性能:①ADSP-TS101的最高内核时钟是300MHz,指令周期可达到3.3ns;②可以提供1.8G FLOPs的浮点处理能力;③6Mbit的片内SRAM;④双运算模块每个包含一个ALU,一个乘法器,一个移位器和一个寄存器组;⑤双整数ALU,提供数据寻址和指针操作功能;⑥基层1/0包括14通道的DMA控制器,外部端口,4个链路口,SDRAM控制器,可编程标志引脚,2个定时器和定时器记满引脚等用于系统;⑦TI EEE 1149.1兼容的JTAG端口用于片上仿真;⑧片上仲裁通过共享总线可无缝连接多达8个TigerSHARC DSP。

另外,ADSP-TS101还提供了HOST微处理器接口、Flag标志等功能,正是这些优异的特点,使其非常适于高速实时信号处理场合,成为构成并行处理系统的理想DSP芯片。

3.3处理模块的并行设计实现

通过鱼雷声靶信号处理流程、数据处理流量和可扩展性分析,设计了一种基于全局分散存储器和局部共享存储器的多DSP处理器结构。即所有DSP之间直接或间接通过LINK口互连,构成网状分布式并行处理系统,其拓扑结构可以由软件编程改变,而对于小规模大数据量的数据存储与交换,由其内部所设计的小范围共享总线实现。整个系统中各并行子模块之间由后背板上所设计的LINK口相连,可扩展成满足更大任务处理能力的分布式并行系统。

采用ADSP-TS101构成的全局分散存储器和局部共享存储器的多DSP处理器模块,各处理接点与外部总线间无交叉访问,无需复杂的总线逻辑仲裁,系统软硬件之间关联小,可以灵活适应于不同的数据处理算法,并可方便的扩充系统数据吞吐能力。

鱼雷面尺度声靶等需要超大容量存储的应用领域,利用ADSP-TS101处理器提供的可与标准的SDRAM进行无缝连接及其无需附加外部仲裁逻辑的特点,可以设计出超大容量存储器模块。

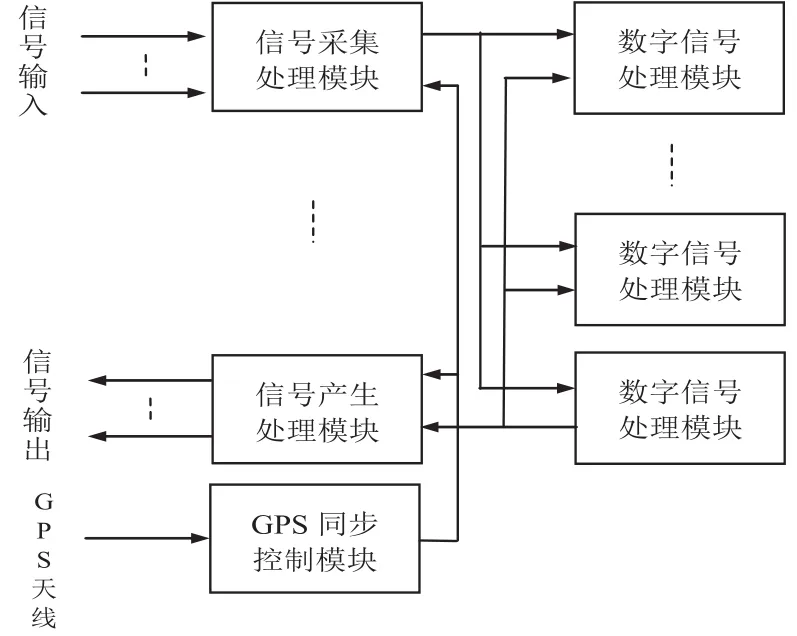

根据以上设计思路,设计一种基于CPCI总线的通用信号采集处理模块、通用信号产生处理模块和数字信号处理模块。图3所示为基于CPCI总线的通用信号采集处理模块系统框图。

该模块采用标准6U印制板,每个模块上包含由2片ADSP-TS 101芯片作为处理节点,并辅以链路口互连的点到点通信构成了基于全局分散存储器和局部共享存储器的多处理器结构的通信方式。该模块具有运算能力强、I/O带宽大、能灵活改变拓扑结构、可扩展性、通用性及系统容错能力强的特点。

图3 基于CPCI总线通用信号采集处理模块系统框图

4 系统实现

根据不同的鱼雷声靶(如点源固定靶、线列式尺度固定靶、面尺度固定靶以及活动靶等)对信号处理系统功能及运算量的要求,可利用上述基于CPCI的总线设计通用信号采集处理、信号产生处理和数字信号处理处理模块,按照图1所示结构,就可组成一实时信号处理系统,其基本工作流程如图4所示。

图4 鱼雷声靶实时信号处理流程图

信号采集处理模块将鱼雷声靶前放送来的模拟信号进行转换,由模块上的FPGA和DSP进行预处理后,通过板间高速Link口送给不同的数字信号处理模块进行并行处理。数字信号处理模块完成对数字信号的鉴向、鉴幅和频率检测,从而实现对鱼雷自导信号的实时快速检测。当确认是鱼雷自导信号后,采集存储的数据通过板间高速Link口送入信号产生处理模块。信号产生处理模块依据鱼雷声靶配置的功率放大器和发射换能器参数,完成对数字信号的频率均衡后,送D/A转换形成回波模拟信号,经滤波、强度控制后输出目标回波信号。

整个系统基于CPCI总线设计,各处理模块中DSP节点进行不同功能程序及控制字的加载、调试均通过CPCI总线由控制计算机实现。鱼雷声靶参数的修改、功能的增减或变化不需要修改系统硬件,只需对系统处理软件作相应修改即可。实验表明,整个系统结构简单、体积小、可靠性高,并且有很好的通用性、灵活性和系统可扩展性。

5 结束语

综合考虑鱼雷声靶实时信号处理系统的特点,设计了一种高性能鱼雷声靶通用并行信号处理系统。该系统各组成部分均采用基于CPCI总线的模块化设计,通用性强。各处理模块均基于ADI公司新一代高性能DSP处理器,采用各处理节点互连的网状分布式并行处理结构。各处理节点充分利用DSP本身大容量内存,相互之间可以无总线交叉完全并行工作。同时对于需要超大数据容量的处理模式,系统还利用无需总线仲裁逻辑的ADSP-TS101的SDRAM接口设计了超大容量存储器。整个系统充分考虑了鱼雷声靶的特点,所设计系统结构简单、清晰,可扩展性强。它不仅适用于鱼雷声靶并行信号处理系统,也可用于需要高速、实时大规模并行数据处理的末弹道测量系统等信号处理领域。

[1]蒋均齐.鱼雷声靶技术研究[D].长沙:国防科学技术大学,2006.Jiang Junqi.Study on Torpedo Sonar Technique[D].Changsha:National University of Defense Technology,2006.

[2]王楠.基于AD7655的鱼雷声靶数据采集系统设计分析[J].舰船电子工程,2010,30(4):166-168.Wang Nan.Analysis for the Design of the Data Acquisition System of Torpedo Acoustics-Drone Based on AD7655[J].2010,30(4):166-168.

[3]任家富,庹先国,陶永莉.数据采集与总线技术[M].北京:航空航天大学出版社,2008.Ren Jiafu,Tuo Xianguo,Tao Yongli.Data Acquisition and Bussing Technique[M].Beijing:Press of Beijing University of Aeronautics and Astronautics,2008.

[4]李国辉,杨宏.新一代Tiger SHARC结构的ADSPTS101及其应用[J].现代电子技术,2005,16:5-8.Li Guohui,Yang Hong.TheNewGenerationTiger SHARC ADSP-TS101 and Its Application[J].Modern Electronics Technique,2005,16:5-8.

[5]王菲,汪学刚.ADSP-TS101外部总线接口技术[J].现代电子技术,2007(11):53-55.Wang Fei,Wang Xuegang.ADSP-TS101 External Buss Interface Technology[J].2007(11):53-55.

[6]高渊,许会玲.基于ADSP-TS101的数字信号处理机实现[J].现代电子技术,2006(20):13-15.Gao Yuan,Xu Huiling.A Digital Signal Processor Based on ADSP-TS101[J].Modern Electronics Technique,2006(20):13-15.

[7]刘书明,苏涛,罗军辉.TigerSHARC DSP应用系统设计[M].北京:电子工业出版社,2004.Liu Shuming,Su Tao,Luo Junhui.Design of TigerSHARC DSP Application System[M].Beijing:Publishing House of Electronics Industry,2004.

[8]冯小平,曹向海,鲍丹.TigerSHARC处理器技术及其应用[M].西安:西安电子科技大学出版社,2010.Feng Xiaoping,Chao Xianghai,Bao Dan.TigerSHARC Processor Technology and Its Application[M].Xi'an:Xidian University Publishing House,2010.

Design and Realization of Signal Processing System of Torpedo Acoustic Target With High Performance

Huang Fan

(Naval Military Office Stationed at Kunming Area,Kunming 650051,China)

The signal processing system of torpedo acoustic target requires more functions,complicated calculation,huge information and high-speed real-time processing.This paper designs a parallel processing system with high performance.Based on CPCI bus and ADSP-TS101 processor,a reticulated parallel processing structure with ADSP-TS101 points interconnecting is used and signal collecting module,signal producing module and digital signal processing module are contained.With the simple system structure and good universal property and scalability,it can be well used in design of the signal processing system of torpedo acoustic target to meet the requirements mentioned above.

Torpedo acoustic target;Signal processing;CPCI bus;ADSP-TS101 processor;Parallel process;Real-time processing

10.3969/j.issn.1002-2279.2016.01.020

TP368.1

A

1002-2279(2016)01-0079-04

黄凡(1983-),男,湖北天门人,工程师,博士,主研方向:装备监造与目标探测、信号处理。

2015-03-18