基于ARM&FPGA的1394仿真测试前端系统设计

2016-11-17马云云王金波

苏 宇,孔 璐,周 珊,马云云,王金波

(中国科学院 空间应用工程与技术中心,北京 100094)

基于ARM&FPGA的1394仿真测试前端系统设计

苏 宇,孔 璐,周 珊,马云云,王金波

(中国科学院 空间应用工程与技术中心,北京 100094)

针对在航天嵌入式软件测试中遇到的将1394总线仿真测试融合到分布式测试系统中的实际需求,提出了一种基于ARM&FPGA架构的1394仿真测试前端系统;在简单介绍了1394总线和分布式测试系统后,设计和实现了1394仿真测试前端软硬件,并基于此前端构建分布式仿真测试系统;经测试,1394仿真测试前端满足1394等时数据包和异步数据包的收发时序要求,并成功应用于某航天器软件第三方评测中。

IEEE1394协议;ARM;现场可编程门阵列;分布式系统

0 引言

近年来,伴随着载人航天技术的飞速发展,系统的复杂度越来越高,对各个子系统之间的数据传输速率的要求也在不断提高;而且随着航天器上的载荷设备进行的科学探测和科学实验的越来越丰富和深入,对数据通信速率的要求也随之提高,原有的1553B总线的1 Mbps的传输速率已经无法满足高速数据通信要求。IEEE1394是一种高速串行总线,一项与平台无关的技术,可以应用于各种设备和PC机中,凭借这种与众不同的跨平台能力,得到了众多的IT厂商(Microsoft和Intel)的大力支持[1]。但是在目前的市面上众多的嵌入式IEEE1394开发系统中,几乎都是通用设备,接口较为单一,用户软件操作界面较为复杂。有时候为了完成实际的任务,不得不花费较大的精力去学习和配置用户软件;甚至有时候还无法将其完美融入到现有的仿真测试系统中,对重新构建分布式集成测试系统也会有较大影响。

综上所述,本文在对IEEE1394总线协议以及分布式集成测试系统结构简单分析的基础上,由配置项级的航天嵌入式软件第三方测试中关于IEEE1394总线的具体测试需求,设计了IEEE1394总线仿真测试前端系统,届时IEEE1394总线数据帧和任务调度运行于移植了嵌入式Linux操作系统的ARM11(S3C6410)处理器中,以ARM+FPGA为硬件核心的控制处理器就可以根据仿真监控测试系统的测试指令[2],实现灵活对IEEE1394协议芯片的初始化、工作模式以及消息进行配置,测试人员只要根据测试需求,通过在监显控制终端配置一系列指令就可以完成对IEEE1394总线设备的功能测试、强度测试以及故障测试等。

1 IEEE1394总线简介

IEEE1394是一种高速串行总线,也称“火线(FireWire)”,其最早由Apple公司在20世纪80年代主导开发的一种高速实时数据传输总线,意在简化其计算机的连线。在1995年由IEEE(电气与电子工程师协会)正式制定为总线标准,被认定为IEEE1394-1995规范,即IEEE1394[3]。IEEE1394早期版本如IEEE1394a在Backplace模式下支持12.5 Mbps、25 Mbps以及50 Mbps等传输速率,在Cable模式下则可以达到400 Mbps的速率;而在后来发布的新版本如IEEE1394b,传输速率则可达到800 Mbps;在2007年更新的IEEE1394c规范中传输速率则可达到1.6 Gbps和3.2 Gbps。

IEEE1394是一项成熟的技术,几乎被所有现代操作系统所支持[4],广泛应用于数码相机、数字摄像机、电视机顶盒以及计算机及其外部设备中。其中IEEE1394b还被用于F-22猛禽战斗机和F-35闪电II攻击战斗机数据总线中[5]。此外,美国国家极轨道军事环境卫星系统(NPOESS)和地球行星探测器(FPT)等航天器都采用了IEEE1394总线进行设备间的通信。

IEEE1394串行总线支持等时传输和异步传输,分别用于等时事务和异步事务的传输[6]。异步传输不占据固定的带宽, 但能保证节点获得时间上的公平访问;等时传输以固定的时间间隔(125 μs)发送数据,有着高于异步传输的优先级[7]。

IEEE1394总线根据协议可以分为4个部分,即物理层、链路层、事物层以及总线管理层。物理层的作用是提供设备间的电气连接以及机械连接,主要特点是提供逻辑信号到物理电气信号的转换[8]。链路层的主要功能是转化数据流格式使其按照协议成为总线可以识别的数据包[9]。链路层也对进来的等时包或异步包进行地质或信道号的解码,以及CRC校验[10]。事务层只处理异步包,提供读事物、写事物以及锁定事物等操作[11],但是不提供任何有关等式传输的服务。总线管理层的主要功能是对总线进行配置,并管理各个节点[12],同时设定自身的传输速度和工作模式等。

2 仿真测试系统概述

分布式仿真测试平台——DSTP (distributed simulation testing platform)是采用半实物仿真原理,通过对被测试的目标板进行仿真,模拟出被测目标的运作环境,从而实现对被测试目标系统进行动态、闭环、非侵入式的系统仿真测试[13]。

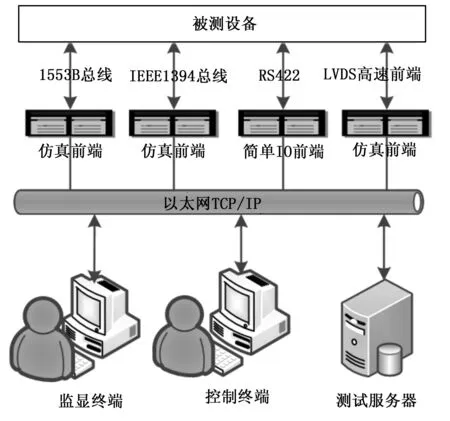

一般来说,DSTP主要由测试服务器、嵌入式测试前端、被测设备以及监显控制终端等构成。如图1所示。

图1 分布式仿真测试系统结构图

监显和控制终端的功能:

1)调用测试数据库中已构建好的测试指令序列,完成对测试数据和测试指令的配置操作,发起测试行为;

2)测试结果数据的回显及回放:即测试监显终端将仿真测试前端回传的被测软件反馈数据包进行实时显示,以供测试人员参考;

3)测试数据的判读功能:即测试人员事先写好数据判读脚本或判读软件,并嵌入到测试监显终端中,每当被测软件有下行数据包需要判读时,即可通过测试监控终端的数据判读功能,生成判读结果数据或判读报告,以供测试人员查看或参考。

根据测试的具体需求,测试服务器上一般运行大型关系型数据库,如:Oracle、IBM DB2以及Microsoft SQL Server等。测试服务器的功能:

1)测试指令序列存储:根据被测软件的实际特点,在数据库中构建并存储测试指令序列的数据模型;

2)测试数据存储:将测试人员配置的测试激励数据以及被测软件反馈的原始测试结果数据进行归档以及存储。

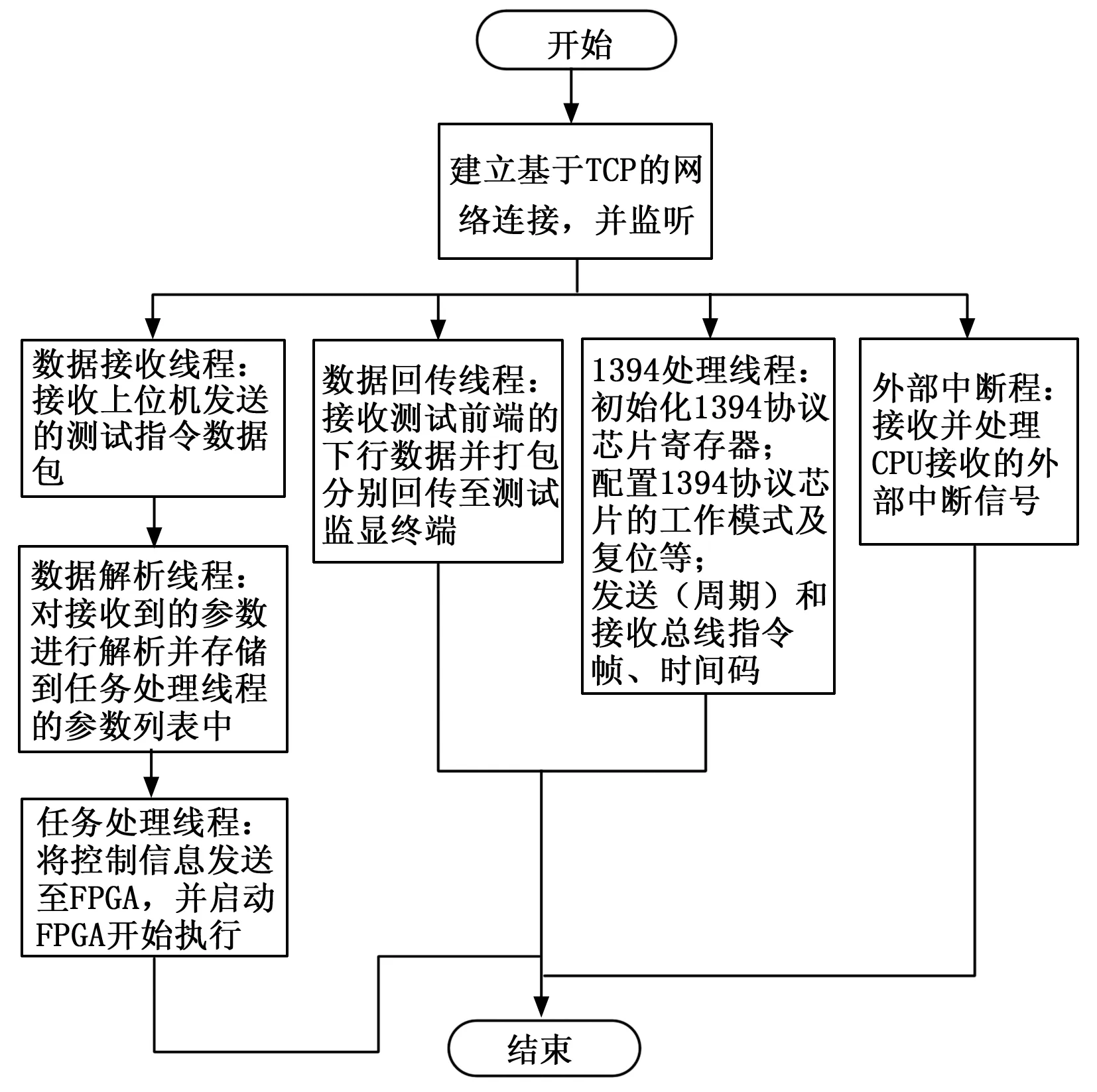

由图1可知,嵌入式仿真测试前端是连接测试监控终端和被测设备(软件)的桥梁,根据被测软件的具体测试需要,测试前端可由一个或多个测试前端构成,在本设计中,整个系统的工作流程如图2所示。

图2 仿真测试系统工作流程图

3 IEEE1394仿真测试前端硬件设计

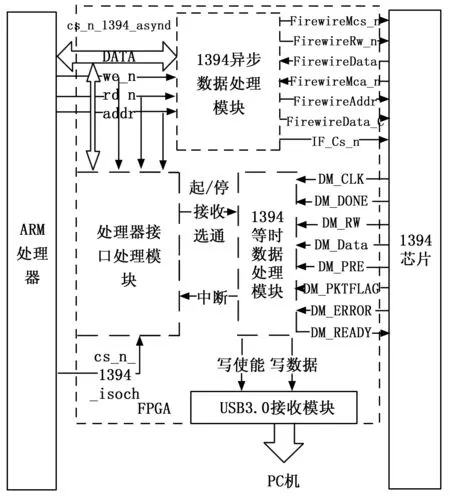

本文要实现的IEEE1394仿真测试前端在结构上仿真测试指令的处理以及IEEE1394 总线协议芯片的帧和消息处理部分,系统硬件结构框图如图3所示。

图3 系统硬件设计框图

在本设计中,仿真测试前端板采用了核心板+底板的设计模式,核心板采用的是ARM+FPGA的通用架构,不同测试前端之间的核心板可以互换;由于底板的硬件资源有限,底板是采用通用接口和专用接口组成,通用接口是指RS232、SD卡、以太网以及电源模块等;专用接口根据测试需要可包含RS422接口、1553B总线接口、IEEE1394接口、USB3.0接口等在内的一种或多种专用接口。

测试开始时,由测试监控终端调用测试服务器内已经组建完成的测试指令序列,IEEE1394仿真测试前端通过以太网接收测试指令序列,并对其进行解析处理,从而完成对IEEE1394协议芯片的配置以及测试激励数据的转发,驱动IEEE1394协议芯片和IEEE1394 PHY芯片的运行;同时通过多线程设计将被测目标软件反馈的数据打包并传送至测试监控终端。

系统上电后,运行于ARM中的应用程序软件会完成对IEEE1394协议芯片内部寄存器的初始化,以及芯片工作模式的设置,然后等待测试控制终端发起测试任务。FPGA 内部对IEEE1394协议芯的读写操作分别进行, 为了通信的快速性和有效性,读操作和写操作都实例化了双口的RAM,ARM 与IEEE1394协议芯片之间往来的数据帧首先经过双口的RAM,FPGA 内部将数据帧和控制信号转化成ARM 和IEEE1394 协议芯片需要的时序,再进行数据传输。

3.1 NAND Flash和SDRAM存储器

NAND Flash 存储器是断电非易失型存储器,主要用于存放Bootloader、内核映像文件、根文件系统以及用户应用程序等,在本文中,使用一片SAMSUNG公司型号为K9G8G08U0A容量大小为1 GB NAND Flash芯片;SDRAM 存储器是断电易失型存储器,本文中SDRAM采用两片SAMSUNG公司的K4X51163PC芯片,每片容量大小为128 MB,数据运行速度可达266 MHz。

3.2 ARM处理器和FPGA芯片

本文中,嵌入式仿真测试前端的微处理器采用SAMSUNG公司的ARM11—S3C6410微处理器,该微处理器基于ARM1176JZF-S内核,拥有强大的内部资源,可稳定工作在533 MHz,支持多种NAND Flash和Mobile DDR,同时支持以太网、RS232以及SD卡等多种外部接口;FPGA采用的是Xilinx公司的Virtex5系列的XC5VLX110T芯片,该芯片资源丰富,与ARM之间采用的是三态总线相连。同时该款FPGA芯片与IEEE1394协议芯片输出都是3.3 V信号,因此它们之间采用直连进行通信。

3.3 IEEE1394协议芯片

在本设计中,IEEE1394协议芯片采用的是美国德州仪器公司(TI)的TSB12LV32芯片,物理层芯片采用TI公司的TSB41AB3芯片。TSB12LV32链路层芯片全面支持 IEEE 1394-1995 和P1394a高速串行总线协议规范;支持等时数据和异步数据传输等功能;芯片中含有一个通用发送FIFO和一个通用接收FIFO,大小均为2 kB。

物理层芯片TSB41AB3全面支持 1394-1995和P1394a高速串行总线协议规范; 提供 3个线缆端口,最高速度可达 400 Mb/s; 芯片工作时钟为24.576 MHz,由外部晶振提供。物理层芯片的/ISO管脚是链路层接口隔离控制标识位。该引脚电平的高低决定了链路层芯片和物理层芯片之间电路的连接方式:直接连接方式还是隔离电路方式;本文中/ISO引脚接低电平,即链路层芯片和物理层芯片采用了直连的方式。

4 IEEE1394仿真测试前端软件设计

在本设计中,不仅要求系统能够控制IEEE1394协议芯片的上电初始化、复位、工作模式的设定等,还要求其能够实时响应测试控制终端发送的测试指令序列和被测设备的反馈数据,因此在ARM处理器上移植了嵌入式操作系统,测试人员只需根据测试具体需求建立不同优先级的测试任务,由嵌入式操作系统完成各个任务的调度,这样大大提高了编程的效率和代码可维护性。

在本设计中,IEEE1394嵌入式仿真测试前端系统选用了嵌入式Linux 操作系统,嵌入式Linux操作系统具有内核小巧、开放源代码、开发简单等优点。嵌入式Linux系统软件的开发包含了Bootloader与嵌入式Linux内核的修改与编译、设备驱动程序的开发以及用户应用程序的开发3个部分。

4.1 Bootloader与嵌入式Linux内核的修改与编译

一个完整的嵌入式Linux系统需要包含Bootloader、内核映像文件以及根文件系统3个部分。Bootloader是在硬件板上电时就加载运行的用于初始化硬件设备、引导嵌入式Linux系统运行的一段程序。

在本设计中,选用U-Boot1.6作为Bootloader。为了提高ARM与FPGA之间的通信能力,修改U-Boot1.6中Board/Samsung/smdk6410/smdk6410.c 下的函数DM9000_pre_init(),将其中的宏SROM_BC4_REG 和SROM_BC5_REG 修改为0x22032200,这样ARM 与FPGA 之间设备通信软总线由原来的8 bit位宽提高至16 bit位宽,大大提高了通信效率。

在Linux内核源代码的根目录下执行make menuconfig命令,以此来对Linux内核配置进行简单的修改。在本文中,通过去除“Device Drivers->Input device support->Keyboards”选项及其子选项来释放原操作系统中被外部键盘占用的CPU外部中断接口,以便FPGA与ARM之间以中断方式进行通信。然后运行make zImage -jn进行编译内核映像文件,n值通常为执行编译计算机CPU的逻辑内核数。编译结束后,在/arch/arm/boot路径下即可得到内核映像文件:zImage。

4.2 嵌入式Linux驱动程序开发

驱动程序是联系用户应用程序和硬件的桥梁。Linux内核已经集成了市面上多数硬件芯片的驱动程序,如本设计中使用的网络芯片DM9000E的驱动程序,大大节省了开发周期。在本设计中,FPGA芯片作为嵌入式Linux操作系统的一个外设,而Linux内核并没有集成该款芯片的驱动程序,因此需要重新开发驱动程序。将所有外设均视为文件进行处理是Linux设备驱动的一个非常重要的性质,因此在本文中将所有的外设均当作字符设备来编写驱动程序。

通过static const struct file_operations fdev_fops来定义顶层用户应用程序层调用设备文件的常用函数,包括设备读、写操作,设备的打开与关闭等操作。通过static int __init fdev_init(void)和static int __exit fdev_exit(void)函数分别完成设备注册、内存堆栈空间的分配以及设备的注销和内存堆栈空间的回收等。为设备分配新的设备号,建立与实际使用的Linux内核版本号以及内核配置相一致的依赖关系,然后编译并生成可以动态加载的*.ko文件,然后通过insmod命令将编译好的*.ko文件加载到内核中,用户应用程序可以根据相应的文件名直接调用该设备。

4.3 用户应用程序开发

应用程序的开发可以根据用户实际测试任务的需要,来决定任务的类型以及开启线程的数量,本设计中,根据实际测试的需要,将任务分为4个主要的部分,为每个任务线程分配足够的堆栈空间,线程之间的通信通过互斥锁以及信号量来实现。本文中用户的应用程序框架如图4所示。

图4 系统软件设计结构图

IEEE1394协议芯片参数设置和工作模式的设置是系统应用软件设计的关键。系统上电后,1394处理线程即对1394协议芯片内部寄存器进行初始化;测试人员通过测试监控终端配置参数来完成IEEE1394协议芯片的复位以及工作模式的设定,并通过监显终端实时回显的数据查看芯片当前的工作状态以及工作模式。

4.4 FPGA固件编程

本文中,在充分考虑了系统的可靠性和可维护性,程序设计按照功能块划分,可分为以下3个模块。

1)1394异步数据处理模块。

本模块与1394芯片的异步数据接口连接,主要完成1394异步数据接口与ARM处理器接口之间的时序转换。当仿真测试平台向1394芯片发送异步数据包时,本模块根据接收到的ARM处理器写使能信号、写地址和写数据,按照1394异步数据传输时序要求将数据包依次写入用户配置的地址中;当仿真测试平台请求读取1394芯片中某寄存器的值时,ARM处理器向本模块发起两次读操作,第一次读操作后,本模块根据接收到的读地址从1394芯片中读取相应的值,并在第二次读操作时将该值输出至ARM数据总线上,供ARM处理器读取。

2)1394等时数据处理模块:

本模块与1394芯片的等时接口连接,主要功能是按照用户配置要求接收固定长度的等时数据包,并写入USB3.0接收模块中,最终传输到PC机上保存成数据文件。

3)处理器接口处理模块:

本模块与1394等时数据处理模块配合使用,主要功能为解析ARM处理器发送的用户指令,控制1394等时数据处理模块开始或停止接收等时数据包。

各个模块之间的关系如图5所示。

图5 FPGA内部各模块之间的关系图

5 1394测试前端测试结果与分析

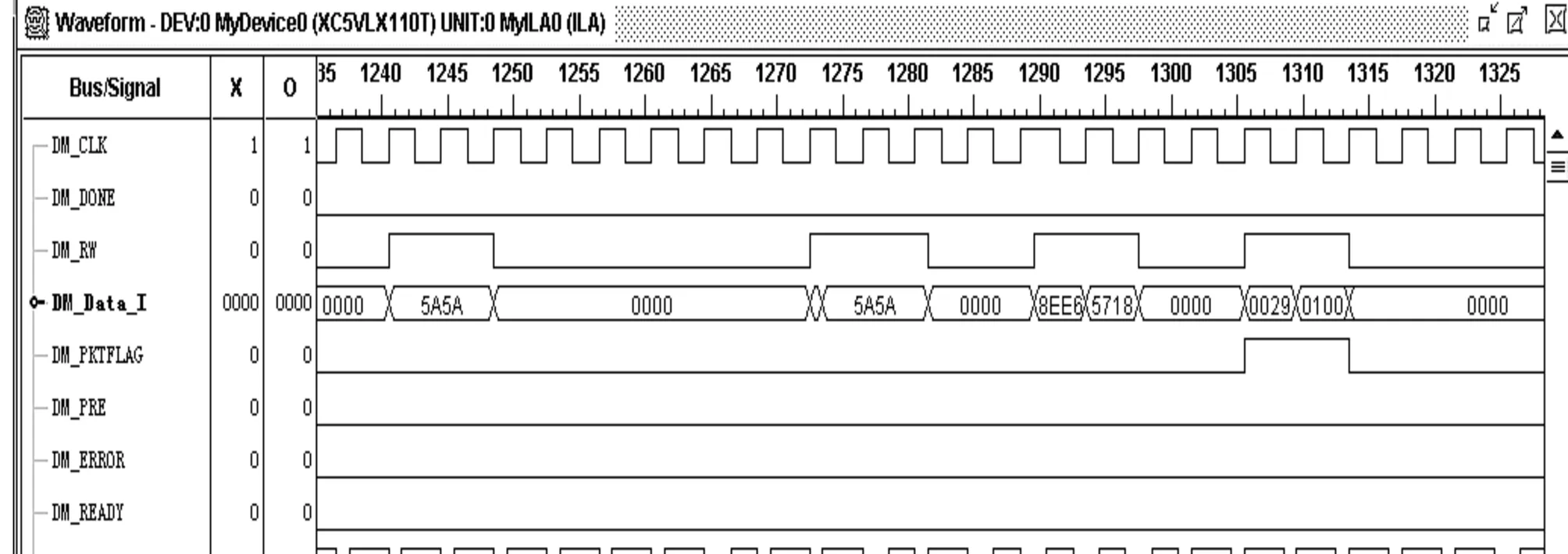

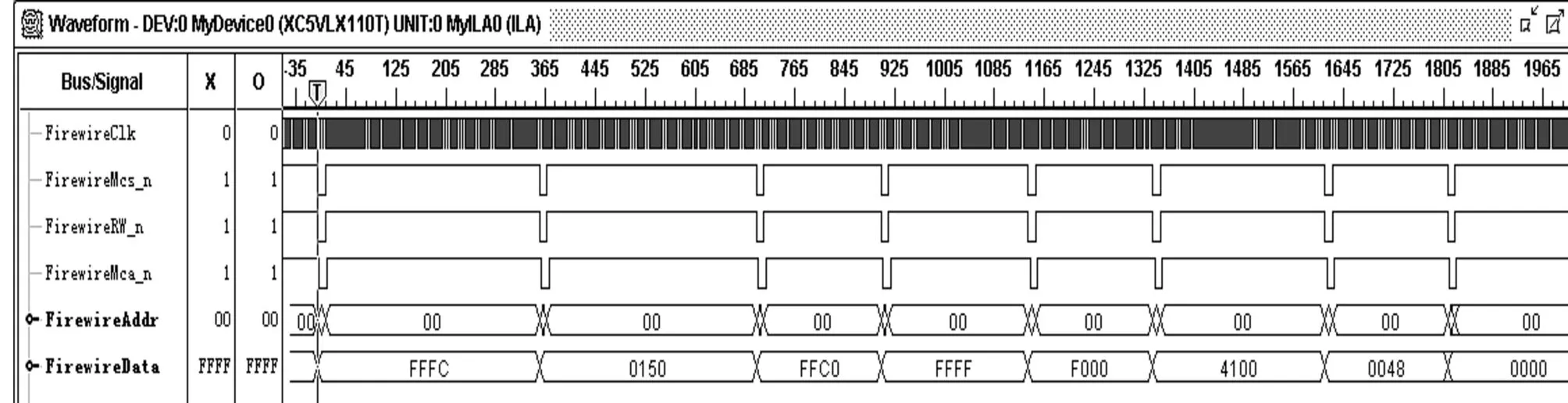

为了验证本设计的实用性与完整性,利用本设计按图1所示构建一套1394分布式仿真测试系统,采用ChipScope(片上示波器)与1394总线分析仪相结合的方式对所设计的1394总线仿真测试系统的功能进行测试。根据实际测试的需要,对1394等时和异步数据包的传输分别进行了测试,结果如图6和图7所示。

图6 等时数据包接收时序图

图7 异步数据包的发送时序图

最终的测试结果表明,测试前端的发送数据包和接收数据包与1394总线分析仪监测到的数据内容完全一致,时序也满足1394协议时序要求,因此本设计完整实现了1394总线等时数据包和异步数据包的发送和接收功能。

6 结论

本文在充分分析了当前载人航天嵌入式软件测试过程中遇到的实际问题的基础上,设计并研发了基于ARM&FPGA架构的分布式1394仿真测试前端,工程实践表明,本设计作为测试系统的一部分,成功完成了对载人航天工程某型号航天器嵌入式1394软件的配置项级测试,包括功能测试、性能测试、强度测试以及故障测试等,不仅大大提高了测试的效率,而且对类似测试系统(前端)的研制也具有较高的参考意义。

[1] 杜 倩. 基于1394串行总线图像采集的硬件设计[D]. 天津:天津大学,2006.

[2] 王 彬,张 涛. 基于ARM-Linux 的1553B 仿真测试前端系统[J]. 电子设计工程,2013,20:147-150.

[3] 王桂强. 基于 IEEE1394 总线的高速相机数据传输方案设计[D]. 哈尔滨:哈尔滨工业大学,2011.

[4] Brown K A, Frak B, Gassner D, et al. IEEE 1394 Camera Imaging System for Brookhaven’s Booster Application Facility Beam Diangostics*[A]. EPAC’02[C].2002.June,2-7.

[5] 蔡伟鹏. 应用于1394b物理层实现的时钟数据恢复电路的研究和设计[D]. 北京:北京交通大学,2014.

[6] 常 安. IEEE1394物理层链路接口的设计与验证[D]. 西安:西安电子科技大学,2014.

[7] 金晓红, 高有行. IEEE1394 协议在外设端接口中的应用[J]. 计算机测量与控制,2003,11(10):809-811.

[8] 陈尔钐. 1394总线链路层系统架构设计及接收模块实现[D]. 西安:西安电子科技大学,2014.

[9] 李 洁. 基于IEEE1394数据链路层芯片设计与验证[D]. 西安:西安电子科技大学,2014.

[10] 张 伟. 基于IEEE1394总线数控系统实时通信的DMA方式实现[D]. 上海:上海交通大学,2009.

[11] 张盼盼. 基于IEEE1394b交叉通道数据链路FPGA的验证[D]. 西安:西安电子科技大学,2014.

[12] 张 琨. 基于IEEE1394数据传输系统的驱动程序及应用程序设计[D]. 西安:西安电子科技大学,2014.

[13] 蔡建军. 嵌入式软件测试实用技术[M]. 北京:清华大学出版社,2010.

Design of Front End System of IEEE1394 Simulation Test Based on ARM&FPGA

Su Yu, Kong Lu, Zhou Shan, Ma Yunyun, Wang Jinbo

(Technology and Engineering Center for Space Utilization,Chinese Academy of Sciences,Beijing 100094,China)

Analyzing the actual needs of the 1394 bus simulation tests are integrated into the distributed test system in the testing of aerospace embedded software, a front end system of 1394 Simulation Test Based on ARM&FPGA was proposed. After a brief introduction of the 1394 bus and distributed test system, the hardware and software of front End System of 1394 simulation tests are designed and implemented, and then the distributed test system is built. The result of the test shows that the 1394 simulation test front end could meet the sending and receiving timing requirements of the 1394 isochronous data and asynchronous data packages, and successfully applied to a spacecraft software third party evaluation.

IEEE Std 1394;ARM;FPGA;distributed systems

2015-09-14;

2015-10-20。

国家重大专项载人航天应用系统软件第三方评测 (Y5181021RN)。

苏 宇(1985-),男,吉林长春人,硕士,助理工程师,主要从事高可靠软件测试与验证,嵌入式系统开发方向的研究。

1671-4598(2016)03-0035-05

10.16526/j.cnki.11-4762/tp.2016.03.011

TP39

A