通用高速数据采集及测试平台设计

2016-11-17张兴成阎跃鹏

刘 谋,孟 真,张兴成,唐 璇,阎跃鹏

(中国科学院微电子研究所,北京 100029)

通用高速数据采集及测试平台设计

刘 谋,孟 真,张兴成,唐 璇,阎跃鹏

(中国科学院微电子研究所,北京 100029)

在图像和雷达等信号处理领域中,一个系统往往需要多块信号处理板进行协同工作,为了实现各个电路板之间的高速数据传输和通信,设计出了一种新型高速数据采集测试平台;平台采用64B/66B编码,同时兼容8B/10B编码,使用光纤作为传输介质,采用高性能FPGA为处理器实现高速数据收发;测试证明,采用64B/66B编码方式的平台相较于采用8B/10B编码方式的平台能够在大幅提高传输效率的同时减少数据冗余率;该平台设计通用性强,提高了通信速率的同时简化了外围线路的复杂性,可以为超高速数据采集提供更为高效的硬件支撑,并已得到了广泛的应用,具有较强的实用性。

高速数据采集及测试;64B/66B编码;8B/10B编码;收发器

0 引言

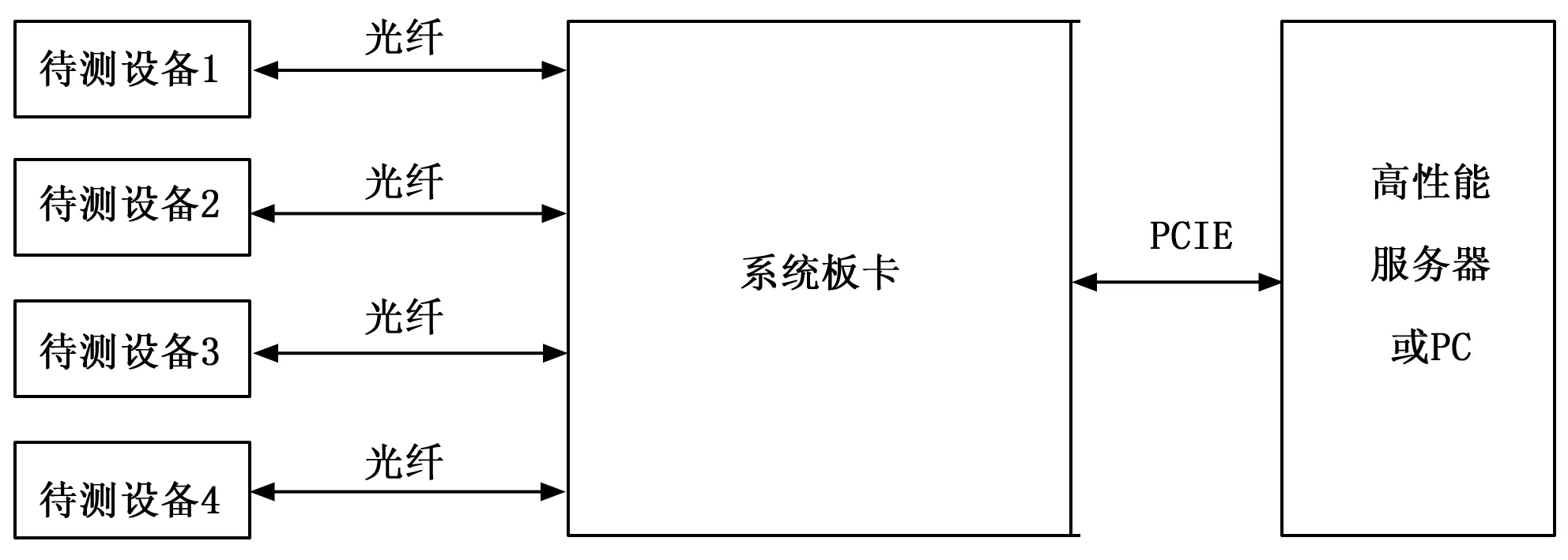

图1 测试系统总体架构

在图像系统、雷达信号处理等领域,经常涉及对高速信号数据进行采集和传输,以便进行后续数据处理,这就对器件选择、电路结构和系统调试提出了很高的要求。目前,高速接口技术发展迅速,速度不断提高,由原来2.5 Gbps每通道,提高到现在的10.312 5 Gbps每通道。64B/66B编码因为传输速度快、效率高成为高速传输的优选编码方案,例如应用越来越广的万兆网通信等;8B/10B编码虽然效率较低,传输速率相对不高,但是作为已经成熟应用于SATA、PCI-E、USB等的编码方案,在一定时期内,也有其存在的意义,并且采用其高速接口,可以大大简化外围电路设计。因此,本文设计了一种主要要采用64B/66B编码,同时兼容8B/10B编码的通用硬件平台,充分利用了高速传输的优点,用途非常广泛[1-2]。

1 采集及测试平台系统架构

数据测试系统板卡总体图1所示。数据的处理模块为一款高性能的FPGA处理器,通过内嵌的高速处理IP核与SFP+相连,具体采用何种协议,与测试信号的速度和协议有关,并根据传输速度和波长来选择光模块;板卡上带有DDR3存储器组,最大可以缓存2G字节的数据;板上预留PCIE接口,可以插入服务器中或者高性能PC中进行更深入的测试处理。测试人员通过高性能PC或者服务器,可以得到更加直观的测试结果,也可以实现对多块数据测试系统板卡控制,使板卡之间协同工作。

测试平台如图2所示,待测设备通过光纤连接测试板卡,采集及测试平台支持多路输入多路输出,可以使多路信号的同时进行采集和测试,灵活度和性能均有大幅度的提升。

图2 整体测试平台搭建

2 采集及测试平台编解码结构

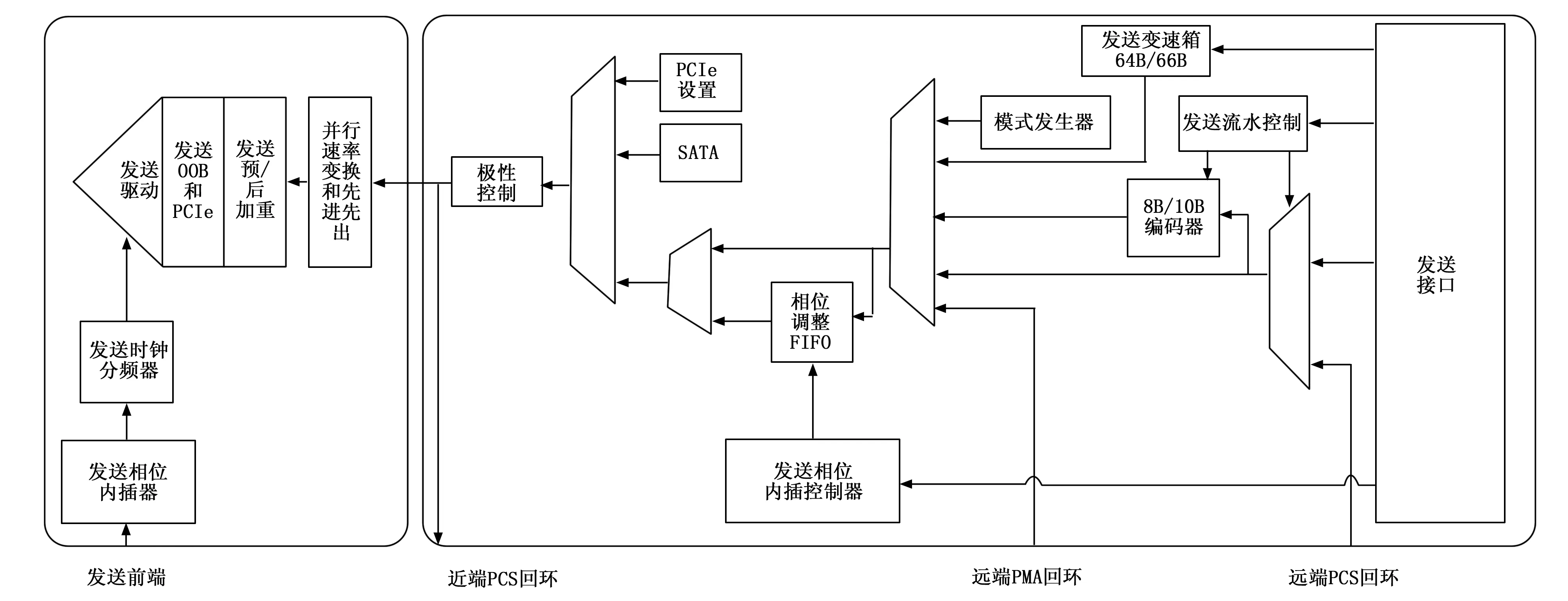

该平台采用64B/66B编码,同时兼容8B/10B编码。每个收发器包含一个独立的发射器和一个独立的接收器。从结构上看,这些高速接口主要包括三级层级结构:收发前端、物理层编解码部分和收发逻辑接口[4]。

图3给出了发送器的结构图。

发送前端包括了时钟管理和并串转换器,可以支持多种驱动负荷,通常还带有转换的预加重部分。时钟管理器管理各种时钟操作,包括时钟分频,相位调整等。

收发器的物理层级都是由一个的物理编码子层(physical coding sublayer,PCS)和一个物理介质附属(physical media attachment,PMA)组成。

编码模块可以实现64B/66B编码和8B/10B编码。发送变速箱可以将64B/66B编码增加一位扰码变为64B/67B编码,其核心都是64B/66B编码。在8B/10B编码的情况下,编码模块内还可以完成PCIE和SATA等专用协议。

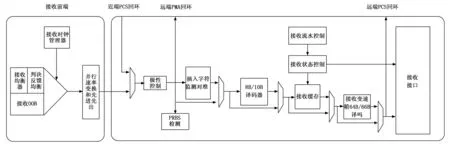

图4给出了接收器的结构图。

与发送器相对应,接收线路接口中包括差分接收器,接收均衡器,接收OOB,还可能包括有源或者无源均衡电路。时钟管理器管理各种时钟操作,包括时钟倍频,时钟恢复,并且有时钟修正和通道绑定的结构,修正发送时钟和接收时钟之间的偏差,同时也可实现多通道间的歪斜修正。插入字符监测对准将接收的数据对齐到合适的字边界。可以使用不同的方法,从自动检测和对齐特殊的预留比特序列(通常也称作comma字符),到用户控制的比特调整。在接收数据被提取之前,暂时保存数据。在需要时钟修正的系统中,接收缓存是必须的。与发送向对应的还有可调的解码器,将64B/66B编码方式和8B/10B编码方式进行相应的解码。

3 系统软件设计

3.1 系统程序架构

系统程序设计如图5所示。

图3 发送器结构图

图4 接收器结构图

图5 系统程序架构

外部命令包括采集开始设置、采集结束设置、系统复位。采集开始设置通知系统开始采集数据;采集结束设置为强制结束此次采集的命令;系统复位为当系统遇到未知状况时,进行复位的操作。

系统对采集的数据进行分析,如果瞬态数据量大,可以将数据通过ddr3读写控制器写入板上自带的大容量数据存储器中,数据分析时,可以对待测系统发送数据反馈命令,使其暂缓发送,对数据进行测试后,可以根据数据的分析结果对待测系统给出反馈控制。进而完成对待测系统数据收发和控制功能。

3.2 收发器程序设计

收发器的程序设计为整个软件系统架构设计的重点,其关系到数据的收发是否正确,对整个系统的可靠运行,起着至关重要的作用。收发器程序设计架构如图6所示[5-6]。

图6 收发器程序架构

在发送模块内部, 输入并行数据在发送缓存中进行缓存,发送编码器从发送发送缓存中读取数据进行数据编码,编码完成后将数据送给串化器,串化后的数据从FPGA 管脚送出。

接收模块按照与发送模块相反的流程执行,解串器将数据进行串并转化,转化后的数据进行数据译码,译码过程中,时钟数据恢复功能可以将数据进行对准,对准后的数据存入接收缓存器中。

为了保证收发模块能够稳定的运行,FPGA外部需要高精度的差分晶振提供时钟源,使收发器内部的时钟管理器模块能够给串化器和解串器提供高精确度的时钟,使时钟数据恢复模块能够准确的修正发送时钟和接收时钟之间的偏差,确保数据的接收。

4 试验结果与分析

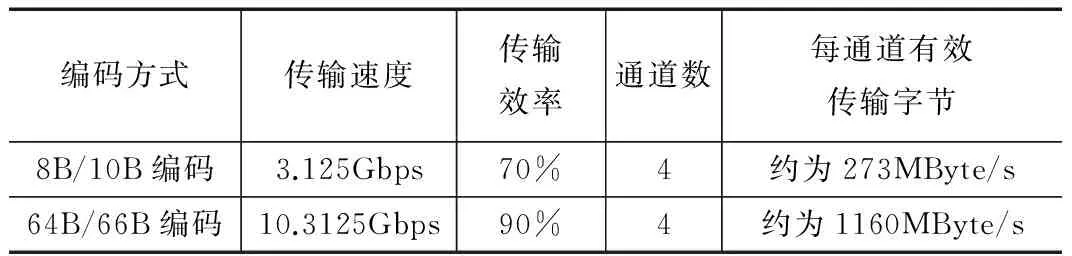

本系统板卡目前以应用与图像数据测试和雷达数据测试领域,测试结果如表1所示。

表1 不同编码方式的测试结果

应用于图像采集测试时,图像为彩色图像,每个像素3个字节,1080P图像的大小为约为6.3 M字节,4 k图像大小约为48 M字节,当用8B/10B编码方式时,可以同时对4个不同信号源的1080P图像进行采集测试,帧频为每秒25帧。而采用64B/66B编码时,不仅可以采集测试帧频更快的1080P图像,还能采集测试4 k图像,帧频甚也可以达到每秒20帧以上。

应用于雷达数据采集测试时,应用于中频采集的高精度ADC芯片一般为16位采样,当用8B/10B编码方式时,用于中频采样的ADC采集时钟最大速率约为135 M,带宽约为60 M左右,局限性较大,而采用64B/66B编码时,用于中频采样的ADC采集时钟最大速率可以达到550 M,带宽可以达到270 M左右,大大扩展了应用场合。

由以上评估能够说明64B/66B编码快,效率高,远远优于8B/10B编码;同时平台也兼容8B/10B编码,应用更加广泛。

5 结论

综上所述,高速传输协议,在技术上具有共同点,又有不同点。本文在深入研究高速传输协议的基础上,构建了主要以64B/66B编码为主,兼容8B/10B编码的数据采集及测试平台,目前该平台已应用于图像、雷达,软件无线电,软件定义网络等多种数据采集及测试场合。通过实际验证, 所构建采集及测试平台工作性能稳定可靠,运行良好。

[1] Luo, Y.-B. Chiueh, T.-D. Timing and data recovery circuit for high-speed optical storage drives[J]. Circuits, Devices and Systems, IEE Proceedings : 79-81.

[2] Krstic, A. Kwang-Ting Cheng, Chakradhar, S.T. Testing high speed VLSI devices using slower testers[A]. VLSI Test Symposium, 1999. Proceedings. 17th IEEE[C].276-277.

[3] 敖志刚,解文彬,胡 琨,等.新一代以太网的结构模型和并行传输设计[J].电子科技大学学报 第42卷:773-777.

[4] ug476_7Series_Transceivers User Guide [DB].Xilinx Corporation : 93-286.

[5] 轻松实现高速串行I/O[M]。Abhijit Athavale, Carl Christensen : 20-22.

[6] 高速串行接口的编码技术[EB].移动通信网.

Design of High Speed Data Acquisition and Test Platform

Liu Mou, Meng Zhen, Zhang Xingcheng, Tang Xuan, Yan Yuepeng

(Institute of Microelectronics of Chinese Academy of Sciences, Beijing 100029, China)

In the field of image and radar signal processing, a system is usually required to work together with multi signal processing board. In order to realize the high-speed data transmission and communication between the various circuit boards, a new high-speed data acquisition and testing platform is designed.The platform uses 64B/66B encoding, and is compatible with 8B/10B encoding, uses optical fiber as the transmission medium, uses high performance FPGA to achieve high-speed data transceiver. The result of test provides that the platform using of the 64B/66B encoding compared to the platform using of the 8B/10B encoding greatly improves transmission efficiency and significantly reduces data redundancy at the same time. This platform has a strong universality and improves the speed of communication. It also can simplify the complexity of the peripheral circuit. Therefore, the platform can be used to provide a more efficient hardware support for ultra high speed data acquisition,and have strong practicability.

high speed data acquisition and testing; 64B/66B coding method; 8B/10B coding method; transceiver

2015-09-08;

2015-11-06。

国家科技重大专项子课题(2013ZX02502-001); 国家自然科学基金项目。

刘 谋(1983-),男,河北饶阳人,工学硕士,助理研究员,主要从事高速信号处理方向的研究。

1671-4598(2016)03-0018-03

10.16526/j.cnki.11-4762/tp.2016.03.006

TP3

A