基于RocketIO 高速串行回环通信的实现

2013-03-13苏秀妮李英利

苏秀妮,李英利

(西安电子科技大学 电子工程学院,陕西 西安 710071)

随着信息流量的增长,当今社会对信息的处理速率提出了较高的要求,尤其是图像、视频等多媒体领域,促使了高速通信行业的迅速发展,同时也使高速可靠通信成为当前的研究热点[1-2]。国内外高速收发器的快速发展推动了高速传输行业的迅猛变化。当前国外高速传输速率已达到THz 级别,而在国内仍处于MHz 时国外已实现了64 GHz[2-3],目前国外可普遍实现100 GHz 以上的传输速率,采样速率也已达到20 Gsample/s。虽国内在此方面的应用也较多,但可实现的速率还远未达到要求,其中可实现1 Gbit·s-1速率占多数。因此国内在该方面的发展仍有较大的提升空间。鉴于此,文中提出一种基于RocketIO 高速串行回环通信的实现,该设计有助于高速串行通信的实现,且具有速率快、可靠性高及开发容易等优势。

1 高速串行回环

1.1 高速串行收发器

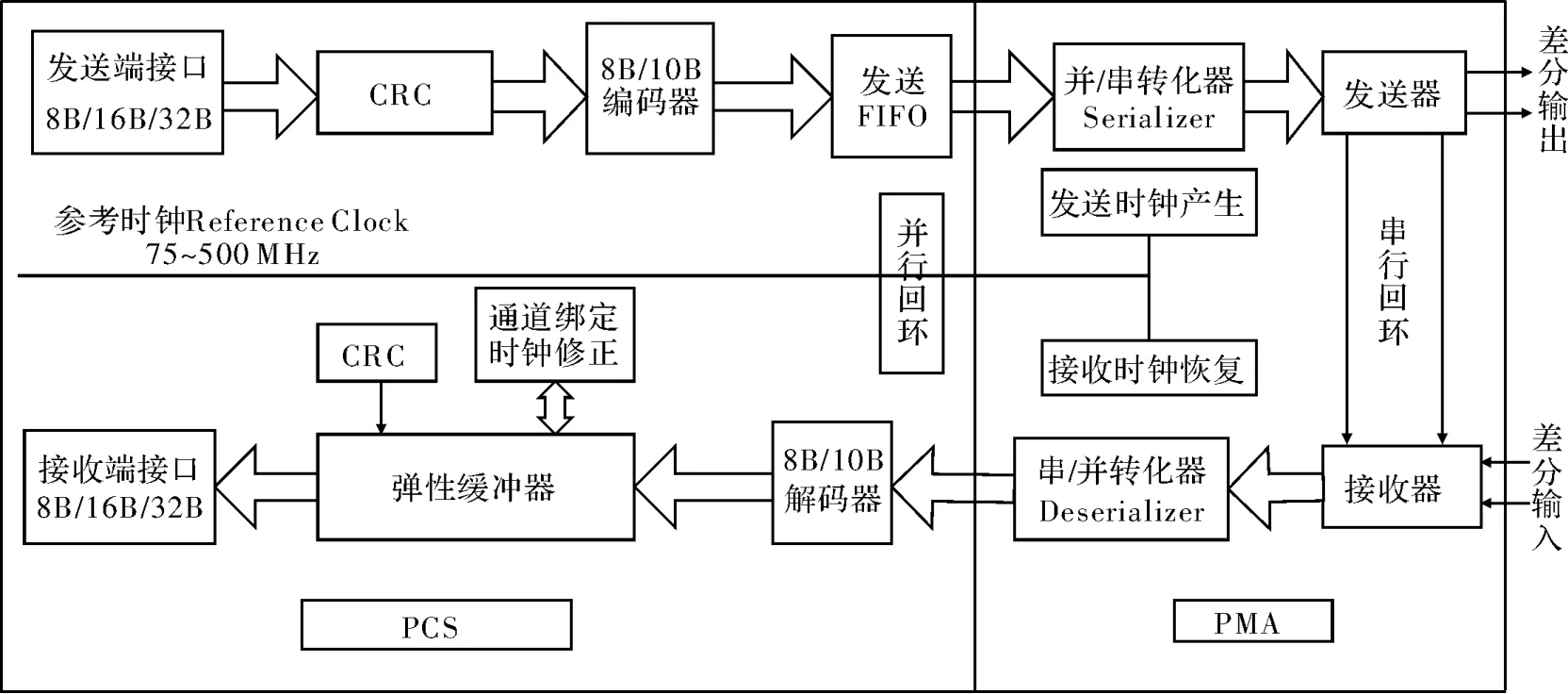

高速串行回环是基于RocketIO 高速串行收发器,回环是高速串行收发器本身携带的。RocketIO 高速串行收发器是Xilinx 集成在VirtexII pro 以上系列的专用高速串行收发器,可实现Gbit·s-1的传输速率,支持多种协议,且应用广泛[3]。其主要组成如图1所示。

如图1 所示,RocketIO 高速串行收发器主要由物理编码层(PCS—Physical Code Subplayer)和物理媒介层(PMA—Physical Media Acess Physical)构成,PCS 层包括周期冗余检测(CRC—Cyclic Redundancy Check)、8B/10B 编码、发送FIFO、8B/10B 解码以及用于通道绑定和时钟修正的弹性缓冲器等主要模块;PMA 层主要包括串行转换、差分接收器、并串转换以及接收时钟恢复等模块。发送器先经CRC 按照一定的算法规则设计的校验码插入欲发送的数据中,然后进行8B/10B编码,将数据输入到发送FIFO 中,再经过并串转换后,最终以差分串行数据流的格式输出。接收器接收到该差分串行数据流后,先进行串并转换,将其转换成并行数据,再进行8B/10B 解码,将数据流对齐后输出该并行数据[4]。

以上是RocketIO 的工作原理,其中PCS 和PMA将该收发器分成2 个回环,即图1 所示的并行回环和串行回环。

图1 高速串行收发器结构图

1.2 回环概述

回环模式是收发器的专有设置,数据由发送端输入,然后从接收端输出,由于数据流向路径从发送端到接收端是一个回环,故称为回环模式。正如发送器发送数据,接收器接收数据,只是发送器和接收器在同一个收发器中,故数据路径恰好为一个回环。每个收发器内部均有专用的PRBS 生成器和检测器来检测错误[5]。由于一个RocketIO 中包含有2 个GTX 收发器,故共有4种回环。图2 给出了一个GTX 中的4 种回环。

图2 GTX 中的4 种回环

4 种不同回环的划分是由所处的位置决定的,对于一个收发器而言,由TX-PCS 和RX-PCS 构成的是近端PCS 回环,即图2 中所示的①路径。由TXPCS、RX-PCS、TX-PMA 和RX-PMA 构成近端PMA回环,即图2 中所示的②路径。物理位置较远的收发器的TX-PMA、RX-PMA 和第1 个收发器的PCS、PMA 构成的回环称为远端PMA 回环,即图2 中所示的③路径。物理位置较远的收发器(第2 个收发器)的TX-PCS、RX-PCS 和第1 个收发器的PCS、PMA构成的回环称为远端PCS 回环,即图2 中所示的④路径。其中远端的2 种回环均与第1 个收发器的发送端和第2 个收发器的接收端相连,第1 个收发器的接收端和第2 个收发器的发送端相连。

近端PCS 回环主要是验证第1 个收发器PCS 层的通信状况以及该层的参数变化对通信结果的影响;近端PMA 主要是验证第1 个收发器的通信过程以及该收发器参数变化对通信结果的影响;同理远端PCS回环、远端PMA 作用与近端PCS 回环、近端PMA 回环作用相同。

2 回环实现

2.1 回环实现原理

不同的回环测试不同的模块,可通过设置LOOPBACK 端口来选择所需回环,LOOPBACK 是一个3 bit宽度的端口,可提供8 种组合,但可用组合仅5 种,其余组合均是保留。以Xilinx 的FPGA 为平台,以Virtex5系列的FXT 为对象,用ISE 实现高速串行收发器的不同回环,用Modelsim 对其进行仿真。实现这4种回环的原理如图3 所示。

图3 回环实现原理

图3 中,1 个RocketIO 收发器包含两个收发器,可以实现4 种不同的回环,回环设计可根据指标要求设计满足要求的参数;数据产生模块提供仿真数据,数据接收模块是接收到的RocketIO 输出数据;校验模块指示接收到的数据与产生的数据是否相同。在4 种回环的实现中,数据产生模块提供的数据是Matlab 产生的10 000 个随机二进制数,数据接收模块将收发器输出的数据放在指定的文件夹中,校验模块将数据接收模块接收到的数据和数据产生模块产生的数据进行比较,当发现两个模块的数据不同时,有相应的端口和内容指示,便于观察和定位错误信息。

2.2 回环仿真实现

该设计工作在参考时钟为250 MHz 的速率下,回环实现结果中各个端口的意义如下所述,REFCLK_N_IN 和 REFCLK_P_IN 是差分时钟输入端口;LOOPBACK0_IN 和LOOPBACK1_IN 分别是通道0、1回环种类选择端口;TXDATA0 和TXDATA1 分别是通道0、1 的并行数据发送端口;RXDATA0 和RXDATA1分别是通道0、1 的并行数据接收端口;RXN0_IN 和RXP0_IN 是通道0 的差分输入端口,RXN1_IN 和RXP1_IN 是通道1 的差分输入端口;error0_count 和error1_count 分别是指示通道0、1 接收的数据与发送的数据相比较,数据不相同的个数。

2.2.1 近端PCS 回环实现

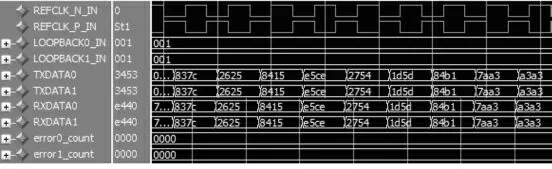

选择近端PCS 回环时,将LOOPBACK 设置为001。近端PCS 回环是在并串转换和串并转换之前的回环,如图2 中①所示路径。图4 是近端PCS 回环的仿真结果。

图4 近端PCS 回环实现结果

图4 中,LOOPBACK 为001,即选择的回环是近端PCS 回环。从仿真结果可看出,error0_count 和error1_count 的值均为0,说明接收到的数据和发送的数据相同,并无不同情况,故接收端可以正确地接收发送端发送的并行数据,即RXDATA 接收到的数据应和TADATA发送的数据相同,不会出现误码和移位现象。

2.2.2 近端PMA 回环实现

选择近端PMA 回环时,将LOOPBACK 设置为010。近端PMA 回环发送端发送的数据是并行数据,然后经并串转换将其转换成串行数据输出,接收端接收该串行数据,并将其转换为并行数据输出,如图2所示的②路径。图5 是近端PMA 回环的仿真结果。

图5 近端PMA 回环实现结果

图5 中,LOOPBACK 为010,即选择的回环是近端PMA 回环。其仿真结果与近端PCS 回环实现结果相同。

2.2.3 远端PMA 回环实现

选择远端PMA 回环时,将LOOPBACK 设置为100。远端PMA 回环是由近端PMA 回环、并串转换以及串并转换组成的回环,如图2 所示的③路径。图6是远端PMA 回环的仿真结果。

图6 远端PMA 回环实现结果

图6 中,LOOPBACK 为100,即选择的回环是远端PMA 回环。从仿真结果可知,error0_count 和error1_count的值为0,差分接收端口接收到的数据流和差分发送端口发送的数据流相同,接收端也可正确地接收发送端发送的并行数据,即RXDATA 接收到的数据应和TADATA 发送的数据相同,同样不会出现误码和移位现象。

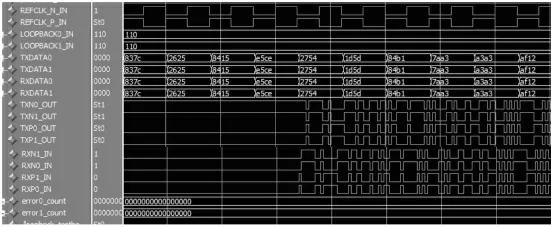

2.2.4 远端PCS 回环实现

选择远端PCS 回环时,将LOOPBACK 设置为110。远端PCS 回环是由远端PMA 回环、并串转换以及串并转换之后的部分组成的回环,该回环包含两个收发器。如图2 所示④路径。图7 是远端PCS 回环的仿真结果。

图7 远端PCS 回环实现结果

图7 中,LOOPBACK 为110,即选择的回环是远端PCS 回环。仿真结果与上述3 种回环相同。

从仿真结果看,以上各个回环均实现无误码和移位,说明该设计有较高的可靠性,其主要是因为该设计是基于专用高速收发器RocketIO 的,该收发器已被验证能够实现高可靠性,但是在高速串行通信中,RocketIO收发器要依据需要设计,实际中并非发送器和接收器均要使用,该系统的误码率与前端的信号提供有较大的关系,故高速串行回环能够实现的误码率是高速串行通信可实现误码率的最佳情况。

3 结束语

文中设计了一种基于RocketIO 高速串行回环通信的实现方法,RocketIO 高速串行回环不仅在高速串行通信开发阶段有助于熟悉高速收发器的工作原理,并在调试阶段有助于检查和定位错误,促进了高速串行通信的开发,且可靠性高、便于开发。

[1] 马腾飞,吴志勇.基于XAUI 协议的10Gb/s 光纤通信系统[J].计算机工程,2010,36(17):264-266.

[2] 欧阳科文,黎福海.基于RocketIO 的SATA 物理层高速串行传输实现[J].计算机测量与控制,2009,17(5):937-939.

[3] Xilinx Corporation.Virtex-5 FPGA user guide[M].USA MA:Xilinx Corporation,2010.

[4] Xilinx Corporation.Virtex-5 FPGA RocketIO GTX transceiver user guide[M].USA MA:Xilinx Corporation,2009.

[5] ANNE M,AKIRA K.External loopback testing experience with high speed serial interfaces[C].Guangzhou:International Test Conference,2008.