高速高精度ADC动态参数评估系统的设计与实现

2016-11-17虞致国顾晓峰

黄 朴,冯 洋,虞致国,何 芹,顾晓峰

(江南大学 电子工程系物联网技术应用教育部工程研究中心,江苏 无锡 214122)

高速高精度ADC动态参数评估系统的设计与实现

黄 朴,冯 洋,虞致国,何 芹,顾晓峰

(江南大学 电子工程系物联网技术应用教育部工程研究中心,江苏 无锡 214122)

高速高精度模数转换器(ADC)广泛应用于信号处理领域,其动态性能直接决定系统性能的优劣;由于实际使用的芯片与设计的额定指标间会存在偏差,有必要评估ADC的实际动态性能;基于FPGA及Labview实现了一个低成本、高可靠性的高速高精度ADC性能评估系统;系统由底层控制待评估ADC子卡,提供精确的采样样本;采用异步FIFO进行数据缓存, DMA方式优化数据存储;Labview定义通信模块,结合Matlab测试脚本完成动态参数测试;最后使用ADI公司的AD9467进行了测试验证;实验结果表明,该系统运行稳定,与datasheet相比,参数误差不超过1.89%,达到了IEEE Std 1241-2000的测试标准,降低了测试系统构建难度和成本。

模数转换器;动态参数;模块化;数据采集

0 引言

随着微电子技术的发展,模数转换器(Analog-to-digital Converter, ADC)经历了由低速低精度向高速高精度发展的过程。高速高精度ADC在仪器仪表、无线通信、雷达信号处理、航空航天等领域的应用极其广泛[1],对其进行性能测试十分重要,ADC的动态特性更是决定系统性能的重要因素[2-5]。目前,高速高精度ADC性能测试的方案大都基于高性能的自动化测试设备(ATE)[6],存在测试成本高、测试难度大的问题,因此,构建实用的ADC性能测试系统来快速准确地评估高速高精度ADC的动态性能参数,具有重要的工程实践价值[7-9]。

1 ADC的动态性能参数

1.1 动态性能参数与测试原理

ADC的性能测试分为静态测试和动态测试。静态测试法有其局限性,不能准确地反映ADC的动态特性[10]。动态参数一般包括信噪比(SNR)、总谐波失真(THD)、无杂散动态范围(SFDR)、有效位数(ENOB),主要采用快速傅里叶变换(FFT)法进行测试,即对在时域内采集的一组正弦信号的采样信号进行FFT变换,然后从得到的傅里叶频谱中提取有关信息,对ADC的动态特性在频域上给出全局性的描述。主要动态参数[11]的计算公式如下:

(1)

(2)

(3)

(4)

(5)

式中,Psignal、Pnoise、Pharmonic分别为信号功率、噪声功率及谐波功率。

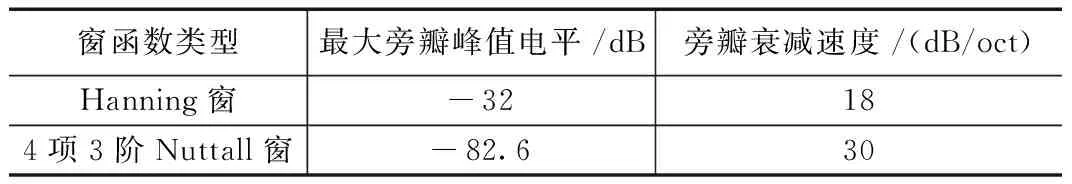

1.2 窗函数的选择

利用FFT法测试ADC动态参数时很难做到相干采样和整周期截断,需要使用合适的窗函数对信号截断。矩形窗是最简单的窗函数,若将其改为两端平滑的窗函数来处理时域数据,可显著减少采样数据点的非连续性效应,减弱频谱泄漏[12]。窗函数种类很多,主瓣宽度、最大旁瓣衰减水平和旁瓣衰减速度是描述窗函数的3个基本特性。但是,这3个基本特性不可能同时得到优化,因此不同的窗函数抑制频谱泄漏的效果不同。表1给出了本文使用的各项窗函数的旁瓣特性。

表1 Hanning窗和4项3阶Nuttall窗函数的旁瓣特性

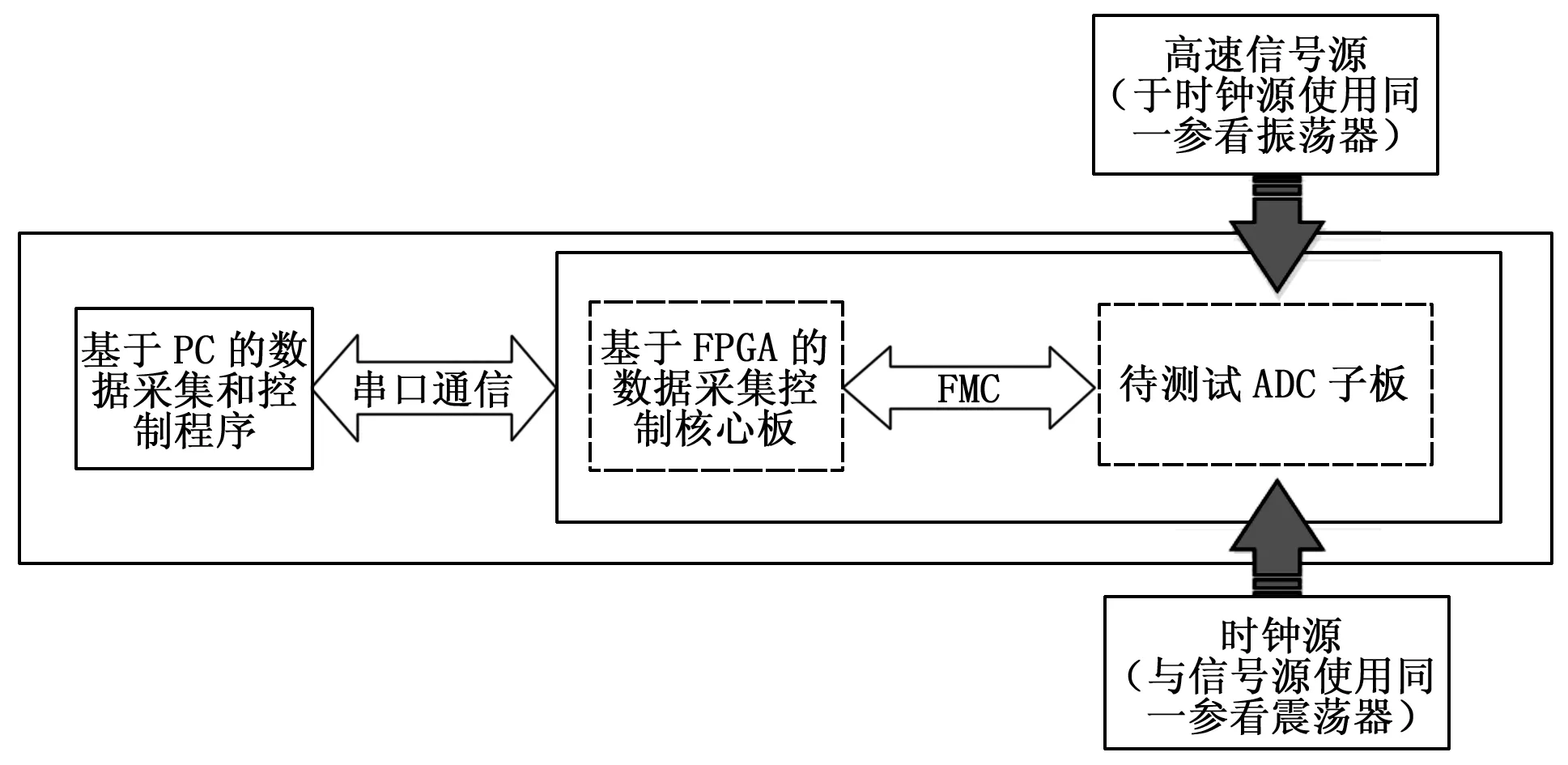

2 评估系统整体结构设计

如图1所示,高速高精度ADC动态参数评估系统主要由待评估ADC子卡、基于FPGA的数据采集控制核心板、基于PC端Labview的数据采集和控制端、信号发生器等4个部分组成。其中信号发生器包括时钟源与同源信号源,对接相应频率的滤波器以保证信号的高纯度。

图1 高速高精度ADC动态参数评估系统

信号发生器产生一幅度略小于ADC满测试量程的正弦波,作为采样信号输入到待评估ADC子卡的SMA (Sub-Miniature-A)接口;采样信号滤波后到达ADC模拟信号输入端,通过模拟输入电路转换为差分信号;然后进行模数转换,经FIFO (First In First Out)缓冲后利用DMA (Direct Memory Access)通道输出至DDR3 (Double Data Rate 3)内存进行保存;最后送入PC机的Labview控制测试端,进行动态特性测试。PC机和FPGA核心板采用串口进行通信,可满足数据传输和通信控制需求。不同的ADC芯片性能测试,均采用同一个数据采集硬件平台。

本文选用XC7K325T芯片作为控制核心。该芯片为Xilinx公司生产的高性能嵌入式微处理器,总线工作频率高达150 MHz,带有片内RAM,并配备DDR3、SPI (Serial Peripheral Interface)等丰富的外设。为验证系统性能,采用ADI公司生产的AD9467作为评估芯片,其采样率默认为250 Msps,转换精度高达16位。

3 数据采集与存储系统设计

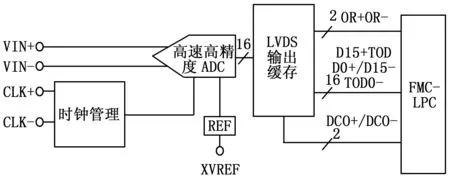

3.1 待评估ADC子卡设计

3.1.1 模拟输入电路

考虑到采用模块化方法构建系统,因此评估ADC动态参数时,待评估ADC子卡与通用核心板需要通过前端接口FMC进行连接,以减少ADC变更的影响。图2为待评估ADC子卡的功能模块示意图。最终输入到A/D芯片的是差分信号,包括电压差分信号和时钟差分信号,输出包括OR (Over_Range)、Data与DCO等3种差分信号。OR端占用2 bit,高低各1 bit,作为超出量程的标志信号;D端为16 bit的数据端,高低两路各8 bit;DCO端为时钟信号。采样信号是发生器产生的模拟输入信号,默认是电压输入,对ADC来说,电流输入可选。

图2 待评估ADC子卡功能模块

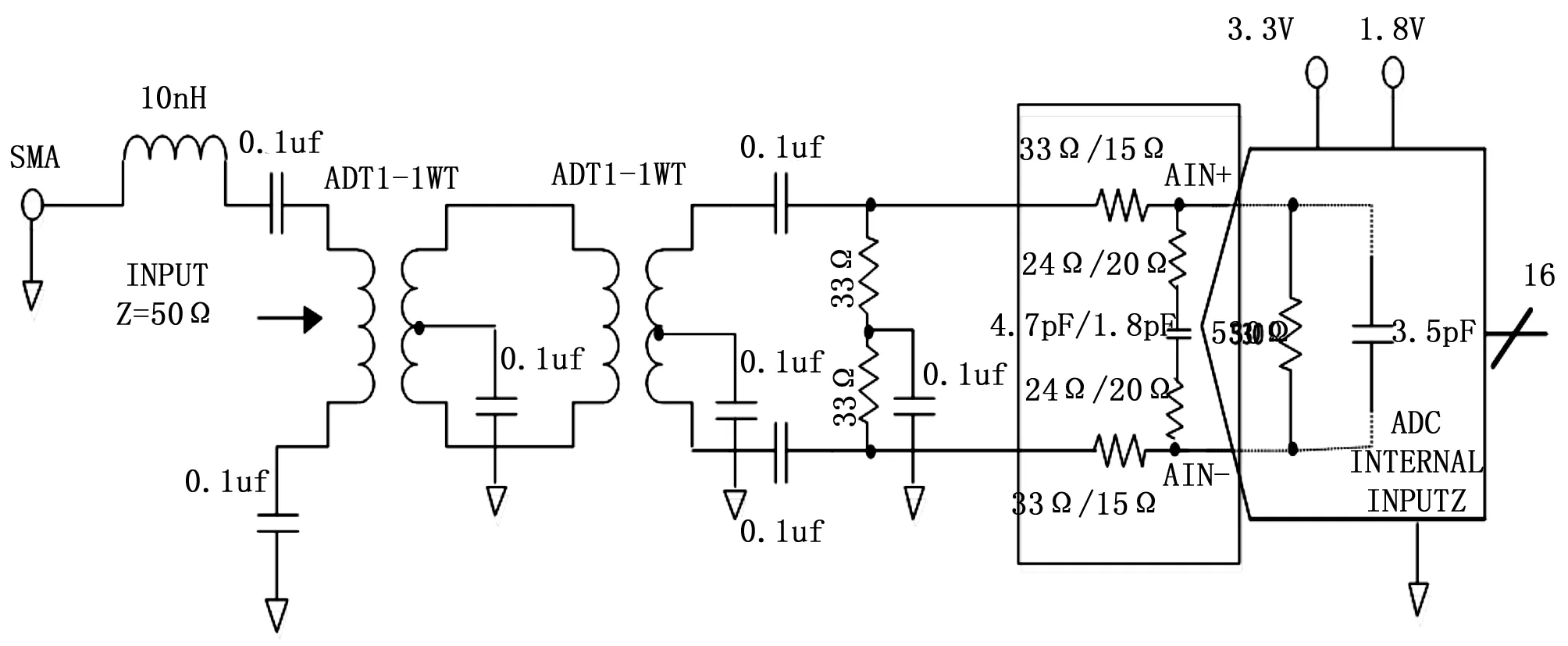

在实际的信号采样过程中,由于信号发生器只能产生单端信号,需要用到模拟输入电路进行差分变换。模拟输入电路是A/D芯片的信号缓冲区。电压模式模拟输入电路如图3所示,该模拟输入电路工作于0-300 MHz之间。

图3 电压模式模拟输入电路

不论输入信号频率多少,电路元件固有的噪声总会降低ADC的SNR,因此模拟电路利用变压器,通过提供高质量的高频输入耦合机制以解决噪声问题。另外,输入信号频率高达250 MHz,若只是用2个变压器,则寄生电容耦合会导致二次输出,最终结果是输出不对称,并且造成转换器的模拟输入及2阶谐波数字信号的扭曲。解决办法是在第一个级联(图3中的左边矩形)应用第二个变压器,通过提供额外的电流隔离来减少电容式直通的不平衡问题。

3.1.2 量化与编码

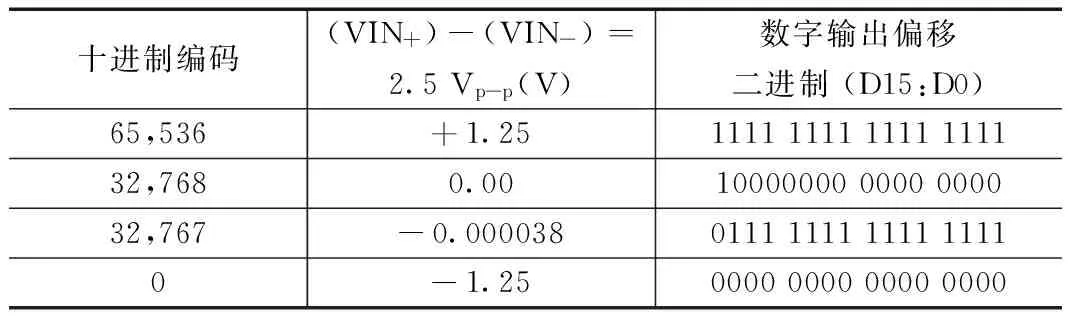

通常A/D转换经过采样后还需要进行量化、编码两个步骤。AD9467支持偏移码、补码、格雷码3种数据格式,默认情况下使用偏移码以保证转换后的量化电平始终大于0,具体可参考表2。

3.2 数据存储系统设计

3.2.1 数据存储系统设计

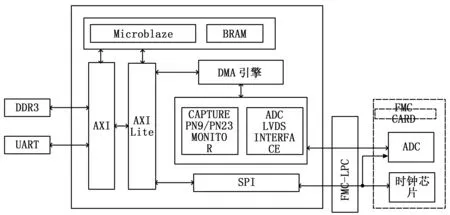

存储系统结构分为三部分:一是基于FPGA的存储控制模

表2 数字输出编码

块,二是FMC-ADC完成数据采集,三是存储单元DDR3,如图4所示。基于Micrlblaze的存储控制模块作为核心部分,一方面负责控制待评估ADC子卡的数据采集与存储,另一方面需要与基于Labview的测试控制端进行通信。待评估ADC子卡采集数据后,利用AXI-4协议总线完成数据交换任务,AXI-4总线速率可达150 MHz,而数据采集速率高达250 MHz,每秒钟产生250 M*16 b=4 Gb的数据,因此以低速总线完成数据交换成为构建存储系统的关键。为保证数据采集的实时性,应尽可能减少数据实时采集、预处理、存储和传输过程中的时间开销,需设计高性能的数据链路以实现高速采样数据的存储,故系统采用Xilinx高性能IP核DMA与AXI-4总线配合完成高速数据存储。存储介质为1 GB的DDR3,则对于16 bit的ADC来说样本空间可达400-500 M,足以应对各种评估算法的样本需求。

图4 数据存储系统整体结构

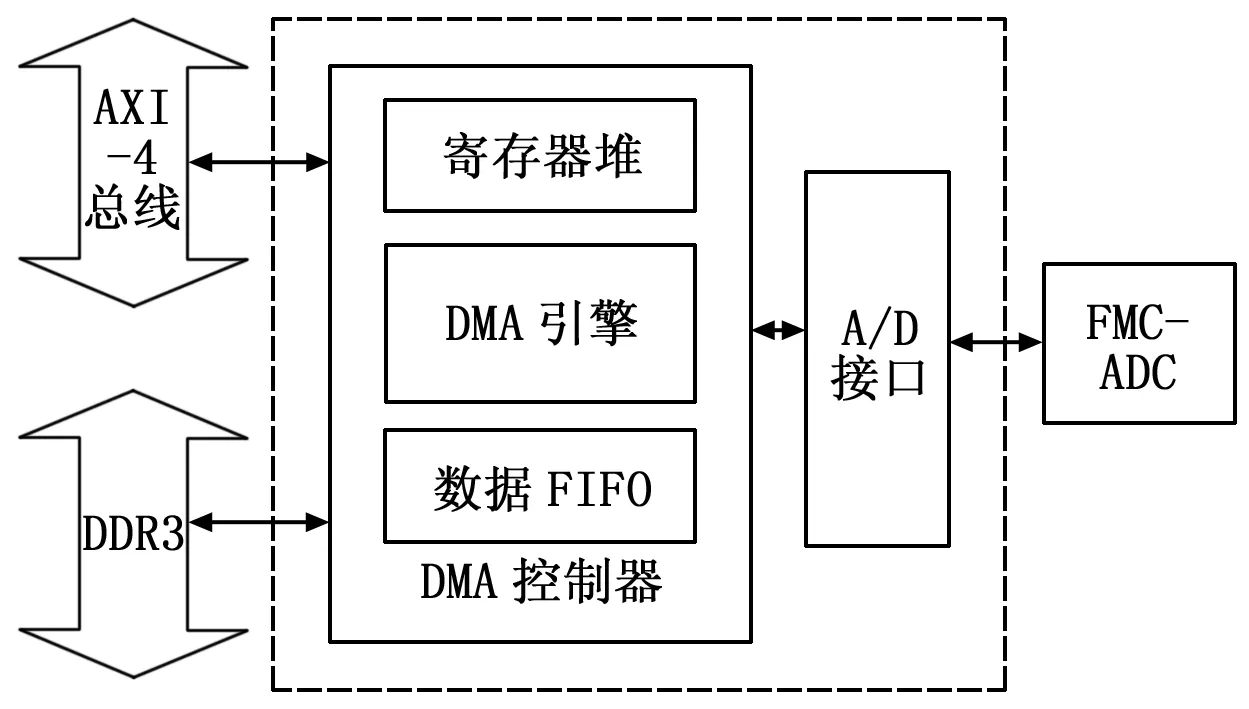

系统采用DMA方式实现数据存储,其结构如图5所示。数据存储路径为:模拟输入电路生成的两路模拟差分信号进入ADC,进行A/D转换后输出两路8位数字差分信号;信号通过Xilinx自带基本元件IBUFDS缓冲,经过一定的延迟后组合成16位数据;经过异步FIFO后转换为64位数据,通过DMA送入DDR3中。系统构建中需要注意,尽管DMA包含MM2S (Memory Map To Slave)、S2MM (Slave To Memory Map)双通道,但系统是由FMC-ADC获取数据存入DDR3中,所以只需开启S2MM通道。存在多个ADC时,只需为每个ADC添加各自的S2MM通道即可。

图5 DMA控制器结构

3.2.2 异步FIFO设计

考虑ADC接口模块通过FMC-LPC完成数据采集,经DMA通道送入DDR3,但由此引出一个问题:待评估ADC子卡采样时钟为高达250 MHz的外部时钟,而DMA控制器与系统总线时钟一致,仅为150 MHz,即数据传输需要经过异步时钟域。因此,为不丢失地跨时域传输数据,需利用异步FIFO进行数据缓存。

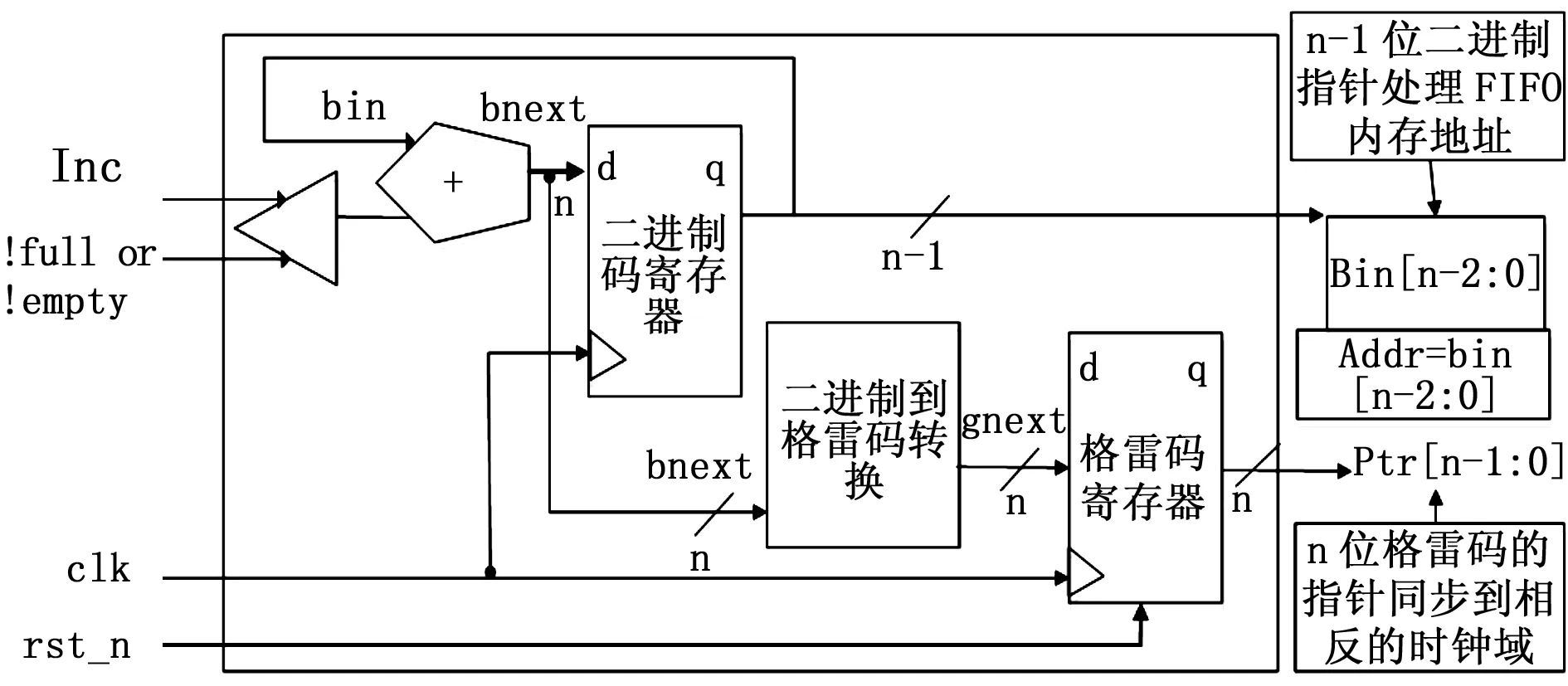

为解决跨时域传输造成的亚稳态,需要一个二进制到Gray码的转换电路,将地址转换为相应的Gray码,然后将Gray码同步到另一个时钟域进行对比,作为空满状态的检测。图6为基于FPGA实现的Gray码的转换电路示意图。

图6 Gray码转换电路示意图

使用Gray码解决了亚稳态问题,同时也带来另一个问题,即在Gray码域如何判断空与满。对于“空”的判断依然依据二者完全相等(包括MSB);而对于“满”的判断,由于Gray码除了MSB外,具有镜像对称的特点,当读指针指向7,写指针指向8时,除了MSB,其余位皆相同,不能说它为满。因此不能单纯地只检测最高位,在Gray码上判断为满必须同时满足以下3条:

1)wptr和同步过来的rptr的MSB不相等,因此wptr必须比rptr多折回一次;

2)wptr和rptr的次高位不相等;

3)剩下的其余位完全相等。

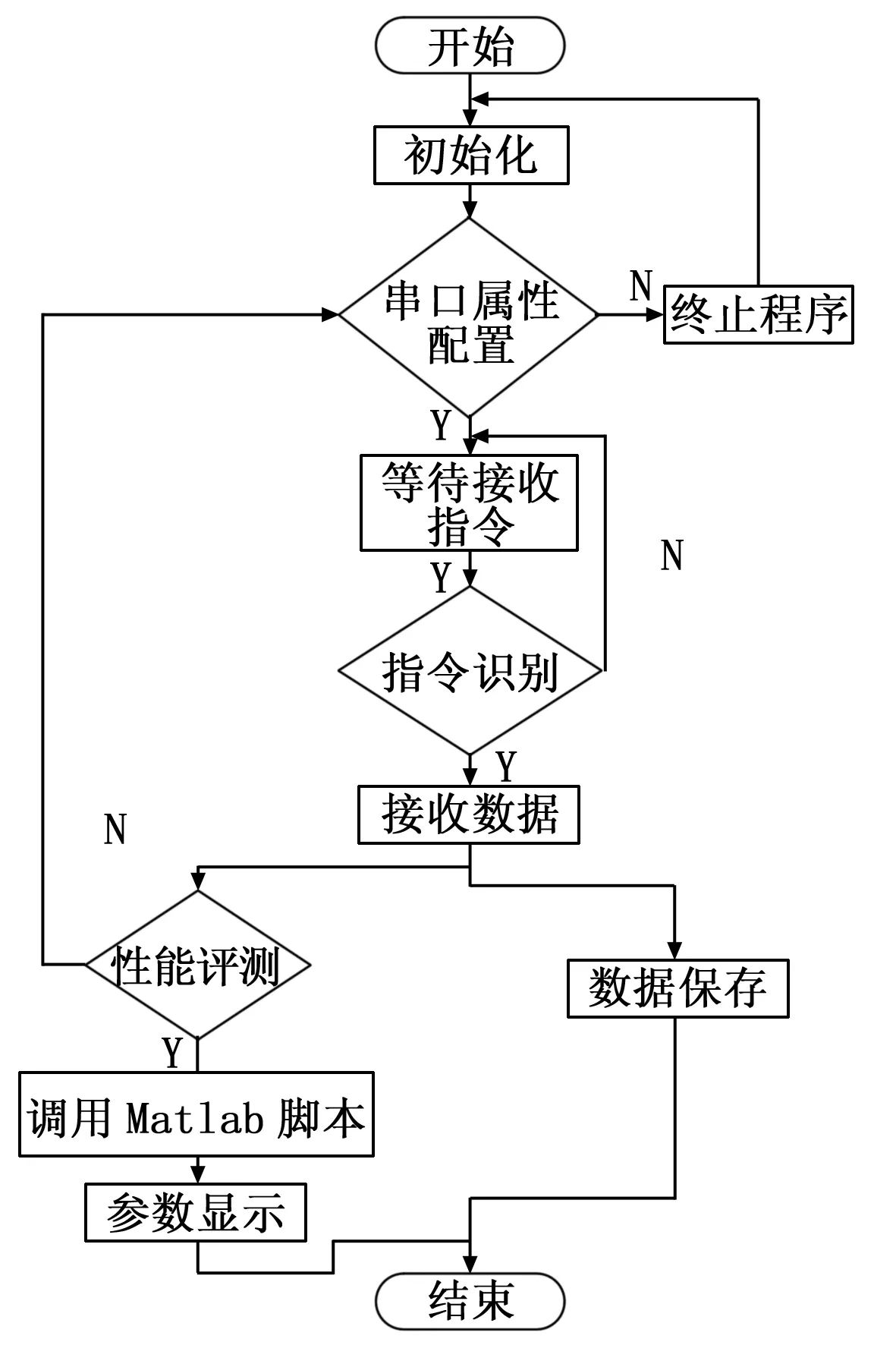

3.3 Labview控制测试端设计

采用Labview作为系统的控制测试端,与基于Microblaze的FPGA存储控制模块通过串口通信。ADC初始化成功,Labview端接收到返回的信息后,通过可视化界面发送指令给FPGA,开始数据采集与存储,并将采样数据由串口返回Labview端进行动态测试。Labview端动态测试提供多种算法选择,其控制流程如图7所示。

图7 Labview测试控制流程

其中,系统初始化运行时,CPU与PC端还未成功建立通信,直至串口参数配置完成。发送与接收指令均使用ASCII编码。通过PC端的Labview图形化界面控制系统的运行,如图8所示。界面左侧给出系统的控制参数及测试所得的各项ADC动态参数,包括SNR、SINAD、ENOB、SFDR、THD以及基波频率等。

图8 Labview测试控制端配置

此外,由于数据量大,为方便管理,控制面板提供保存数据至TXT文档以及保存频域波形的选项,可通过面板实现对历史数据的查询。

4 测试结果分析

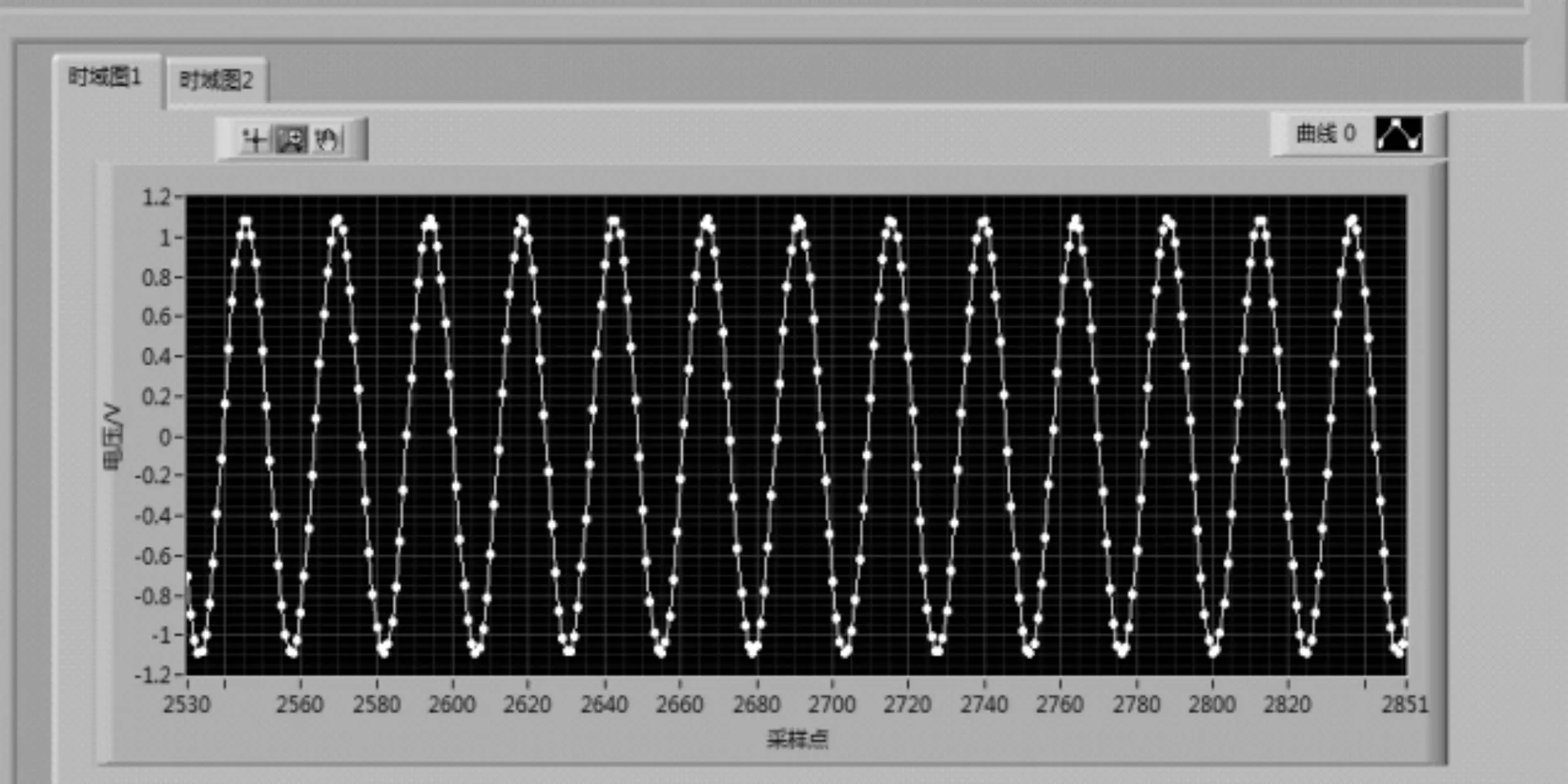

图9~10给出了输入信号频率10.3 MHz、电压幅值2.5 Vpp、Ain为-1 dBFs的测试结果,设置加窗函数部分为五项最大旁瓣衰减窗函数MSLD5[13],采集的样本空间大小为214=16K个样本点。理论上数据越多,测试结果越接近真实值。左下部分为与核心板的串口通信相关参数配置。电压对比部分输入信号置为2.5 V,但实际输入电压为2.23 V,实际输入电平为量程的89%,符合ADC的输入要求。

经过调试,该系统能够可靠并稳定运行。图9为采集数据的时域图,其中纵轴的电压幅值通过数字输出编码转换得到,横轴为样本点递增。可看出,电压幅值约为1.12 V,与设置相符;另外,图中以小圆点表明样本点,遍历样本点数与设置的样本空间大小一致。

图9 ADC测试时域图

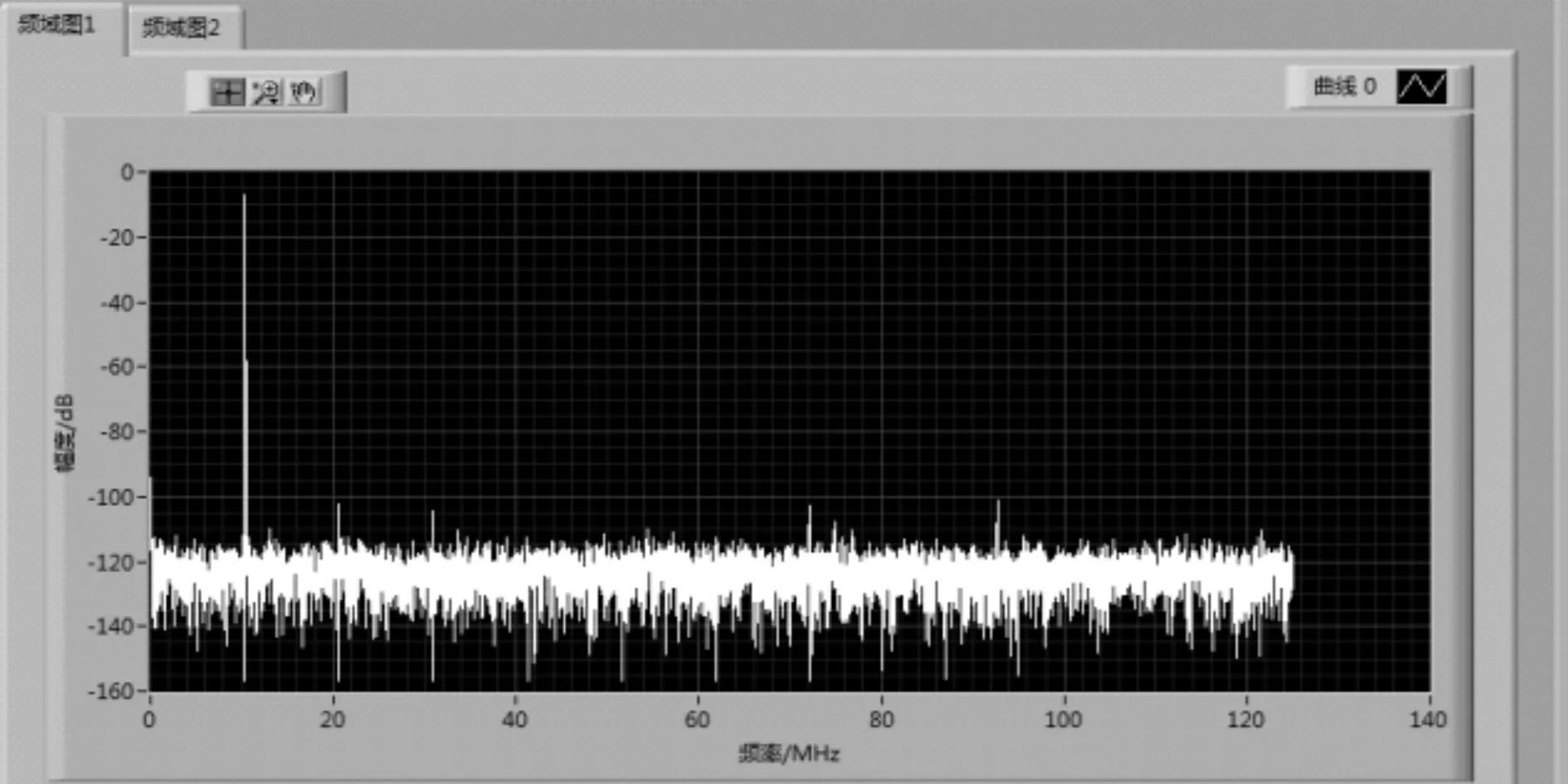

根据样本点可得到A/D芯片的频谱图,如图10所示。可以发现,得到的频谱图噪声基底较小,量化噪声集中在几条谱线上,其余为时基抖动、非线性失真等其他因素产生的噪声,能真实地反映ADC的动态特性。

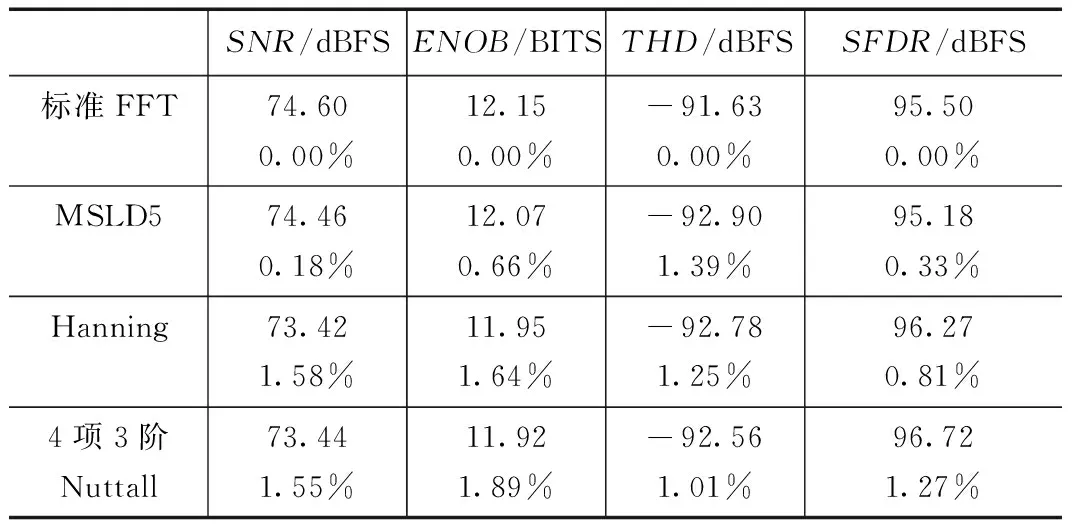

图10 ADC测试频域图

表4给出了基于同种加窗函数、输入信号不同频的动态参数测试结果以及与datasheet的数据误差,由于ENOB与SINAD是直接关联的,故测试结果只需给出其中一种参数即可。另外,datasheet的数据由高端专用ATE测得,等同于相干采样,可视作标准FFT算法值。观察表4可以发现:1)本系统利用3种加窗函数动态测试得到的结果与datasheet中给出的各参数非常接近,误差不超过1.89%;2)不同的窗函数间测试结果相近,系统能可靠并稳定地运行;其中加窗函数为MSLD5时,THD与SFDR结果不变,但SNR与ENOB的测试结果更加优秀。

表4 不同窗函数的测试结果

5 结束语

基于FPGA、Labview与待评估ADC子卡构建了一套高速高精度ADC的动态参数评估系统。系统为解决跨时域问题,利用异步FIFO进行缓存完成了高速数据采集;采用DMA方式控制高速数据流至内存,优化了数据存储;然后通过Labview界面定义了通信模块进行采集控制,并选用非相干采样下相应算法评估,能够在短时间内精确地评估ADC动态性能。实验结果显示,各项参数与标准FFT算法值相比误差不超过1.89%,符合IEEE Std 1241-2000的测试标准,且相比传统价格昂贵的测试方法,该系统构建难度及成本低,可移植性强,操作简单易行,具有良好的实际应用前景。

[1] 黄 欣, 张 平, 童智勇, 等. 基于FPGA的软件无线电宽带多通道数字接收技术[J]. 科学技术与工程, 2009, 9(12): 3292-3296.

[2] 戴 澜, 姜岩峰, 刘文楷. 基于Matlab的高速高精度ADC测试研究[J]. 计算机测量与控制, 2010, 18(9): 2044-2049.[3] 黄深喜, 樊晓萍, 刘少强, 等. 高速ADC频域特性测试系统的设计[J].计算机工程, 2009, 35(9): 277-279.

[4] 董振龙, 董 惠, 武 锦. 基于FPGA的高速高精度ADC测试平台的设计[J]. 计算机测量与控制, 2012, 20(9): 2372-2374.

[5] 成 章, 王 健, 刘 敏, 等. 关于ADC测试平台的探讨[J]. 电子信息对抗技术, 2012, 27(4): 77-80.

[6] 何 芹, 黄 朴, 虞致国, 等. 基于平均频谱测试高速ADC动态参数的方法[J]. 电子测量与仪器学报, 2014, 28(7): 755-762.

[7] 裴颂伟, 李兆麟, 李圣龙, 等. 基于 V93000 的 SoC 中端口非测试复用的 ADC 和 DAC IP 核性能测试方案[J]. 电子学报, 2013, 41(7): 1358-1364.

[8] 贺志容, 石 坚, 韩红星. 93k集成电路测试系统校准原理及实现方法研究[J]. 宇航计测技术, 2009 (3): 66-69.

[9] NI. 高性能测试测量与控制平台-PXI产品[EB/OL]. http://sine.ni.com/nips/cds/view/p/lang/zhs/nid/ 1527.

[10] Grace C R, Denes P, Gnani D, et al. Radiation-tolerant code-density calibration of nyquist-rate analog-to-digital converters[J]. IEEE Transactions on Nuclear Science, 2013, 60(2): 1303-1310.

[11] 周 娟, 蒋登峰. 基于Matlab的ADC自动测试系统开发[J]. 中国计量学院学报, 2008, 19(3): 219-224.

[12] ADI. AD9254 14-Bit, 150 MSPS, 1.8 V, Analog-to-Digital Converter[M]. ADI INC. 2006.

[13] He Q, Huang P, Zhao L, et al. A five-item MSLD windowed triple-spectrum-line interpolated FFT algorithm for measuring SFDR[A]. 2014 12th IEEE International Conference on Solid-State and Integrated Circuit Technology (ICSICT)[C]. IEEE, 2014: 1-3.

Design and Implementation of Dynamic Parameter Testing System for High-speed and High-precision ADCs

Huang Pu, Feng Yang, Yu Zhiguo, He Qin, Gu Xiaofeng

(Ministerial Engineering Research Center of IoT Technology Applications, Department of Electronic Engineering, Jiangnan University, Wuxi 214122, China)

High-speed and high-precision analog-to-digital converters (ADCs) have been widely used in signal processing,their dynamic characteristics directly determine the system performance.Since there always exist deviations between practical chip parameters and designed indices, it is necessary to evaluate the actual dynamic performance of ADCs. By building an ADC hardware and software test platform based on FPGA and Labview, a low cost and high reliability performance evaluation system is constructed for high-speed and high-precision ADCs.The system controls the sub-ADC in bottom layer to provide accurate sampling; Asynchronous FIFO is used to carry out data cache, and DMA method to optimize data storage; Labview defines the communication module, combined with Matlab’s scripts to test the dynamic parameters.Finally, AD9467, a high-speed and high-precision ADC of ADI, is used for verifying the implemented system. Experimental results show that the system works stably, and the errors are within 2% compared with datasheet, which reaches the test standard provided by IEEE Std. 1241-2000, and the difficulties and cost in constructing the evolution system can be reduced.

analog-to-digital converter; dynamic parameter; modular approach; data collection

2015-11-30;

2015-12-25。

江苏省自然科学基金资助项目(BK20130156);江苏省六大人才高峰资助项目(DZXX-027);中央高校基本科研业务费专项资金资助项目(JUSRP51323B);江苏省普通高校研究生实践创新计划项目(SJZZ_0148,KYLX15_1192)。

黄 朴(1990-),男,江苏邳州人,硕士研究生,主要从事集成电路测试技术方向的研究。

虞致国(1979-),男,江西万年人,副教授,主要从事集成电路设计与测试方向的研究。

1671-4598(2016)06-0294-04

10.16526/j.cnki.11-4762/tp.2016.06.080

TN216

A

顾晓峰(1971-),男,江苏无锡人,教授,主要从事半导体材料与器件方向的研究。