基于FPGA的ADS-B信号解码的设计

2016-11-12胡安营

胡安营,王 涛

(山东航空股份有限公司,山东 济南 250000)

基于FPGA的ADS-B信号解码的设计

胡安营,王 涛

(山东航空股份有限公司,山东 济南 250000)

文章介绍了基于1090ES数据链技术的广播式自动相关监视设备(ADS-B)的解码流程;给出了FPGA和DSP信息提取的实现方案。通过ADS-B标准解码方式,文章采用Verilog编程语言和C语言完成了其各个功能模块的设计。实验结果表明,该方案可以实现ADS-B信号信息的提取,并可以提取ADS-B信号所包含的信息。

ADS-B;现场可编程门阵列;数字信号处理

广播式自动相关监视(ADS-B)接收机是基于卫星定位系统的飞行器运行监视技术的地/空、空/空信息地面设备。1090 ES ADS-B是基于S模式数据链的通信技术,可以提供通信数据带宽为1M Bit/s。ADS-B 接收机能够以较小的成本实现航空器动态的监视。本文主要进行了基于1090ES ADS-B接收机信号处理及解码功能的设计与实现。

1 方案设计

1.1 系统组成

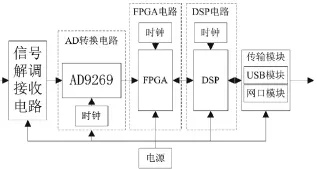

1090 ES ADS-B接收机主要由DSP处理器和现场可编辑门阵列(Field-Programmable Gate Array,FPGA)处理器、ADC电路组成。首先ADS-B载波信号经过信号解调电路,转换为ADS-B信号,并进行ADC电路10Mbps采样,送入FPGA和DSP中。其采样信号在FPGA中经过一系列的数字信号处理,得到所需要的ADS-B数字信息并送入DSP处理器中,通过DSP处理器提取相关信息送至上位机。系统的框图设计如图1所示。

图1 系统框图

1.2 DSP处理模块

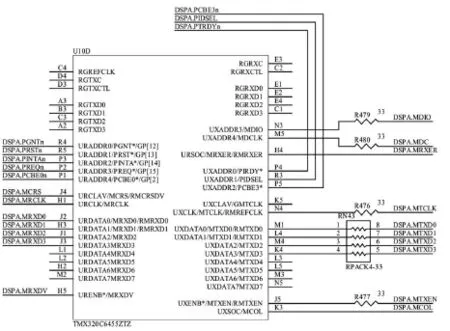

如图2所示,D S P处理模块由T I的D S P处理器TMS320C6455、时钟电路、电源模块组成。DSP处理模块主要用于ADS-B消息处理,对ADS-B的信号进行解码,得到ADS-B的明文信息。

图2 DSP电路图

1.3 FPGA控制模块设计

FPGA控制模块选用ALTERA公司的EP2C5Q208C8芯片。它具有144个引脚,其中102个I/O通信口,4608个逻辑单元,288个LAB。其并行处理的特点完全以较高的速率完成ADS-B信息解码处理,同时设计EMIF接口与DSP进行数据通信,完成ADS-B数据的提取。FPGA部分电路图如图3所示。

1.4 AD转换电路设计

模数转换电路采用ADI公司的AD 9269芯片,转换速率可以到达60 Mps,信号分辨率高,满足高频小信号ADS-B的信号采样的要求。其转换电路如图4所示。

1.5 网口电路设计

数据传输采用网口输出,物理芯片用的是ENC28J60。ENC28J60芯片是千兆网芯片,具有超低功耗模式和功率降低模式,能够满足当前设计需要。如图5所示,其模块主要是用户传递ADS-B明文信息。

图3 FPGA电路

图4 模数转换电路

图5 网络模块原理图

2 程序设计

该设计的程序流程包括接收数据、判断报头、计算参考功率、检测功率一致性、CRC校验等部分。

2.1 报头识别

判断脉冲的位置:4出现时间分别为0 μs,1 μs,3.5 μs,4.5 μs,考虑到容错需要,可以超前或者延后一个采样点。

2.2 参考功率计算

在报头识别的处理过程中,需要计算该参考的功率数值REM_PWOER,并使用该功率的参考值用于后面步骤的数据位的提取和置信度的计算,其流程如图6所示。

图6 参考功率计算流程图

2.3 检测功率一致性

ADS-B接收的解码需要计算报头脉冲5个采样点的平均数值。如果报头脉冲的平均值在报头脉冲幅度能够满足在参考信号幅度的±3 dB内,则认为通过功率的一致性检测,否则应该返回数据采集步骤,并重新判断报头。其程序流程如图7所示。

2.4 总体设计的流程

如图8所示,总体的程序流程包括接收数据、判断报头、计算参考功率、检测功率一致性、CRC校验等部分。

2.5 FPGA的实现

利用FPGA设计的RTL电路如图9所示。

2.6 实验结果分析

通过串口和网络输出ADS-B提取的消息:

*10780233;No-Call ;;;;;;;000;000;0;00000;

*1078056C;CSZ9676;ZH9676;ShenzhenAirlines;116.682 2;040.5287;A;34100;382;235;0;00000;

3 结语

本文研究了ADS-B接收机信号处理的设计方案,并在FPGA和DSP上实现ADS-B信号的解码与消息的提取。下一步的设计中,ADS-B中的重叠信号的处理方法和纠错算法还有待进一步研究。

图7 功率检测流程图

图8 总体设计流程图

图9 RTL电路

[1]RAJESH S,RAGHAVAN,ANALEX.Performance analysis of 1090 MHz automatic dependent surveillance broadcast(ADS-B)using OPNET modeler[M].Ohio:Brook Park,2002.

[2]朱芸.模式S应答接收机数字处理系统设计[D].成都:电子科技大学,2006.

[3]陈士毅.模式S应答处理中的数据处理[D].成都:电子科技大学,2006.

[4]郑超,刘志刚,王玉章.基于1090ES的ADS-B OUT系统的设计与实现[J].航空维修与工程,2010(1):56-58.

Design and implementation of ADS-B receiver signal processing based on FPGA

Hu Anying,Wang Tao

(Shandong Airlines Co.,Ltd.,Ji'nan 250000,China)

This paper introduces decoding process of broadcast automatic monitoring equipment (ADS-B)based on 109ES data chain technology and gives a implementation scheme of field-programmable gate array and DSP information extraction.Through the way of ADS-B standard decoding method,the paper complete design of moduals of all kinds of functions with Verilg programming language and C language.The experiment result showed that this scheme could realize the extraction of signal information of ADS-B and the information in it.

ADS-B;FPGA(Field-Programmable Gate Array);DSP(Digital Signal Processing)

胡安营(1983—),男,山东济南,本科;研究方向:交通信息工程及控制。