基于IEC61508标准的功能安全芯片设计方法探讨

2016-11-12谷荧柯崔同兵任军林子明

谷荧柯崔同兵任 军林子明

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

基于IEC61508标准的功能安全芯片设计方法探讨

谷荧柯1,2崔同兵1,2任 军1,2林子明1,2

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

集成电路设计和制造技术的发展使得芯片级功能安全设计取得快速进步,功能安全芯片的开发、验证方法成为业界关注的热点。基于IEC61508标准,首先论述该标准的功能安全技术手段,归纳总结当前国际主流功能安全芯片的设计技术特性。其次基于IEC61508标准对功能安全芯片的开发和设计进行深入分析,建立功能安全芯片开发的V模型。最后提出一套符合IEC61508标准的功能安全芯片的开发方法,基于该方法的约束设计一款ASIC芯片,并针对设计结果进行归纳总结。

功能安全;IEC61508;V模型;二取一冗余;锁步技术;冗余校验

1 概述

半导体技术的飞速发展,使得高性能、高鲁棒性系统的片上集成成为可能,从而提高了集成度,降低了功耗,减少了成本。功能安全系统也在逐步小型化集成,在提升产品综合性能的同时,也对系统的安全性带来挑战。IEC61508标准对功能安全芯片的开发提出要求,在其基础上建立的V模型可从开发流程上对功能安全芯片提供有效约束。目前,英飞凌、飞思卡尔和德州仪器等公司均已掌握功能安全芯片的设计方法,并发布了各自SIL3级别的CPU;其设计大多采用冗余思想、隔离技术、故障检测和保护、特殊开发工具等手段,可保证较高的鲁棒性和测试覆盖率。

2 IEC61508安全标准

2.1 标准简介

IEC61508安全标准[1]由国际电子协会于1998年第一次发布并在其中正式提出“功能安全”的概念。目前IEC61508是业内公认的一个最基本的针对特殊应用的国际安全标准,其定义4个安全完整度等级,简称SIL等级,SIL等级越高,表明系统的安全性越高。SIL等级为开发者、供应商和用户等各方面提供了界限明确的安全规范。该标准在高层次上进行了抽象的约束,提供灵活的设计方法,同时设定明确的要求和界限;其满足了对软硬件的要求,为技术创新留下灵活的发挥空间。

IEC61508标准第二部分的附录F提出,可通过测试和验证等方法避免ASIC芯片的系统性错误,从而提高系统安全完整度的方法;该部分以表格的形式详细列出不同SIL等级对设计、测试或者验证方法的要求。标准第三部分的规则主要针对软件编程,其中ASIC开发涉及的硬件描述语言编程也要适用于此规则。

2.2 标准技术分析

为了保证硬件的容错能力,IEC61508标准提出一系列技术手段。下面分析主要以电路设计技术为例。硬件冗余是最基本的策略,包括N取M冗余架构、冗余校验等;其次,可测试性设计如DFT/ BIST电路设计;第三,关键模块(如时钟、内存)的监控和保护电路;第四,易干扰模块间的隔离。下面着重介绍N取M冗余架构。

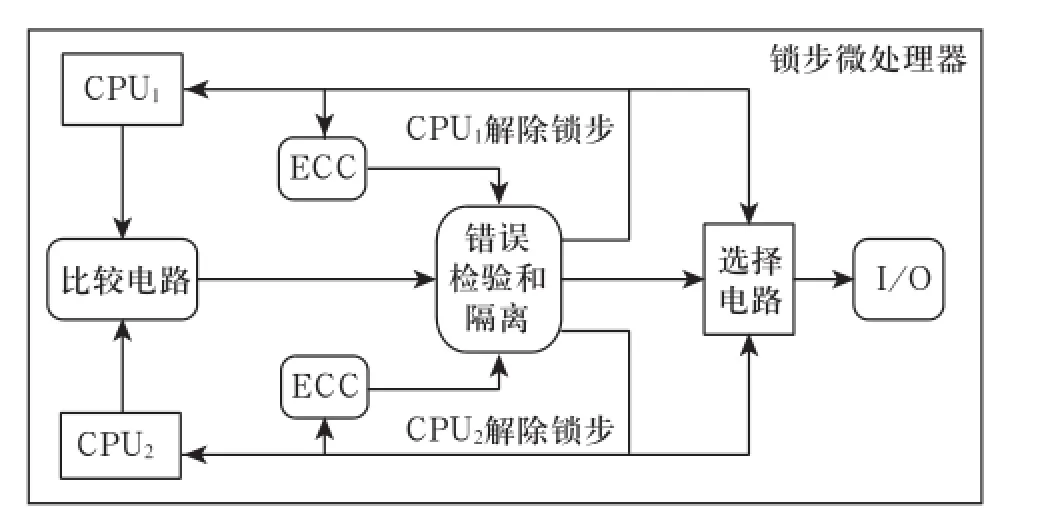

为保证系统在非正常条件下将系统导向安全状态,IEC61508标准建议采用N取M冗余架构,最经典的是二取一冗余架构(如图1所示)。二取一冗余架构包含两个完全相同的并行通道(主通道和冗余通道),还有一个集成的诊断电路持续地比较两个通道的输出结果。如果两通道的输出结果发生冲突,那么诊断电路将错误信息分别反馈,并通过系统设计的安全通道将系统导向安全状态。如果两个通道同时发生故障或共因失效,那么系统将丧失安全功能;此时外部检测模块(如看门狗、温度/电压监测电路)将系统导向安全状态。后来发展的基于锁步技术的微处理器,其本质仍然是二取一冗余架构。

图1 二取一架构

2.3 应用案例

目前,市场上有3种主流的功能安全芯片[2]:德州仪器的TMS570LS系列微处理器、英飞凌的TriCore系列微处理器、飞思卡尔的MPC5765P微控制器,均达到IEC61508标准规定的SIL3等级。德州仪器的TMS570LS微处理器采用基于锁步技术的双32位RISC内核架构;对CPU、内存、存储器内置自检、循环冗余校验(CRC)逻辑和ECC纠检错电路;为地址总线设计奇偶校验逻辑;此外,还有内存保护单元(MPU)、可追踪测试模块和故障修正模块。英飞凌的TriCore基于由主处理器、监视处理器和外设控制处理器(PCP)构成的三核架构,采用锁步技术对CPU故障进行诊断;其包含内存故障检测和保护模块、存储器和内存循环冗余校验逻辑。飞思卡尔MPC5765P微控制器的双核/存储器/桥间均采用指令级锁步,双核并行工作,内部集成的存储器和内存具有ECC检纠错能力,内嵌BIST和时钟/电源监控。

此外,Yogitech公司[2]致力于功能安全芯片IP核以及开发/测试EDA平台工具的开发。其基于ARM Cortex M3的Yogitech fRCPU, 在 采用锁步、冗余校验等技术的同时,还采用自己的fR工具以提高芯片的鲁棒性和测试覆盖率。近年来,该公司一直为其他设计公司提供IP核和EDA工具的授权服务。

功能安全芯片在工业界应用的日益广泛引起学术界强烈的研究兴趣,意大利圣马提诺研究所的Riccardo Mariani[3]对功能安全芯片的设计和测试提出解决方案;德国卡塞尔大学的Ali Hayek[4]讨论了基于IEC61508功能安全芯片的设计;美国的MIT和UCLA也有相关研究课题。在国内,中科院也发布了具有自主知识产权的功能安全CPU,已成功应用于航天等领域。但是,目前业界仍然没有针对功能安全芯片的开发、测试形成一套公认的完整方法和流程,此课题还需深入研究。

3 功能安全芯片开发流程

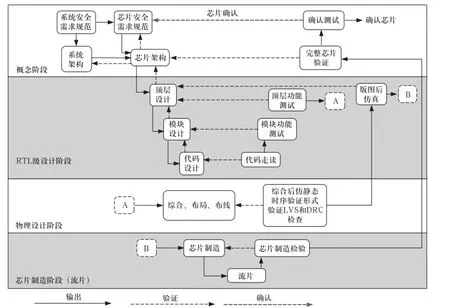

芯片(特指数字电路)的开发同时受软、硬件开发规范的约束,芯片本身是硬件设备,但其开发过程主要依靠硬件描述语言编程实现。本节根据IEC51508标准对功能安全芯片开发过程的各个阶段进行分析,建立了闭环V模型(如图2所示)。其中,硬件描述语言要满足IEC61508第二、三部分的约束。

总而言之,功能安全芯片的开发主要分为概念阶段、RTL级设计、物理设计、制造4个阶段,每个阶段的每个子过程都有对应的验证/测试过程,构成闭环的开发流程,具体参见V模型。该模型所示的开发流程可保证每个阶段的设计结果能被充分验证/测试,提高了开发过程的可靠性。下面结合IEC61508标准,对每个开发阶段做相应的要求。

图2 功能安全芯片开发V模型

1) 系统安全需求规范

明确,不含糊,可测试的需求,可进行追溯的安全需求规范;详细的硬件和软件需求规范,包括接口、性能、响应时间等参数;采用经过时间和市场检验的设计方法、结构、开发平台等;同时满足安全标准对软硬件的安全完整度要求。

2) 架构、顶层、模块设计

系统架构设计、接口规划、模块划分,合理分配系统需求到子模块;完成芯片内部子模块的结构设计,并确定相应的验证/测试规范。

3) 代码设计

模块化设计,降低代码复杂度,加注释提高可读性;对时序进行严格约束,注意阻塞/非阻塞语句的区别;可测试性设计如BIST和DFT,提高测试覆盖率;可综合性设计;使用经过市场和时间检验的开发语言、辅助软件版本。

4) 物理设计和制造

严格遵守版图布局布线要求,并留合理的裕度;对易串扰模块进行物理隔离;合理设计电源线/信号线的线长和线宽;选择成熟的工艺和代工厂。

4 功能安全芯片设计技术

针对前述市场上主流的四款功能安全CPU,对其采用的技术手段做相应总结,如表1所示。

表1 功能安全芯片主流技术

根据IEC61508安全标准的要求,结合上述功能安全CPU的设计技术,本节总结分析了针对功能安全芯片的开发方法。

4.1 严格遵守V模型的闭环开发流程

本文提出的V模型专门针对芯片独特的开发流程而设计,涵盖芯片设计的每个阶段并提供严格的约束,其闭环特性保证设计的可追溯性、测试和验证的完备性。该模型也包含IEC61508标准对功能安全芯片设计的最基本的要求。

4.2 冗余设计技术

目前,功能安全系统主要采用“冗余设计”的思路,包括N取M架构、锁步技术、冗余校验等。

1) N取M架构

IEC61508标准建议采取N取M冗余架构保证系统的安全等级,最常见的就是二取一冗余架构。如前所述,二取一冗余可以在系统发生故障时将系统导向安全状态,而且这种冗余思想是后面锁步技术的基础。

2) 锁步技术

锁步技术[5,6]常用于功能安全处理器中,其包含两个CPU处理器,集成比较逻辑,构成自监控对,不断互相监控和检出错误;此外,还包括错误检查、隔离和恢复逻辑,如图3所示。如果比较结果正确,其中一个通道的校验输出错误,可以禁止此通道的CPU和解除锁步,另一个通道的CPU独立工作;如果比较结果错误且其中一通道校验错,说明这路的校验逻辑或接收模块出错,恢复到上一个状态;如果比较错误但两边校验正常,说明两边失步,系统停止工作;如果发生双通道均校验错,说明两个CPU或接收模块故障,系统停止工作。

图3 锁步技术

综上所述,锁步技术处理器主要有3个功能:故障发现,故障容忍和隔离、纠正,故障恢复。

4.3 冗余校验技术

常用的校验逻辑包括奇偶校验、ECC校验、CRC校验等。奇偶校验只能检错,ECC可以检查并对错误进行纠正。鉴于ECC同时具有检/纠错能力,以及大数据量下只需较少的冗余数据,成为目前主流的校验方式。CRC校验主要用于数据通信中。在功能安全芯片的开发中采用校验逻辑可以提高数据存储、传输的可靠性,提高系统的容错能力和鲁棒性。

4.4 测试、监测和保护模块

1) 可测试性设计

SIL等级对芯片的测试覆盖率有一定要求,要注意可测试性设计,如BIST、DFT等。此外,对于复杂的处理/控制电路,还要增加JTAG接口,可以实现对内部的寄存器、Flash、内存、时钟等进行扫描测试。

2) 监测、保护电路

对于特殊的模块,如内存、数据寄存器、数据存储器、时钟等模块,要专门设计检测电路,对其温度、电压、电流等状态进行监视,故障发生即进行断电等保护。

4.5 隔离技术

对于易互相干扰的模块要进行物理隔离,避免互扰失效。常用的隔离技术主要有磁隔离、电容隔离、光耦隔离、物理分隔等措施,上述技术的片上集成已经是热门研究课题。

4.6 特殊的开发工具

对于SIL等级较高的芯片,一般的EDA工具难以很好地对其设计和测试进行支持,需要特殊的开发工具。目前大型的集成电路设计公司均有自己特殊的EDA辅助工具,比如英飞凌的Infineon Solution Finders,Yogitech公司的fR工具等。

5 新型应答器控制芯片

基于上述方法,本节设计了一款应用于安全系统的ASIC芯片——大容量应答器控制芯片,该芯片的开发流程严格遵守上述V模型。应答器控制芯片是应答器设备的控制核心,负责完成应答器所有逻辑处理功能,其基本架构和最终版图如图4(a)(b)所示,包括FSK/PSK通道报文的读取、发送,A5命令的解析,FSK/PSK通道报文的写入等。其有如下特点:

图4 新型应答器控制芯片

1) 该芯片第一次将PSK解码模块进行片上集成,避免了多元件布线和焊接带来的安全性问题;

2) FSK/PSK通道均具有对报文的读取和发送功能,为避免干扰在版图设计时对其进行了有效的物理隔离,如图4(b)所示。

3) 该芯片时钟可采用载频27 M时钟、有源/无源9M时钟3个可选时钟源,可以根据不同的应用配置相应的时钟,且配置完成后不会受到另外两时钟通道的影响;

4) 采用LFSR伪随机序列对FSK/PSK报文分别进行加密,引入了冗余逻辑,可降低由报文互扰导致错误的风险。

6 总结与展望

本文根据IEC61508安全标准的要求,分析了当今主流的功能安全芯片所采用的设计技术。其次,从流程和技术手段出发,整理出针对功能安全芯片的一套基本的设计方法。最后基于上述方法开发一款用于功能安全系统的ASIC芯片。该芯片安全功能设计流程采用V模型进行验证和约束,且借鉴功能安全芯片的开发技术和理念,有利于提高设备整体的可靠性和安全性。简而言之,当前基于IEC61508安全标准的芯片级功能安全设计正处于快速发展的阶段,芯片级安全设计的理念在安全控制业界逐步得到认可和推广,可以预见,功能安全芯片将会在安全控制系统中扮演越来越重要的角色,并推动装备的技术革新。

[1] IEC.Functional safety of electrical/electronic/programmable electronic safety-related systems IEC61508[S].2010.

[2]史学玲,冯晓升.IEC61508标准的基本原理与方法研究[J].工业控制计算机,2006,19(11):17-17.

[3] Mariani R.The impact of functional safety standards in the design and test of reliable and available integrated circuits[C].ETS,2012.

[4] Hayek A,Borcsok J.Safety-Related ASIC-Design in Terms of the Standard IEC 61508[C].PESARO,2013.

[5]陈浩.处理器Lockstep技术研究[J].数字技术与应用,2012(8):56-58.

[6]周啸.基于60x总线的Lockstep处理器架构[J].航空计算机技术,2015(1):127-130.

Due to the rapid development of integrated circuit design and manufacturing technologies,chip-level functional safety-related devices have made great progress. The development & validation methodology of functional safety- related IC has become the focus of the industry. This paper discusses the functional safety techniques introduced in IEC61508 standard, summarizes the main technical characteristics of functional safety-related IC at present, and presents a V-model for functional safetyrelated IC development based on the analysis of IEC61508 standard. Finally, it puts forward a complete methodology of functional safety-related IC development conforming to IEC61508 to design an ASIC, and gives a short conclusion on the design result.

functional safety; IEC61508; V-model; 1 out of 2 redundancy; lock step technology; redundant check

10.3969/j.issn.1673-4440.2016.05.001

北京全路通信信号研究设计院集团有限公司研究项目(2300-K1140044)

(2015-09-23)