一种高效可靠的MVB总线网关设计

2016-11-12谢立国马振球

谢立国马振球,2

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

一种高效可靠的MVB总线网关设计

谢立国1马振球1,2

(1.北京全路通信信号研究设计院集团有限公司,北京 100070;2.北京市高速铁路运行控制系统工程技术研究中心,北京 100070)

不同的MVB总线物理层存在两方面的差异:ESD+和EMD波形的差异;单路A线和A/B冗余总线的差异。波形的差异会导致总线无法互联互通,单路和冗余总线的差异会导致B路冗余总线失效,降低整个通信系统的可靠性。对上述差异进行详细分析,设计并实现一种MVB总线网关,测试结果证明所设计网关的高效性和可靠性。

MVB;列车控制;网关;总线冗余

1 概述

列车通信网络TCN已形成国际标准IEC61375-1[1],其包括多功能车辆总线(MVB)和绞线式列车总线(WTB)两大部分[2-3]。MVB总线用于车辆控制,WTB用于列车控制。MVB总线的物理层有3种。电的短距离:ESD+,传输介质使用双绞屏蔽线,按照隔离RS-485电平标准传输,最多支持32个设备,最大总线距离20 m。电的中距离:EMD,传输介质使用双绞屏蔽线,使用变压器耦合,最多支持32个设备,最大总线距离200 m。长距离:OGF,传输介质使用光纤,总线距离可达2.0 km。另外,根据使用场合的可靠性要求,物理层可采用单独A线,或者A/B双线的冗余机制。上述物理层的多样性带来不同MVB总线之间的互连性问题。例如单独A线系统与A/B冗余总线系统之间的互联,ESD+总线与EMD总线的互联。OGF应用场合较少,本文不作讨论。

目前,大多数文献关注于第1~4类MVB设备本身的实现[4-7],关于解决上述MVB互联问题的文献较少。本文设计并实现一种高效可靠的MVB总线网关,解决了该互联问题。测试结果表明所设计网关完全满足预期指标要求。

2 网关设计原则

MVB总线网关设计主要面对两个问题:1)单独A线系统和A/B冗余总线系统的差异性;2)物理层ESD+和EMD波形的差异性。

对于单独A线系统,系统仅使用A线电缆进行数据通讯。若A线通信质量下降,则导致整个通信系统的性能下降或中断,因此这种工作方式通常应用于通信环境较好的场合。对于A/B冗余总线系统,系统同时使用A/B总线。在任意时刻,系统选择其中某一线路作为当前工作线路,另一路作为备选线路。若检测到工作线路通信质量较差,系统实现当前工作线路与备选线路的自动切换。A/B冗余总线系统可大大提高整个通信系统的可靠性,其通常应用于通信环境较差的场合。单独A线系统与A/B冗余总线系统互联时,若简单地将单独A线系统直接连接到A/B冗余总线系统的A线,这将导致失去其原有的冗余备份功效,降低整个通信系统的可靠性。

ESD+和EMD波形的差异性主要体现在如下方面。

1)总线空闲电平

ESD+时,通过总线首末节点的上下拉电阻,总线的空闲电平为低电平。EMD时,由于采用变压器隔离,总线的空闲电平为浮动的,体现在接收端所接收到的信号既可能为逻辑高,也可能为逻辑低。

2)数据帧起始波形

ESD+和EMD数据帧起始波形分别如图1所示[1]。虽然标准给出的两种情况接收方收到的波形是相同的,但在实际实现时,为防止噪声干扰,接收端一般采用斯密特接收器,图1中EMD时接收端收到的起始电平信号为总线空闲时的电平状态,根据不同情况,接收端对该电平的处理既可能为高,也可能为低。因此ESD+和EMD数据起始帧波形存在差异。

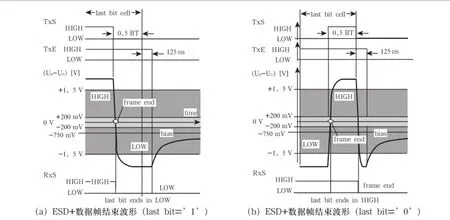

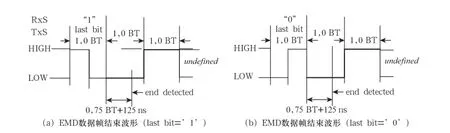

3)数据帧结束波形

ESD+和EMD数据帧结束波形分别如图2、3所示[1],两者存在较大的不同。如图2所示,ESD+的波形较为简单,发送完最后一个bit后,发送端简单地将发送使能置为无效,使得总线恢复为空闲低电平状态。如图3所示,对于EMD波形,发送完最后一个bit后,发送端需要再次发送1 bit宽度的低电平和1 bit宽度的高电平。

单独A线系统和A/B冗余总线的差异,物理层ESD+和EMD波形的差异共同决定两种不同的MVB总线无法直接实现互联互通,需要设计网关进行数据处理。

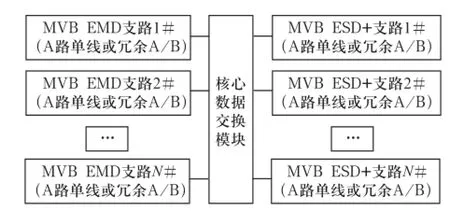

3 网关系统设计

单独A线系统和A/B冗余总线系统的差异性以及ESD+和EMD波形的差异性决定设计的总线网关不能基于MVB的物理层,而应该基于链路层或更高的应用层,这样才能消除波形差异性所带来的影响,同时确保B线冗余线路所带来的通信可靠性提升。总线网关基于MVB通信链路层,其设计原则为对每个MVB支路单独管理,每个支路均具备独立完整的数据发送和接收功能,可独立处理不同物理层的MVB总线数据,例如ESD+或EMD,单线或双线冗余等,网关结构设计如图4所示。核心数据交换模块接收各个支路收到的总线数据,并对数据进行判断比较,若收到的数据是全新的,则将该数据拷贝到对应的目标支路发送出去,以此方式完成数据的转发操作,实现各条MVB支路的互联互通。

图2 ESD+数据帧结束波形

图3 EMD数据帧结束波形

图4 总线网关系统结构图

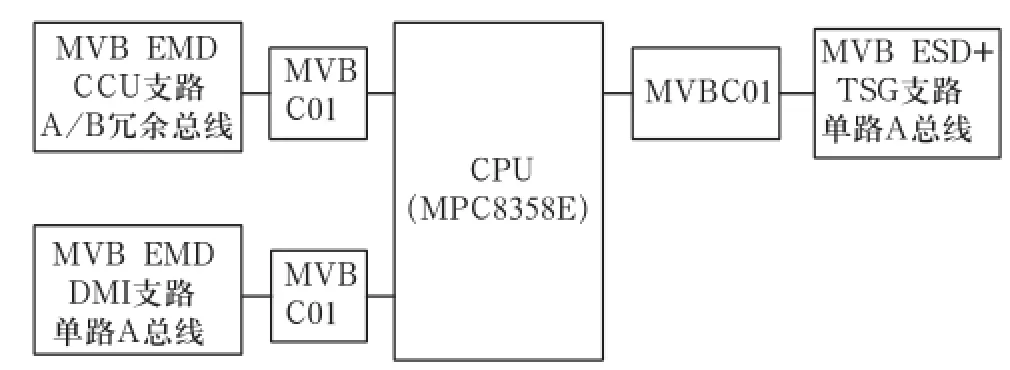

基于上述设计结构,图5所示为一个具体的MVB总线网关设计实例。网关与三路总线互联,分别为:

图5 总线网关实现结构图

MVB EMD CCU总线支路,该支路采用A/B冗余总线。

MVB EMD DMI总线支路,该支路采用单路A总线。

MVB ESD+TSG总线支路,该支路采用单路A总线。

设计主CPU采用MPC8358E芯片,各MVB支路均采用MVBC01芯片作为总线控制器,实现对MVB总线的控制管理和数据收发。主CPU负责按周期轮询对各MVB总线端口进行轮询,若查询到新的端口数据,则将数据转发至目标MVB总线支路。3个MVB支路可实现对所有端口的无缝全映射,例如,若MVB EMD CCU支路存在0x354端口,可将该端口映射到MVB ESD+TSG支路上,MVB ESD+TSG支路上的设备可以像访问自身总线上的端口一样对0x354端口进行读写访问,所获得的数据实际为MVB EMD CCU支路上的数据。

值得说明的是,上述实现结构会带来数据传输的延迟,即某一端口的数据从某一条MVB支路经过网关传输到另一条MVB支路会存在时间延迟,正常情况下时间延迟Tdelay为:

式中,Tpoll表示端口的轮询周期,Tgateway表示网关处理数据所带来的延迟。

4 实际测试结果

针对上述实现的总线网关,制作了测试工装进行性能测试,其测试原理如图6所示。测试工装模拟产生原始总线数据,经过某条总线发送给被测网关。被测总线网关按照配置将接收到的数据从其他总线支路回传给测试工装。在收到回传的总线数据后,测试工装和原始数据进行对比,判断数据是否正确以及数据延迟是否满足规定要求。

图6 MVB总线网关测试结构图

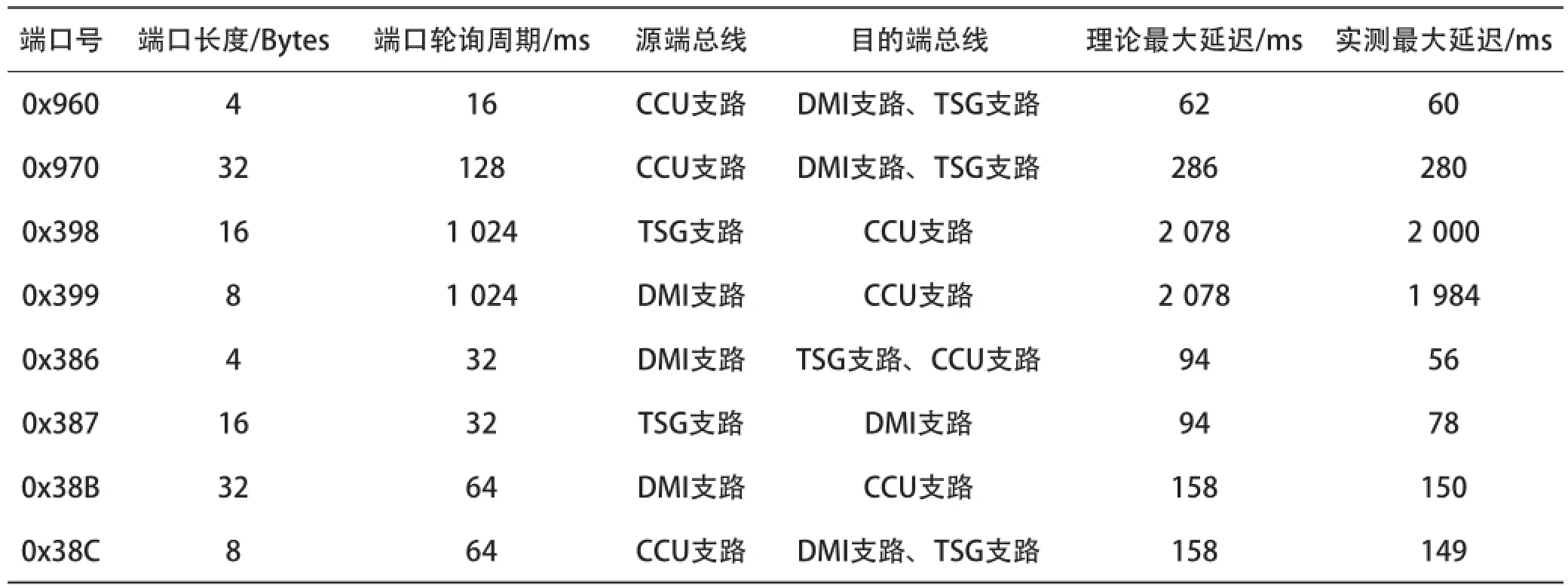

表1给出总线端口配置和对应的测试结果,测试结果表明在网关处理延迟T_gateway为30 ms的情况下,所设计的网关数据未发生丢失,各端口数据传输的最大延迟满足预设指标。

表1 MVB总线网关测试结果

5 总结和展望

分析和指出了MVB总线物理层存在两方面的差异:1)ESD+和EMD波形的差异;2)单路A线和A/B冗余总线的差异。其中,波形的差异会导致总线无法互联互通,单路和冗余总线的差异会导致B路冗余总线失效,降低整个通信系统的可靠性。针对上述问题,设计并实现一种MVB总线网关,测试结果证明所设计网关的高效性和可靠性。

[1] IEC.Electric railway equipment-Train bus-Part 1:Train communication network IEC61375[S].1999.

[2]路向阳.列车通信网络的发展与应用综述[J].机车电传动,2002(1):5-9.

[3] Hubert D.Kirrmann,Ulrich Claessen.IEC列车通信网络[J].机车电传动,1999(5):4-9.

[4]杨绪红,赵明元,谭南林.列车通信网的方案研究[J].计算机系统应用,1999(9):30-31.

[5]张元林,范祚成,梁波.基于MVBC的分布式智能I/O模块的研究[J]. 机车电传动,2000(4):15-18.

[6]李红.MVB1类设备控制器的FPGA设计[D].大连:大连理工大学,2006.

[7]蔡颖.多功能车厢总线控制器(MVBC)的研究与设计[D].成都:西南交通大学,2005.

There are two differences in the MVB bus physical layer. One is the waveform difference between ESD+ and EMD, and the other is the difference between single-channel bus line and A/B redundant bus line. The waveform difference will lead to the bus connectivity problems. The difference between the single-channel bus and A/B redundant bus will cause B bus line failure to reduce the reliability of the whole communication system. The paper introduces the design of MVB bus gateway based on the analysis of the two differences. The test result proves that the gateway has high effi ciency and reliability.

MVB; train control; gateway; bus redundancy

10.3969/j.issn.1673-4440.2016.05.008

中国铁路总公司科技研究开发计划重大课题项目(YK-2012K19)

(2016-07-19)