基于FPGA的磁共振成像仪梯度模块的设计

2016-11-09董海峰郑振耀姚凯文

董海峰,郑振耀,姚凯文,谢 晨,陈 忠

(厦门大学电子科学系 福建省等离子体与磁共振研究重点实验室,福建 厦门361005)

基于FPGA的磁共振成像仪梯度模块的设计

董海峰,郑振耀,姚凯文,谢 晨,陈 忠

(厦门大学电子科学系 福建省等离子体与磁共振研究重点实验室,福建 厦门361005)

针对磁共振成像仪小型化、数字化的发展需求,提出了一种基于FPGA的磁共振成像仪梯度模块设计方案。该方案以FPGA为系统控制核心,结合高精度的四通道DAC和高分辨率的数字电位计,实现了梯度脉冲波形的生成、转换、预加重处理等一系列的功能。与以往的方案相比,该方案不但有效的减轻了主处理器FPGA的工作负担,而且尽可能的提高了系统的数字化和集成化。通过软件仿真和联机调试,结果表明该方案工作稳定可靠,能够很好的满足小型化磁共振成像系统的需求。

磁共振成像;梯度;FPGA;预加重

磁共振成像(magnetic resonance imaging,MRI)技术能够在对机体没有损伤的前提下快速、准确的获得机体内部的图像,具有对比度高、成像参数多、无电离辐射伤害等优点,因此在现代医学成像领域中具有广泛的应用[1]。目前在大多数磁共振成像仪中,梯度模块的设计方案多以高性能的FPGA或DSP实现梯度脉冲波形的生成和处理为主[2-3],虽然集成度高,但是对器件性能要求高,内部控制逻辑和程序复杂,设计难度也比较大。文中提出一种以FPGA为系统控制核心,结合四通道的串行输入DAC和高精度的数控电位计的梯度模块设计方案,显著的降低了对FPGA的性能需求,简化了电路和程序设计,具有全面兼顾性能、集成度、复杂度和成本的优点。

1 梯度模块设计原理

在磁共振成像系统中,除了需要使成像体原子核产生磁化的主磁场外,还需要对其X、Y、Z 3个方向上施加线性变化的梯度磁场以便进行空间编码,从而得到具有空间编码信息的信号,再由上位机软件经过数据处理即可恢复重建出物体的内部图像[4]。因此,梯度磁场质量的好坏直接影响到最终成像的质量。根据磁共振成像仪的功能需求,梯度模块需要产生符合条件的梯度脉冲序列,并且转换成模拟信号,经过梯度功率放大器放大后送至梯度线圈,从而产生所需的梯度场[5]。此外,由于信号采集过程中梯度线圈上的电流快速切换,会在线圈及附近的导体上产生涡流效应[6],因此还需要对梯度脉冲进行预加重处理[7]。一般磁共振成像仪梯度模块主要包括梯度波形发生器、梯度功率放大器和梯度线圈等,其中梯度波形发生器主要实现梯度脉冲波形的生成、数模转换和预加重处理等功能[8]。

2 系统整体设计

2.1 整体方案设计

本方案设计的梯度模块系统框图如图1所示。

图1 梯度模块整体设计系统框图

在本系统中,FPGA作为系统主控制核心,系统启动时,由EPCSFlash芯片存储的程序对FPGA进行配置和外设初始化,通过以太网口与上位机通信[9],接收上位机软件传来的梯度脉冲波形数据并存入SDRAM中,然后根据指令调节预加重参数,配置DAC芯片并将梯度脉冲数据进行并串转换,发送梯度脉冲数据并驱动DAC进行数模转换,再经过预加重处理送至梯度功放进行功率放大,最后馈入梯度线圈产生所需的梯度磁场。其中,FPGA芯片采用Altera公司的Stratix III系列的芯片EP3SL150F1152,该芯片性能强大、功耗低、硬件资源及嵌入式硬核资源丰富,具有700多个用户引脚可扩展多外设,内置嵌入式NIOS II软核CPU,其最高频率可达290 MHz,处理速度达340 MIPS,完全满足成像仪系统的需求。

2.2 DAC部分设计

由于梯度脉冲信号包括X、Y、Z 3个通道,分别为选层、频率编码和相位编码,因此采用一片四通道的DAC芯片可以完全满足转换需求,并且剩下的一路DAC可以作为匀场通道备用[3-10]。本设计采用ADI公司的AD5764R作为数模转换芯片,该芯片是一款四通道、16位、串行输入、双极性电压输出DAC,积分非线性(INL)误差为±1 LSB,噪声很低,建立时间为10μs。该器件还有一个数字I/O端口,可通过串行接口进行编程。AD5764R采用串行接口,能够以最高30 MHz的时钟速率工作,并且与DSP和微控制器接口标准兼容。利用双缓冲,所有DAC可实现同时更新。AD5764R的串行接口时序图如图2所示。

图2 AD5764R的串行接口时序图

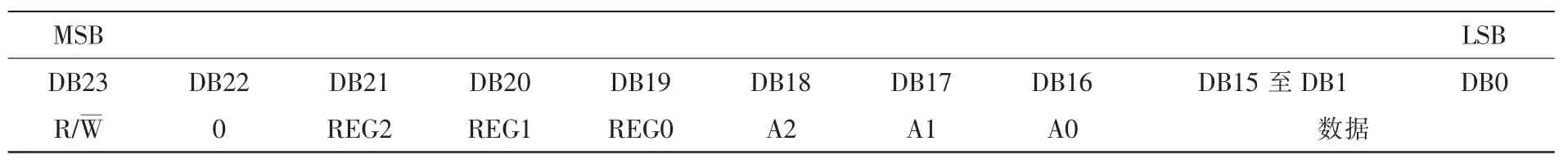

表1 AD5764R的输入移位寄存器格式

根据AD5764R的时序图和寄存器格式使用FPGA编写控制驱动,即可实现各个通道的数模转换功能。例如写全部DAC的控制函数代码如下:

实测当正向最大数据设为0x7FFF时,输出电压为9.997V。AD5764R微调增益寄存器是6位寄存器,允许用户在-32 LSB至+31 LSB范围内,按1 LSB增量调整各DAC通道的增益。计算可知进行20 step的增益弥补3mV,即可达到+10 V的标准最大输出。

2.3 预加重部分设计

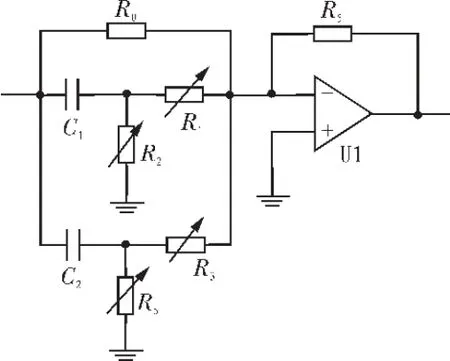

涡流是指变化的磁场在其周围的金属体内产生的感应电流,强度与磁场变化率成正比。涡流所产生的磁场与原磁场想反,阻碍原磁场的变化。在梯度脉冲的上升沿和下降沿,由于梯度电流的快速切换,会瞬间产生较大的磁通变化,从而引起较大的涡流,严重影响梯度场的变化,使梯度波形畸变,从而导致采得的图像出现伪影[11],严重影响成像质量。梯度涡流可以用一系列具有不同时间常数,不同权重的e指数函数的线性和来表示,因此可以采用对梯度信号预加重的方法进行补偿[12-14],从而抵消涡流的影响。预加重的原理如图3所示。

图3 具有2阶预加重的电路原理图

由一个电容与两个可变电阻组成的RC电路网络可以得到e指数函数形式的电压信号,其中可变电阻R1和R2分别用于调节波形的幅度常数和时间常数。RC电路的时间常数的计算公式为:

式中,U0和UC分别表示电容C输入端和另外一端的电压值。计算可知,当t=4RC时,UC=0.98U0,因此可近似认为t=4RC,从而根据R、C值估算时间常数。通过Multisim软件对预加重电路进行仿真,得到预加重前后梯度波形变化对比示意图如图4所示,图中横坐标均为时间t(s),纵坐标均为电压幅值U(V)。

图4 预加重前后梯度波形变化对比示意图

使用多组具有不同R、C值的预加重信号与原始梯度信号通过运放叠加,调节可变电阻的阻值,使预加重波形尽可能的补偿涡流效应造成的畸变,从而得到波形正常的梯度脉冲信号。本设计中R值全部选择满量程为25 kΩ的可调电阻,为了能够尽可能的补偿涡流的影响,每个通道采用4阶不同参数的预加重调节,其中电容C的值分别选择0.1μF、10 nF、1 nF和100 pF。

由于传统的可变电阻如3 296电位器等,阻值精度低,精确调节困难且误差大,温度系数也高,因此本设计采用ADI公司的AD5235芯片作为可变电阻器。AD5235是一款非易失性存储器、双通道1 024位数字电位计,温度系数低至35 ppm/℃,具有SPI兼容型串行接口,加电自动刷新EEMEM设置,标称阻值有25 kΩ和250 kΩ可选,能够很好的满足预加重电路的需求。主控FPGA通过SPI串行接口配置AD5235的24位数据字,可以根据需要灵活调节可变电阻的阻值。

2.4 输出接口设计

梯度脉冲信号经过数模转换和预加重处理后送至梯度功率放大器进行放大[15],梯度放大器采用PCI公司的GA150型放大器,该放大器是一款单通道150VDC,75 Arms的脉宽调制功率放大器。考虑到功放输入接口的需求,预加重后的梯度信号需要转换成差分信号输出,使用差分信号可以有效的降低电磁干扰并提高放大系统的信噪比。本设计采用ADI公司的ADA4922-1差分驱动器,它具有宽电源电压范围(5 V至 26 V)、轨到轨输出、高输入阻抗和固定增益+1(单端)或+2(差分),低失真和高信噪比(SNR)等特点,能够很好的将梯度输出信号由单端信号转换为差分信号。

3 联机测试

为了验证所设计的梯度模块的功能实现效果,将梯度输出的差分信号接入RIGOLDS1074示波器进行测量。所测信号为频率编码梯度(Gx),采样时间(Ts)为 3.2 ms,并预先设置了一组预加重参数,示波器中显示的梯度模块输出波形如图5所示,图中的波形上下两条为差分梯度信号,中间为示波器计算所得的单端信号。由测量结果可见,梯度模块信号输出正常,预加重效果明显。

图5 梯度模块输出脉冲波形图

再将梯度模块输出接入梯度放大器,输出梯度脉冲至梯度线圈,并实时调节预加重参数。通过梯度放大器上的VMON端口可以监测输出到线圈上的实际电压,将该端口通过BNC线连接至示波器,所得梯度线圈上最终得到的梯度脉冲波形如图6所示,可见最终生成的梯度脉冲波形良好,涡流效应基本被预加重抵消,达到了预期的目标。

图6 梯度线圈实际所得脉冲波形图

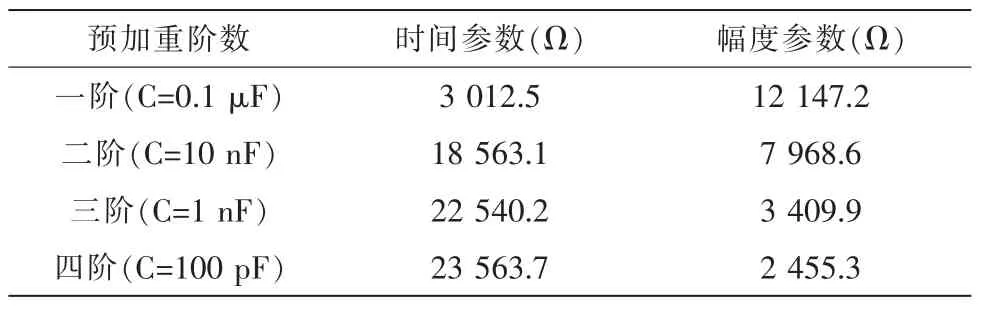

实测此时的预加重可变电阻的参数如表2所示。通过FPGA不断的调节数控电位计AD5235的阻值,可以方便的调节预加重的时间常数和幅度常数,从而尽可能的获得理想的梯度脉冲波形。测试结果表明,本梯度模块可以很好的实现梯度脉冲信号的生成、数模转换、预加重处理和单端至差分转换等功能。

表2 实验中预加重电位器参数实测值

将文中设计的梯度模块应用于本实验室自主研发的0.5 T磁共振成像仪系统中,以放置了3D打印的镂空模型的水模为实验模型进行图像采集实验,采样结果如图7所示,图中采样面为横断面,分辨率达0.5mm。由实验结果可见,采集到的图像质量清晰,信噪比高,成像效果良好,说明该梯度模块在0.5 T磁共振成像仪系统中运行正常,能够较好的满足系统需求。

图7 0.5 T磁共振成像仪采集得到的水模图像

4 结 论

文中介绍了基于FPGA作为主控制核心的磁共振成像仪梯度模块设计方案,给出了梯度模块整体的设计框图,并且重点介绍了FPGA、DAC、预加重处理等关键部分的具体设计。模块的联机测试结果表明本方案能够满足磁共振成像仪梯度通道的需求,取得较好的成像效果,同时具有复杂度低、简单可靠、易于控制和扩展等特点,为研制低成本、小型化的磁共振成像仪提供了一种简单实用的梯度解决方案。考虑到涡流效应主要由磁体内部线圈及周边金属产生,并且涡流大小取决于梯度电流的大小和切换率,因此本设计对不同磁场强度的磁共振成像仪的梯度方案也具有一定的参考意义。

[1]Haacke E M B,Brown R W,Thompson M R,et al. Magnetic Resonance Imaging:Physical Principles and Sequence Design[J].Proteomics,1999,xxvii.

[2]肖亮,汤伟男,王为民.基于单片FPGA的磁共振成像梯度计算模块[J].波谱学杂志,2010,27(2):163-171.

[3]潘文宇,张富,罗海,等.一种基于高性能DSP的MRI梯度计算模块设计[J].中国医疗器械杂志,2011,35(3):189-193.

[4]卡斯特勒.深入了解MRI基础[M].人民军医出版社,2012.

[5]艾吉斯.开放式永磁型MRI谱仪硬件系统的研究与设计[D].成都,电子科技大学,2009.

[6]沈杰,宁瑞鹏,刘颖,等.一种减小梯度线圈产生的涡流的方法[J].物理学报,2006,55(6):3060-3066.

[7]Bartusek K,Kubasek R,Fiala P.Determination of preemphasis constants for eddy current reduction [J]. Measurement Science & Technology, 2010, 21(10): 105601-105609(9).

[8]王恢旺.核磁共振仪器梯度驱动子系统的设计与实现[D].中国科学院研究生院,2012.

[9]覃琴,宋海军,李长俊.基于μC/OS-II和NicheStack的嵌入式以太网接口设计 [J].国外电子测量技术,2013(5): 57-59.

[10]Nixon TW,Scott M I,Rothman D L,et al.Compensation of gradient-induced magnetic field perturbations.[J].Journal of Magnetic Resonance,2008,192(192):209-17.

[11]刘涛.常见磁共振伪影的产生原因及去除[J].中国现代药物应用,2010,04(20):229-229.

[12]刘正敏,周荷琴,武海澄.磁共振成像系统的一种快速涡流补偿方法[J].中国医疗器械杂志,2005,29(6):410-413.

[13]Zur Y.Eddy current compensation:US,US6191582[P]. 2001.

[14]徐勤,王鹤,蒋瑜,等.一种具有数字预加重的磁共振成像梯度波形发生器[J].波谱学杂志,2006,23(1):11-16.

[15]李思奇,蒋晓华.基于数字控制的磁共振成像用梯度放大器[J].中国电机工程学报,2010(27):83-89.

Design of MRIgradientmodule based on FPGA

DONG Hai-feng,ZHENG Zhen-yao,YAO Kai-wen,XIE Chen,CHEN Zhong

(Departmentof Electronic Science,Fujian Key Laboratory of Plasma and Magnetic Resonance,Xiamen University,Xiamen 361005,China)

Aiming at the needsof the digitalization andminiaturization of theMRIsystem,a design scheme ofgradientmodule based on FPGA is proposed in this paper.This scheme uses FPGA as the system control center,combined with high accuracy quad DAC and high resolution digital potentiometer to achieve the gradient pulse waveform generation,conversion,preemphasisprocessing and so on.Compared with the previous schemes,this scheme notonly effectively reduces theworkload of the host processor FPGA,butalso improves the digitalization and integration of the systemasmuch as possible.Through the software emulation and online debugging,results show that the scheme is stable and reliable,able to satisfy the needs of miniaturizedmagnetic resonance imaging system.

MRI;gradient;FPGA;pre-emphasis

TN830.4

A

1674-6236(2016)20-0005-04

2016-03-10 稿件编号:201603123

国家自然科学基金资助项目(11175149)

董海峰(1991—),男,安徽六安人,硕士研究生。研究方向:核磁共振仪器硬件电路原理及设计。