采用ARM的多FPGA串口命令选择配置及其应用

2016-11-04陈发堂主父文刚胡利伟

陈发堂 主父文刚 胡利伟

(重庆邮电大学重庆市移动通信技术重点实验室,重庆 400065)

采用ARM的多FPGA串口命令选择配置及其应用

陈发堂主父文刚胡利伟

(重庆邮电大学重庆市移动通信技术重点实验室,重庆400065)

针对嵌入式系统中的多FPGA配置问题,结合实际应用,设计了一种基于ARM、NAND Flash存储器和串口的多FPGA命令选择配置方案。该方案以含有4片FPGA的嵌入式系统为例,选用ARM作为主控芯片,使用超级终端输入配置文件选择命令,构建了基于TMS320C6A8168、XC3S400AN和NAND Flash的硬件平台,实现了根据设备的应用差别加载不同FPGA配置文件的功能。详细描述了系统的硬件构成、软件实现以及在TD-LTE无线综合测试仪表中的应用情况。与传统基于专用存储芯片的配置方法相比,该方案大大提高了多FPGA系统配置的灵活性,在通信电子领域具有一定的实用价值。

嵌入式系统FPGA配置ARMNANDFlash串口命令TD-LTE智能化

0 引言

随着电子应用领域的不断扩展,FPGA的应用正以空前的规模和速度渗透到各行各业,然而由于FPGA在容量、速度、资源等方面的局限性,利用单FPGA完成某些复杂嵌入式系统的设计存在很大困难。将复杂的系统设计分割为若干个独立模块,每个模块由单FPGA实现,并辅以多FPGA间的有效接口,能很好地解决FPGA规模的局限性[1-2]问题。

另一方面,随着通信设备的复杂化、多样化,采用多FPGA联合实现系统功能时,可通过选择加载不同的配置文件来实现同一套硬件设备“一机多能”的需求[3],特别是在通信仪表领域,这一应用尤为广泛。例如:在移动通信信令分析仪中,为了兼容全球移动通信系统(global system for mobile communication,GSM)、时分同步码分多址(time division synchronous code division multiple access,TD-SCDMA)、分时长期演进(time division long term evolution,TD-LTE)、频分双工长期演进(frequency division duplexing LTE,FDD-LTE)等不同的通信制式,就必须实现“一机多能”。该应用也提高了对多FPGA配置的智能化要求。

1 传统多FPGA系统的配置方案

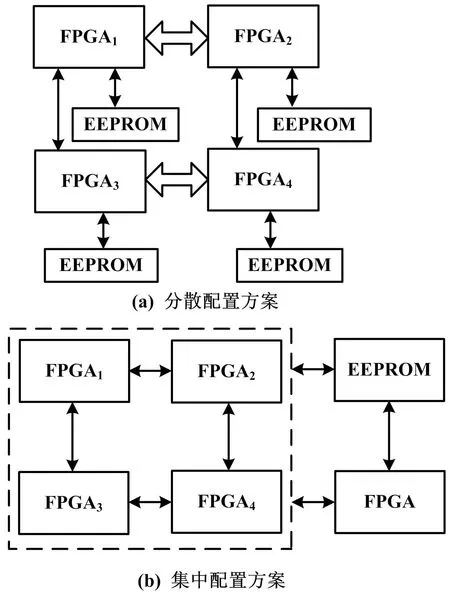

针对多FPGA系统的配置,传统的解决方案大致可分为两种:分散配置方案和集中配置方案。配置结构[4]如图1所示。

分散配置方案中,各FPGA分别采用主模式加载外部电可擦可编程只读存储器(electrically erasable programmable read-only memory,EEPROM)中的配置文件完成配置;待配置的FPGA产生配置时钟CCLK并控制整个配置过程的执行。由于该方案需要设计多个独立的配置电路,随着系统中FPGA数量的上升,PCB的设计变得更加困难,增加了系统的复杂度和成本。一旦想更换FPGA的配置文件,需重新向每片EEPROM烧写文件,十分不便。

集中配置方案采用Slave Select MAP模式[5-6]加载配置文件,配置时序和时钟由专用的FPGA发出。该方案将全部配置文件集中存储在一片EEPROM上,会出现EEPROM容量不足以及系统中的多片FPGA无法在不同版本的配置文件之间进行智能切换等问题。

图1 传统配置方案的配置结构图Fig.1 The configuring structure of traditional configuration scheme

2 多FPGA串口命令配置原理

针对传统方法在多FPGA系统“智能”配置上的不足,本文设计了基于ARM、NAND Flash和串口的多FPGA命令选择配置方案。该方案使用ARM的人机交互接口读取选择命令,控制接口和数据接口按照配置时序完成配置。用户可根据设备不同的功能要求,自主选择FPGA配置文件进行智能加载。

2.1单FPGA 16bit Slave SelectMAP配置原理

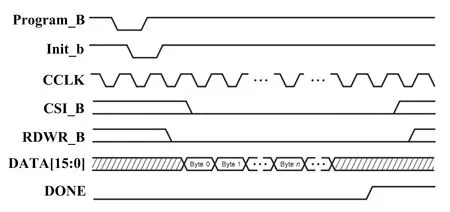

本方案单片FPGA的配置采用16 bit Slave Select MAP模式,配置时序如图2所示。

图2 配置时序图Fig.2 Sequence chart of configuration

系统上电时,ARM发送到PROGRAM_B引脚上的逻辑低电平会复位配置逻辑,使FPGA处于清空配置存储器状态,并使INIT_B信号保持低电平,以表明配置存储器正被清空。ARM释放PROGRAM_B引脚后,FPGA在清空所有配置存储器后拉高INIT_B引脚,并在INIT_B的上升沿,由自动采样模式选择引脚M[2:0]以决定配置模式,SelectMAP模式对应的M[2:0]引脚值为0b110。ARM检测到INIT_B引脚的高电平后,将配置文件写入FPGA。若写入的配置文件循环冗余检验(cyclic redundancy check,CRC)成功,FPGA会拉高DONE引脚,表明配置成功;否则,INIT_B引脚被拉低,配置失败。

2.2基于ARM的多FPGA串口命令选择配置原理

本方案选用高性能处理器ARM作为系统的主控芯片,控制整个配置过程的执行[7];NAND Flash作为系统存储器,存储通用启动装载(universal boot loader,U-boot) 映像文件、配置程序以及所有的配置文件。上电后ARM执行根据硬件信息定制的U-boot[8-9],并通过串口在超级终端上打印配置文件选择信息及对应的设备功能说明;然后,根据用户输入的命令,先将所选配置文件从NAND Flash拷贝至内存DDR,再按照16 bit Slave Select MAP时序,通过辅助FPGA,将DDR中的配置数据分次写入待配置的FPGA中,完成对全部FPGA的配置。

3 多FPGA串口选择配置的实现

本方案选用Ti公司的双核处理器TMS320C6A8168作为系统主控芯片,其具有最高可达1.2 GHz的ARM Cortex-A8核与1 GHz 的C674x数字信号处理(digital signal process, DSP)核,极大地增强了系统多任务处理能力及数学运算能力。NAND Flash选用位宽16位、存储容量2 GB的MT29F2G16芯片。

辅助FPGA采用Spartan-3AN系列的FPGA XC3S400AN。该系列的FPGA专用于系统集成度和安全性高的关键非易失性领域,是业界比较先进的非易失性FPGA解决方案[10],可提高配置过程的安全性和可靠性。

3.1系统硬件设计

ARM的通用内存控制器(general purpose memory controller,GPMC )接口与NAND Flash、DDR以及辅助FPGA相连,用于发出配置命令、配置时钟和配置数据;NAND Flash存储方案的所有代码,在配置前用CCS5.0软件和JTAG仿真器将各类文件和代码烧入芯片。辅助FPGA与4片待配置FPGA相连,可实现ARM与待配置FPGA之间的控制信号传递及配置数据交互。

通过XC3S400AN TMS320C6A8168的GPMC_DATA[15:0]引脚和待配置FPGA的DATA[15:0]引脚,以及TMS320C6A8168的GPMC_CLK引脚和待配置FPGA的CCLK引脚,均可直接建立连接。所以在配置过程中,TMS320C6A8168 GPMC_CLK引脚和GPMC_DATA[15:0]引脚分别发出的写时钟和配置数据会通过XC3S400AN直接作用于待配置FPGA,从而实现将DDR中的配置数据直接写入待配置FPGA中的功能。

3.2系统软件实现

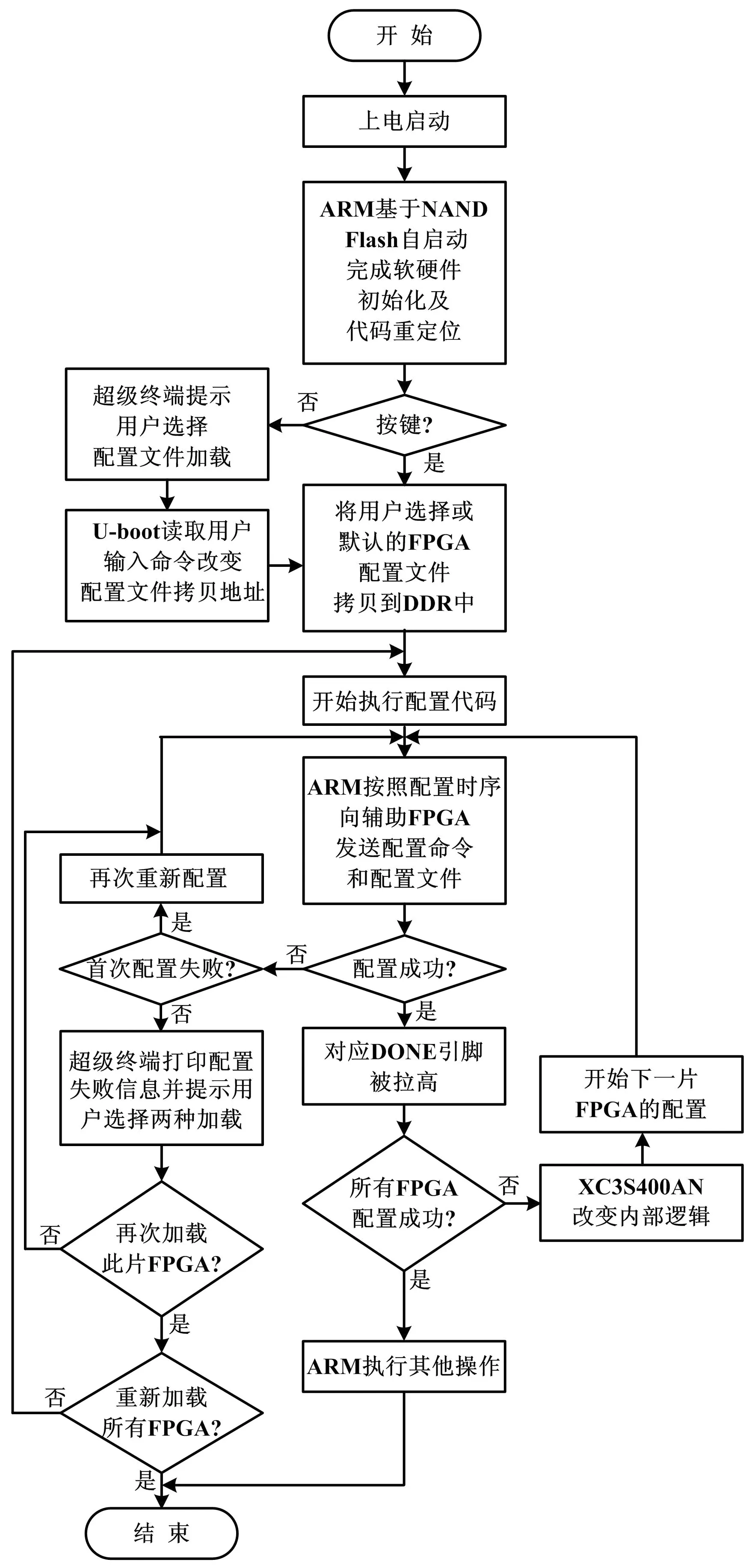

软件实现主要分为ARM自启动和配置代码执行这两个过程,总流程如图3所示。

图3 软件实现总流程图Fig.3 The overall flowchart of software realization

系统上电后,ARM利用NAND Flash中的U-boot代码自启动,初始化系统软硬件环境,然后将用户选择加载的4个配置文件拷贝到DDR中,再执行配置代码。配置代码利用FPGA逻辑可变性,按照Slave Select MAP时序将DDR中的配置数据通过XC3S400AN依次写入4片待配置FPGA中,实现对所有FPGA的配置。

3.2.1基于NAND Flash的自启动

TMS320C6A8168自动加载NAND Flash上的U-boot完成自启动,分为ROM Code(read only memory code)执行阶段和U-boot执行阶段[11]。

①ROM code执行阶段。

ROM code是ARM ROM区域的代码,其主要功能是对ARM进行安全启动的初始化、堆栈和看门狗的设置、系统时钟和RAM的初步配置以及启动模式选择引脚MBOOT[4:0]的采样。ROM code根据采样值创建自启动设备列表,按设备列表的顺序到相应设备搜寻启动文件U-boot Image并执行。本方案将MBOOT[4:0]引脚连接的拨码开关设置为0b10010,创建的启动设备列表顺序依次为NAND Flash、NANDI2C、SPI、UART。

不同的设备类型对应不同的自启动过程。ARM在搜寻启动文件前会先判断当前的启动设备类型。由于NAND Flash是存储类的非可直接执行设备,ARM无法在NAND Flash中直接执行启动文件,因此,检测到启动文件后,ARM会根据U-boot头部的重定位信息把它从NAND Flash拷贝至TI_LOAD_ADDR地址处,完成第一次代码重定位。本方案在U-boot配置文件config.mk中,将此地址设置为ARM第二片RAM的起始地址。

②U-boot执行阶段。

重定位成功后,ARM执行RAM中的U-boot,完成软件环境的设置以及硬件接口和外设的初始化,然后将U-boot Image从NAND Flash拷贝至DDR的TEXT_BASE地址处执行。TEXT_BASE在config.mk中设为0x80700000。

U-boot第二次代码重定位完成后,超级终端显示4 s倒计时,移动通信信令分析仪默认加载各FPGA的配置文件,以实现设备TD-LTE功能。如果用户想切换仪表功能或更换任意FPGA配置文件,只需在倒计时内在键盘按下任意键便可进入U-boot串口命令模式,同时超级终端上会打印出仪表功能及配置文件版本命令选择菜单。

用户可以通过输入数字“1”~“3”来选择不同的设备功能,或者输入字母“a”~“p”来逐一选择加载配置文件。U-boot读取串口输入命令后,会根据命令修改对应FPGA位于NAND Flash中的配置文件拷贝地址。将配置文件从NAND Flash拷贝到DDR后,即完成了所选FPGA配置文件的更换,实现了用户通过串口自主选择配置文件加载的功能。

完成配置文件选择后,U-boot将用户选择的4个配置文件从NAND Flash的相应地址分别拷贝到DDR存放FPGA1~FPGA4配置文件的起始地址处,操作系统文件拷贝至0x90000000处,配置代码拷贝至ARM第一片RAM的起始地址处。

上述代码拷贝结束后,ARM即完成了基于NAND Flash的自启动,并跳转执行配置代码。

3.2.2配置代码的执行

配置代码中,ARM按照Slave Select MAP时序发出的配置信号,通过XC3S400AN首先作用于FPGA1。在FPGA1等待配置数据写入时,ARM将DDR中的FPGA1配置文件写入某虚拟地址中,GPMC接口的GPMC_DATA[15:0]引脚便产生配置数据,GPMC_CLK引脚产生写时钟,且通过XC3S400AN充当待配置FPGA的配置时钟CCLK,GPMC[15:0]上的配置数据在GPMC_CLK的驱使下通过XC3S400AN直接写入FPGA1。

FPGA1配置成功后,其DONE引脚变为高电平,XC3S400AN根据DONE信号的变化改变内部逻辑,ARM再次发出的配置信号和数据将作用于FPGA2。同理,首先完成FPGA2的配置,然后继续按照上述步骤完成剩余2片FPGA的配置,从而实现对所有FPGA的配置。

如果某片FPGA首次配置没有成功,ARM会自动对此片FPGA执行再次配置。如果第二次配置仍然失败,则在超级终端上打印配置失败信息选择,提示用户再次配置此FPGA或重新配置所有FPGA。该方法提高了调试的效率。

完成4片FPGA的配置后,启动操作系统,执行其他任务,实现了ARM处理器的多用途,增强了本方案在各类设备中的通用性。

4 方案具体应用及性能数据测试

本文设计的配置系统已经成功应用于移动通信信令分析仪。该仪表使用的是4片Xilinx公司生产的Virtex-6系列FPGA XC6VSX475T,根据测试对象及环境的不同,通过智能加载不同的配置文件使仪表兼容了GSM、TD-SCDMA、TD-LTE、FDD-LTE四种通信网络,可应用于试验室、外场等不同的测试环境以及5 M、10 M、15 M、20 M四种带宽模式,模拟了单小区单用户、单小区多用户、单天线、多天线等配置,实现了“一机多能”的应用需求。

在该信令分析仪上对本方案的时间参数进行测试,选用的配置文件格式为.bit,采用16 bit Slave Select MAP模式对4片FPGA进行配置。 在U-boot中,将GPMC与DDR的时钟频率分别设定为125 MHz、500 MHz,在不同的ARM时钟频率和平均配置文件大小下,多次测量得出系统启动并完成FPGA配置所需的总时间。

随着配置文件的增大,配置完成总时间逐渐延长。在U-boot中及时开启指令/数据缓存并适当提高ARM时钟频率,有助于缩短配置时间。

5 结束语

随着多FPGA系统的应用越来越广泛,嵌入式系统对多FPGA的加载提出了更高的要求,尤其是要保证加载过程中的可选择性和智能性。本文提出的多FPGA系统加载方案改进了传统方法的不足,并从系统结构、原理设计、硬件构造、软件实现等方面给出了具体实现方案。本方案的软、硬件设计较完整、独立,无需过多的修改即可移植到各种嵌入式系统中使用,在通信电子、计算机领域具有一定的应用价值。

当然,由于本设计方案的配置存储器采用的是NAND Flash,虽然它可以为每片FPGA存储多个版本的配置文件,但是受到现代工艺的制约,其读取速度较慢,这也直接导致了配置时间的延长。如果在成本可接受范围内采用大容量的NOR Flash或者其他高速存储芯片,将大大减少配置时间。此外,如果对保密性没有特殊要求,可以将配置文件存放于SD卡中,使用SD卡启动加载,这样更方便、快捷。

[1] 张倩莉,于芳,刘忠立,等.结合用户约束文件的高效多FPGA系统分割方法[J].哈尔滨工业大学学报,2012,44(7):144-148.

[2] LADDHA S,DE K B.EDA tools and design methodology for multi-FPGA designing/prototyping[EB/OL].[2015-01-26]http://www.design-euse.com/articles/22074/for-multi-fpga-designing-prototyping.html.[3] 陈曦,沈佐峰.一种可靠的 FPGA 动态配置方法及实现[J].通信技术,2012,45(3):105-110.

[4] 张承畅.多FPGA系统的关键问题及应用研究[D].重庆:重庆大学通信工程学院,2011.[5] XLINX Inc.Virtex-6 FPGA configuration user guide.[EB/OL].[2015-01-26].http://www.xilinx.com/support/d ocumentation/user_guides/ug360.pdf.

[6] 纪斌.Xilinx FPGA上电时序分析与设计[J].电讯技术,2012,52(4):591-594.

[7] MARK N,PEATTIE M.Using a microprocessor to configure xilinx FPGAs via slave serial or selectMAP mode [EB/OL].[2015-01-26].http://www.xilinx.com/support/documentation/application_notes/xapp502.pdf.

[8] 蔡利平,任家富,童锐,等.基于ARM的NAND Flash启动分析与移植[J].计算机工程与设计,2012,33(3):931-935.

[9] 杨宗富.基于ARM的系统启动过程研究与系统移植[D].北京:北方工业大学,2014.

[10]XILINX Inc.Spartan-3AN FPGA family data sheet[EB/OL].[2015-01-26].http://www.xilinx.com/ support/ documentation/data_sheets/ds557.pdf.

[11]Texas Instruments Inc.TMS320DM816x DaVinci video processors technical reference manual [EB/OL].[2015-01-26].http:// w.ti.com/lit/ug/sprugx8b/sprugx8b.pdf.

Design of the ARM-based Multi-FPGA Serial Port Command Selection Configuration and Its Application

Aiming at the Multi-FPGA configuration issue in embedded system and combining the practical applications,a Multi-FPGA command selection and configuration scheme based on ARM,NAND Flash memory and serial ports is proposed.With the example of the embedded system which contains 4 pieces of FPGA chips,ARM is selected as the main control chip,and Hyper Terminal is used to input configuration file and select command,so a hardware platform based on TMS320C6A8168,XC3S400AN and NAND Flash is built,which achieves the function that selecting different FPGA configuration file to load according to the difference from applications.The hardware structure,software implementation and practical application in TD-LTE wireless comprehensive test instrument are introduced at great length.Compared with the traditional configuration method based on the dedicated memory chips,the system greatly improves the flexibility of FPGA system configuration,thus it possesses certain reference value in electronic communication field.

Embedded systemFPGAConfigurationARMNANDFlashSerial port commandTD-LTEIntellectualize

陈发堂(1965—),男, 1999年毕业于北京邮电大学应用数学专业,获硕士学位,研究员;主要从事TD-SCDMA移动通信系统和TD-LTE系统的开发。

TH3;TP273+.5

ADOI:10.16086/j.cnki.issn 1000-0380.201610024

国家科技重大专项基金资助项目(编号:2011ZX03001-002)。

修改稿收到日期:2015-09-21。