硅衬底GaN基LED薄膜芯片的应力调制

2016-11-03汤英文熊传兵王佳斌

汤英文, 熊传兵, 王佳斌

(1. 闽南师范大学 物理与信息工程学院, 福建 漳州 363000; 2. 南昌大学 国家硅基LED工程技术研究中心, 江西 南昌 330047)

硅衬底GaN基LED薄膜芯片的应力调制

汤英文1*, 熊传兵1, 王佳斌2

(1. 闽南师范大学 物理与信息工程学院, 福建 漳州363000;2. 南昌大学 国家硅基LED工程技术研究中心, 江西 南昌330047)

将Si衬底GaN基LED外延薄膜经晶圆键合、去硅衬底等工艺制作成垂直结构GaN基LED薄膜芯片,并对其进行不同温度的连续退火,通过高分辨X射线衍射(HRXRD)研究了连续退火过程中GaN薄膜芯片的应力变化。研究发现:垂直结构LED薄膜芯片在160~180 ℃下退火应力释放明显,200 ℃时应力释放充分,GaN的晶格常数接近标准值。继续升温应力不再发生明显变化,GaN薄膜的晶格常数只在标准晶格常数值附近波动。扫描电子显微镜给出的bonding层中Ag-In合金情况很好地解释了薄膜芯片应力的变化。

硅衬底; GaN; 应力; XRD; Ag-In

1 引 言

LED已广泛应用于显示和照明领域[1-4]。近年来,LED的晶体生长、器件结构及器件制备等一直是产业界及研究领域的热点。目前用来生产商品化的GaN基LED器件的衬底主要有3种:Si、SiC和蓝宝石。与SiC和蓝宝石相比,Si衬底具有成本低、尺寸大、质量高、导电性能好[5]等优点,但Si与GaN材料之间也具有更大的晶格失配(17%)和热失配(56%),晶格常数和热膨胀系数之间的差异使得Si衬底与GaN薄膜之间存在应力[6-7]。应力不只存在于外延薄膜中,也会转移到Si衬底GaN薄膜垂直结构器件中。应力过大不仅会导致GaN薄膜出现开裂现象,严重影响芯片的良率,而且对LED的发光光强、波长和电流电压也存在着一定的影响。

为了缓解GaN薄膜外延生长的应力,目前的解决办法有生长缓冲层、使用图形化衬底等,虽然能消除一部分应力,但残余应力仍然很大,这是由膨胀系数和晶格常数决定的。虽然硅衬底GaN基LED得到了广泛的市场认可,但要进入高端LED应用市场还面临可靠性不足的问题。应力是造成芯片可靠性问题的最主要原因,要想有效释放外延GaN薄膜给芯片带来的残余应力只能通过后续的芯片工艺。科研人员研发了各种释放应力的办法,但是总是存在一些后续问题,还需进一步完善。

本文通过优化制作垂直结构器件的晶圆键合(Bonding)及对去硅后的LED薄膜芯片进行热处理等工艺来消除芯片中的应力。为了了解应力的变化,对LED薄膜芯片进行连续退火,每个温度点退火后的LED薄膜芯片用X射线衍射法测量其应力随退火温度的变化情况,并用扫描电子显微镜(SEM)观察Bonding层Ag、In熔化合金情况来解释应力变化。

2 实 验

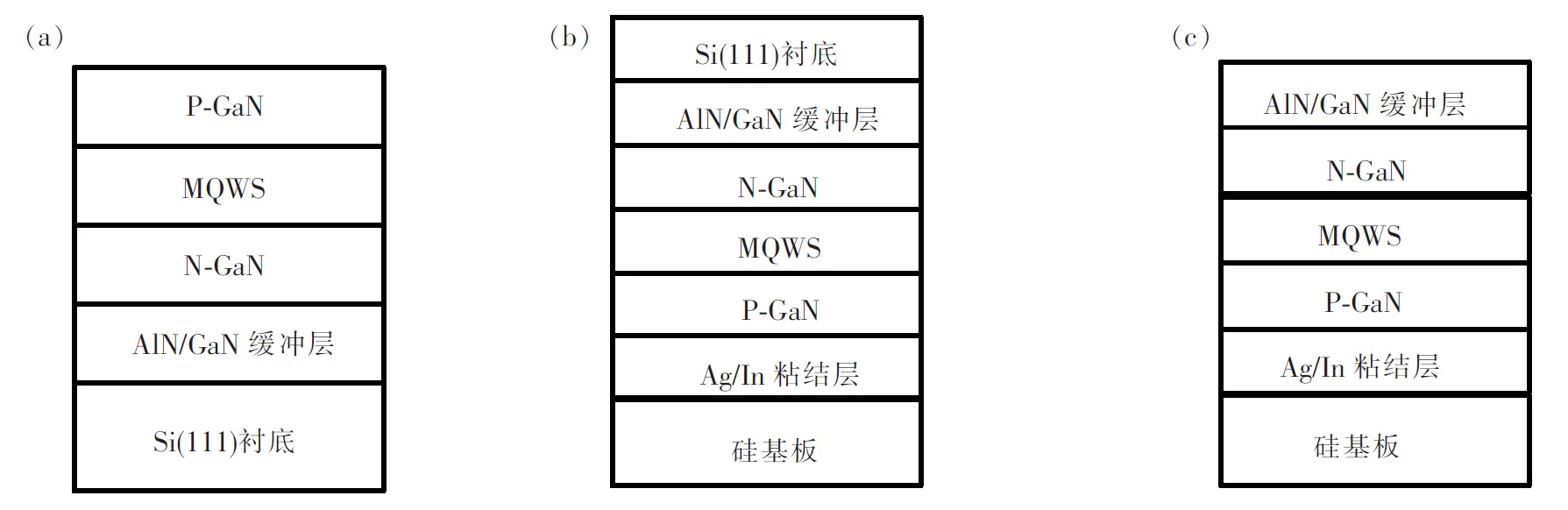

采用MOCVD生长实验所需硅衬底GaN基蓝光LED外延薄膜,生长方法见文献[5]。将硅衬底外延薄膜经过p型激活、P电极蒸发合金、粘结层蒸发、键合(Bonding)、去硅衬底等工艺步骤做成样品,样品详细制作方法见文献[8], 样品制作过程如图1所示。

图1样品制作过程。(a)硅衬底GaN外延薄膜;(b)键合结构;(c)去硅衬底后的GaN。

Fig.1Fabricating steps of the sample. (a) GaN LED film grown on Si. (b) Wafer bonding. (c) Thin film LED chip after substrate removing.

将去硅后的晶圆片切割成25个小块样品,在晶圆中间取相邻位置的8个样品,编号为1~8,放入有氮气保护的合金炉中退火,退火温度分别为160,180,200,220,240,260,300 ℃,退火时间为15 min,升温速率为1 ℃/min。每在一个温度点退火后,将样品1用HRXRD测量GaN薄膜的晶格常数,同时另外取一个样品做SEM分析,观察其粘结层金属合金情况。

荷兰帕纳科高分辩衍射仪(XPert Pro MRD)用于研究芯片中应力的变化,衍射仪的靶材料为Cu,X射线波长为0.154 056 nm,X射线管工作电压为40 kV,电流为40 mA,测试精度为0.000 1°,扫描范围为0.4°~160°。Hitachi超高分辨率场发射扫描电子显微镜SU8010用于观察Bonding层Ag、In熔化合金情况,加速电压为15 kV。

3 结果与讨论

3.1HRXRD图谱计算与分析

当材料受到应力作用时,晶格间距会受应力的影响而发生变化。晶格常数可以通过提高测量衍射角的变化来计算,通过晶格常数变化可以判断材料的应力变化[9-11]。

为了消除仪器零点误差Δθ0,我们采用同一晶面(hkl) 的不同级数法来确定衍射峰的准确位置。设某一晶面的一级、二级衍射角的真值分别为θ1、θ2,实际测量值分别为ω1、ω2,则

(1)

根据布拉格公式2dsinθ=nλ(n为整数),有

(2)

那么

(3)

可得

(4)

那么布拉格衍射角为

由布拉格方程可计算出晶面间距

(6)

由于Si(111)面衬底上长出的GaN薄膜为六角晶系的纤锌矿结构,则有

(7)

(8)

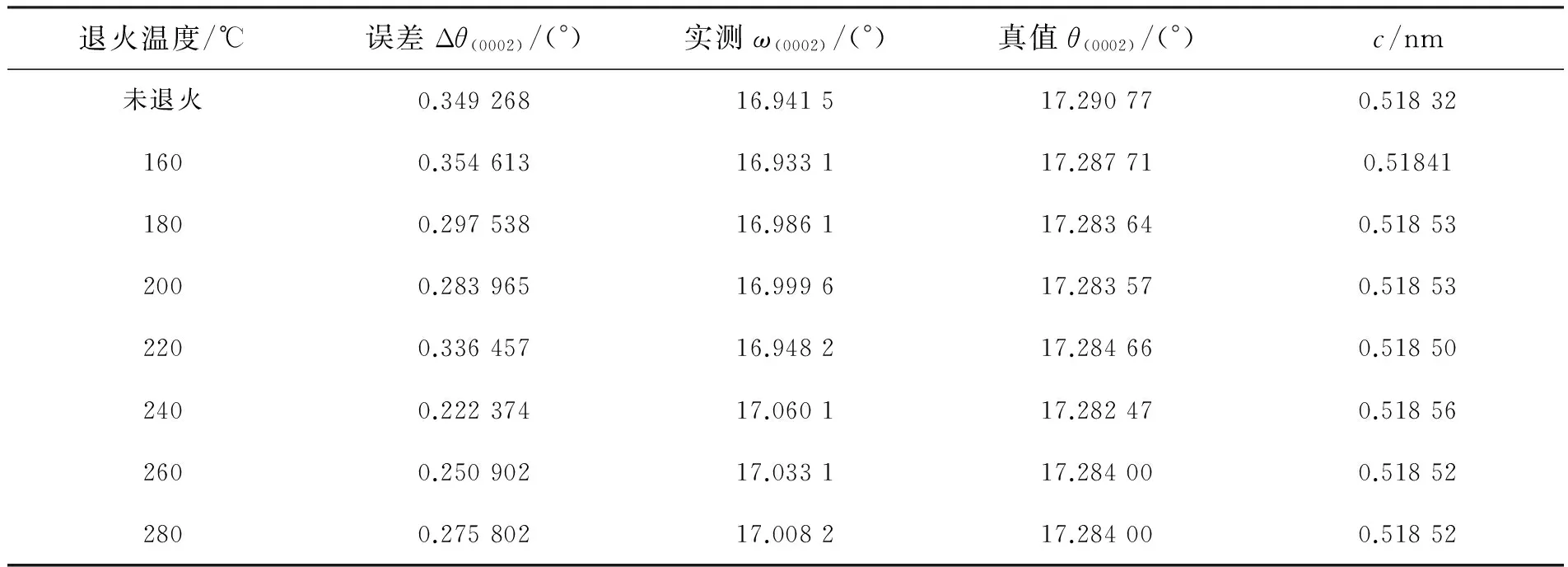

经上面公式计算出零点误差和布拉格衍射角的真值,就可以算出GaN的a轴和c轴的晶格常数,计算结果见表1、表2。

表1 样品1(0002)面的零点误差、实测值、布拉格真值和晶格常数c

表2 样品2)面的零点误差、实测值、布拉格真值和晶格常数a

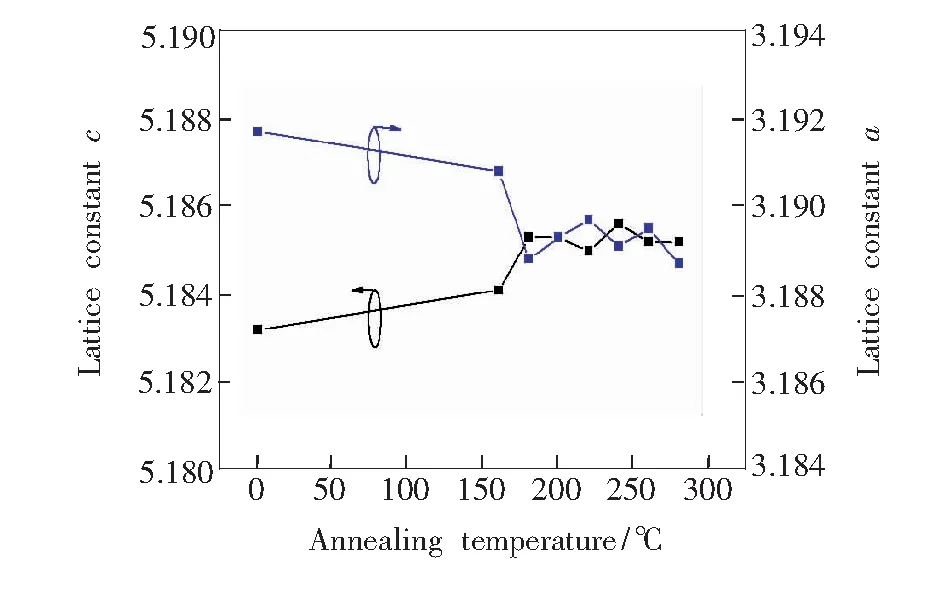

为了直观地看到应力的变化,将表1、2制成图2。可以看出,未退火的薄膜芯片处于张应力状态,这和由于晶格失配和热失配导致硅衬底和GaN之间形成张应力的结论相符。随着退火温度的升高,GaN薄膜的a值和c值逐渐发生改变,a值呈减小趋势,c值呈增大趋势。退火温度在160~180 ℃时,a值和c值变化明显,200 ℃时与GaN晶格常数标准值(a=3.189 1,c=5.185 5)接近。继续升温,a值和c值不再发生明显变化,只在小范围内波动。这说明随着退火温度的逐渐升高,薄膜中的应力是在逐渐释放的;160~180 ℃时应力释放明显,200 ℃时薄膜应力释放充分,再继续升温,其应力不再发生明显变化。

图2 连续退火中薄膜芯片GaN的应力变化情况Fig.2 Stress in GaN film as a function of annealing temperature

3.2SEM图分析

去硅后的LED薄膜芯片由于受到Bonging的基板束缚,应力无法释放,通过升温退火达到了释放应力的目的。我们通过扫描电子显微镜观察Bonding层中Ag-In合金情况来分析其应力释放机制。

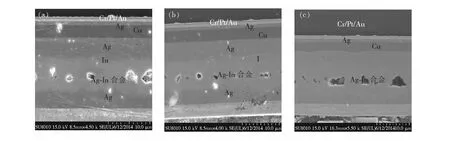

图3是未退火以及180 ℃、200 ℃退火后的Bonding层Ag-In合金的SEM截面图。GaN芯片薄膜在上表面,P型GaN的下面金属依次为Ag反射镜、Ag反射镜保护层金属Cr/Pt/Au、阻挡金属Ag/Cu、粘结金属In、阻挡金属Ag/Cu、导电基板。根据EDS能谱分布图和芯片的结构,已知的元素已标示在图中。从图中可以看出,去硅衬底后还未退火的芯片的Bonding层中的金属扩散不充分,存在较明显界面,低熔点的In单质较多;较低的退火温度就可使In熔化,芯片下面金属处于熔化状态时,芯片就自由伸展,芯片释放了应力;随着退火温度的逐渐升高,Ag和In之间发生相互扩散,界面逐渐模糊,处于可熔状态的In也随之减少;当温度达到200 ℃时Ag-In界面消失,合金最为充分,应力释放也最为充分,继续升温则合金区域变化不明显,对应着薄膜应力变化也不明显。

图3 Ag-In合金的SEM图。 (a) 退火前;(b) 180 ℃退火;(c) 200 ℃退火。

4 结 论

对去除硅衬底后采用导电硅基板作支撑的GaN基LED薄膜进行连续退火,通过高分辨X 射线衍射( HRXRD) 和扫描电子显微镜(SEM) 研究了连续退火过程中GaN 薄膜应力变化和Bonding层金属之间的合金情况。退火温度在160~180 ℃时,应力释放明显;芯片的晶格参数在200 ℃退火时最接近标准值,此时应力释放最为充分;继续升温则应力值变化不大,晶格参数在标准值附近波动。未退火前,Bonding层的金属界面较明显;随着温度的升高,Ag和In相互扩散形成合金;当温度达到200 ℃时,Bonding层中金属界面消失,合金最为充分,应力释放也最为充分。可见,通过键合层的设计及退火可以达到消除芯片应力的目的,为受应力困扰的其他芯片的制造提供了思路。本方法在硅衬底LED芯片的生产中得到了应用,芯片的良率及可靠性得到极大的提高,解决了大尺寸硅衬底GaN基LED在制造过程中良率很低、晶圆翘曲等一系列问题,为硅衬底LED的大规模市场化奠定了基础。

[1] CRAWFORD M H. LEDs for solid-state lighting: performance challenges and recent advances [J].IEEEJ.Sel.Top.Quant.Electron., 2009, 15(4):1028-1040.

[2] NAKAMURA S. The roles of structural imperfections in InGaN-based blue light-emitting diodes and laser diodes [J].Science, 1998, 281(5379):956-961.

[3] 赵玲慧,张连,王晓东,等. 基于InGaN/GaN多量子阱双波长发光二极管生长及发光性能 [J]. 光子学报, 2013, 42(10):1135-1139.

ZHAO L H, ZHANG L, WANG X D,etal.. Growth and optical properties of InGaN/GaN dual-wavelength light-emitting diodes [J].ActaPhoton.Sinica, 2013, 42(10):1135-1139. (in Chinese)

[4] 李正凯,严启荣,罗长得,等. GaN垒层厚度渐变的双蓝光波长发光二极管 [J]. 光子学报, 2013, 42(7):757-762.

LI Z K, YAN Q R, LUO C D,etal.. Dual-blue wavelength light-emitting diodes based on varied GaN barrier thickness [J].ActaPhoton.Sinica, 2013, 42(7):757-762. (in Chinese)

[5] MO C L, FANG W Q, PU Y,etal.. Growth and characterization of InGaN blue LED structure on Si(111) by MOCVD[J].J.Cryst.Growth, 2005, 285(3):312-317.

[6] XIONG C B, JIANG F Y, FANG W Q,etal.. Different properties of GaN-based LED grown on Si(111) and transferred onto new substrate [J].Sci.ChinaSer. E, 2006, 49(3):313-321.

[7] 熊贻婧,张萌,熊传兵,等. Si衬底GaN基LED外延薄膜转移至金属基板的应力变化 [J]. 发光学报, 2010, 31(4):531-537.

XIONG Y J, ZHANG M, XIONG C B,etal.. Investigation of strain of GaN light-emitting diode films transferred to metal substrate from Si(111) [J].Chin.J.Lumin., 2010, 31(4):531-537. (in Chinese)

[8] 江风益,刘军林,王立,等. 硅衬底高光效GaN基蓝色发光二极管 [J]. 中国科学: 物理学 力学 天文学, 2015, 45(6):067302-1-19.

JIANG F Y, LIU J L, WANG L,etal.. High optical efficiency GaN based blue LED on silicon substrate [J].Sci.Sin.Phys.,Mech.Astron., 2015, 45(6):067302-1-19. (in Chinese)

[9] 王雪蓉,魏莉萍,郑会保,等. 利用高分辨X射线衍射技术计算铝镓氮外延膜的晶格参数 [J]. 分析测试技术与仪器, 2010, 16(3):152-156.

WANG X R, WEI L P, ZHENG H B,etal.. Study on crystal lattice constant of AlxGal-xN epitaxial film by high resolution X-ray diffraction technique [J].Anal.Test.Technol.Instrum., 2010, 16(3):152-156. (in Chinese)

[10] KISIELOWSKI C, KRüGER J, RUVIMOV S,etal.. Strain-related phenomena in GaN thin films [J].Phys.Rev. B, 1996, 54(24):17745-17753.

[11] DETCHPROHM T, HIRAMATSU K, ITOH K,etal.. Relaxation process of the thermal strain in the GaN/a-Al2O3hetero-structure and determination of the intrinsic lattice constants of GaN free from the strain [J].Jpn.J.Appl.Phys., 1992, 31(10B):L1454-L1456.

汤英文(1969-),男,湖南怀化人,博士,教授,2006年于中国科学院上海技术物理研究所获得博士学位,主要从事GaN基宽禁带半导体光电器件的研究。

E-mail: t-y-w2002@sohu.com

Stress Modulation of GaN Based LED Thin Film Chip on Silicon Substrate

TANG Ying-wen1*, XIONG Chuan-bing1, WANG Jia-bin2

(1.CollegeofPhysicsandInformationEngineering,MinnanNormalUniversity,Zhangzhou363000,China;2.NationalEngineeringTechnologyResearchCenterforLEDonSiSubstrate,NanchangUniversity,Nanchang330047,China)

,E-mail:t-y-w2002@sohu.com

Vertical structured thin film GaN LEDs on Si substrate were fabricated by wafer boding and substrate removing process. The LED chips were annealed at various temperatures, and high-resolution X-ray diffraction (HRXRD) measurements were performed to analyze the stress in GaN films. The results show that the annealing within 160-180 ℃ can obviously reduce the stress in GaN thin film, and the stress can be fully released at 200 ℃ and the measured lattice constants are close to the standard values of bulk GaN. Annealing at higher temperatures, the lattice constants of the GaN films only slightly fluctuate around the standard values. Scanning electron microscope (SEM) was used to analyze the cross-sectional morphology of the bonding layers. The evolution of the stress in GaN film can be well explained by the alloying degree of the Ag-In layers.

Si substrate; GaN; stress; XRD; Ag-In

1000-7032(2016)08-0979-05

2016-03-15;

2016-04-18

国家科技部支撑计划(2011BAB32B01)资助项目

TN304

ADOI: 10.3788/fgxb20163708.0979