IIC总线和LVDS在高速数据传输接口电路中的应用研究

2016-10-28王红亮何少恒邸丽霞

王红亮,刘 伟,何少恒,邸丽霞

(1.中北大学 电子测试技术重点实验室,太原 030051;2.北方自动控制技术研究所,太原 030006)

IIC总线和LVDS在高速数据传输接口电路中的应用研究

王红亮1,刘 伟1,何少恒1,邸丽霞2

(1.中北大学 电子测试技术重点实验室,太原 030051;2.北方自动控制技术研究所,太原 030006)

当前在高速数据系统中,LVDS接口已被广泛应用,为实现同系列设备之间的智能识别、自动握手以及LVDS高速数据链路通信质量的检测,利用FPGA的IO电路结构,设计一种模拟IIC总线协议电路,该IIC总线高效地实现设备之间的信息双向传递;同时利用FPGA内部丰富寄存器资源设计PRBS码型电路来检测LVDS接口芯片电路误码率;实际测试表明该多通道LVDS传输方式在2米长电缆连接能够实现数据的稳定、低误码率传输,并且在时钟频率为100MHz时,数据传输速率高达4.68Gb/s。

IIC总线、PRBS编码、LVDS信号

0 引言

随着AD采样率的提高,数字雷达接收机输出的I/Q数据,不断朝着高速化演变,如何实现高带宽的数字基带信号在接口电路中传输,成为业界亟待解决的难题[1]。LVDS是一种低振幅差分信号技术,它以几百兆甚至千兆比特每秒的速率传输差分数字信号;差分数字信号抗干扰能力强,适合远距离传输,越来越多应用于高速数字接口电路当中[2]。设备之间数据信息通过philips公司推出的一种用于设备之间互连的双向二线制同步串行总线--IIC总线(Inter-Integrated Circuit,集成电路总线)传递,只需要通过两根电缆,设备之间就可以进行信息传输。

由于FPGA并行处理数据能力强,选用48位并行的LVDS驱动芯片、LVDS解串芯片与FPGA相连;芯片内部固化的串化、解串电路,把数据与时钟串化为8路差分信号,速率为单端信号的7倍,从而实现差分信号在电缆中高速传输;同时利用FPGA的I/O电路结构和内部资源模拟IIC总线协议,实现了同IIC总线协议电路功能相同的双向传输机制。

1 系统的总体构成

如图1所示传输系统主要包括AD采集设备、IQ数据传输设备,其工作原理:AD采样芯片把模拟中频信号转换为数字信号;经过本振电路数字下变频,变换为数字基带信号[3],再由FGPA的FIR算法滤波之后,产生正交的I数据与Q数据;LVDS信号发送电路把I、Q数据与时钟转换为差分信号对,并通过LVDS电缆发送给I/Q数据传输板卡;I/Q数据传输板上接收芯片解串接收到的对应差分信号对转换为并行同步TTL或CMOS电平。FPGA通过IIC总线实现两个设备间的数据通信,内部FIFO可以对解析后的数据进行缓存,并通过PCIe总线上传至计算机进行处理、分析。

2 IIC电路与LVDS电路设计

2.1 IIC总线硬件电路设计

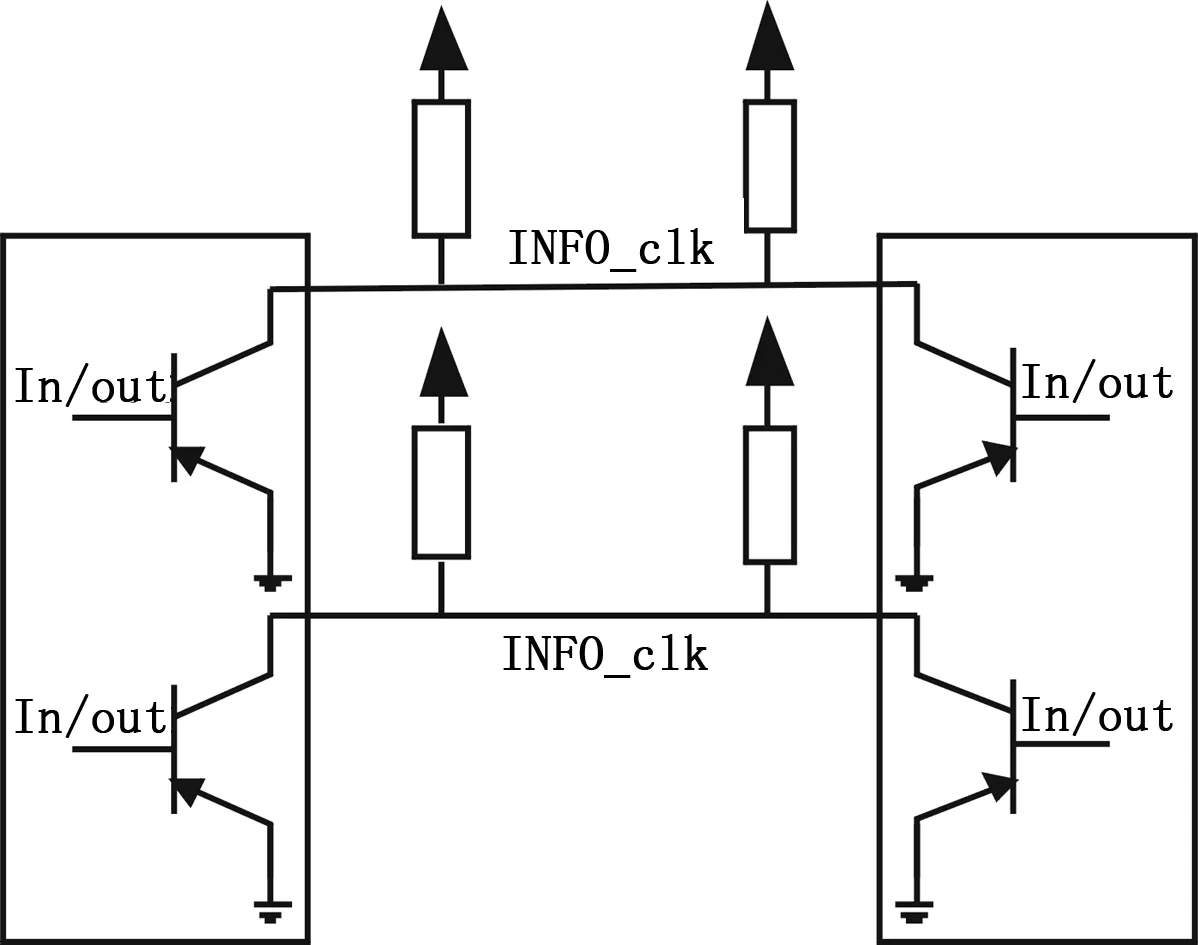

IIC总线是一种用于IC器件之间连接的双向二线制总线,优点是占用空间小,多主控,方便灵活设计电路。该总线含有两根信号线,一根为SDA(数据线),一根为SCL(时钟线)。任何时候时钟信号都是由主控器件产生。IIC总线在传送数据的过程中,主要有3种控制信号:起始信号,结束信号,应答信号。为便于主、从设备互相控制,采用具有线与功能的集电极开路或者漏极开路的电路结构。在电路设计中,集电极开路的总线上没有高电平,所以要加入1k的上拉电阻,上拉电压选用FPGA 的IO电平标准3.3V,同时低电平最大输出电压为0.8V,FPGA管脚最小驱动电流6 mA[4],满足三极管饱和管压降的需求。IIC总线硬件电路,如图2所示。

图1 系统总体构成

图2 IIC总线硬件电路

按照IIC协议的标准,在时钟频率为100 kHz时,INFO_clk与INFO_dat信号最大上升时间为1 000 ns,最大下降时间为300 ns。上升沿建立时间是由上拉电源对上拉电阻线上电容的充电时间决定的,可以用RPCL来近似计算,上拉电阻RP=1 k、时钟频率100 kHz时,RPCL乘积常数为1 000 ns,可得CL最大值为1 nF。所以要注意PCB走线、连接器线容不要大于1 nF。

2.2 LVDS硬件电路设计

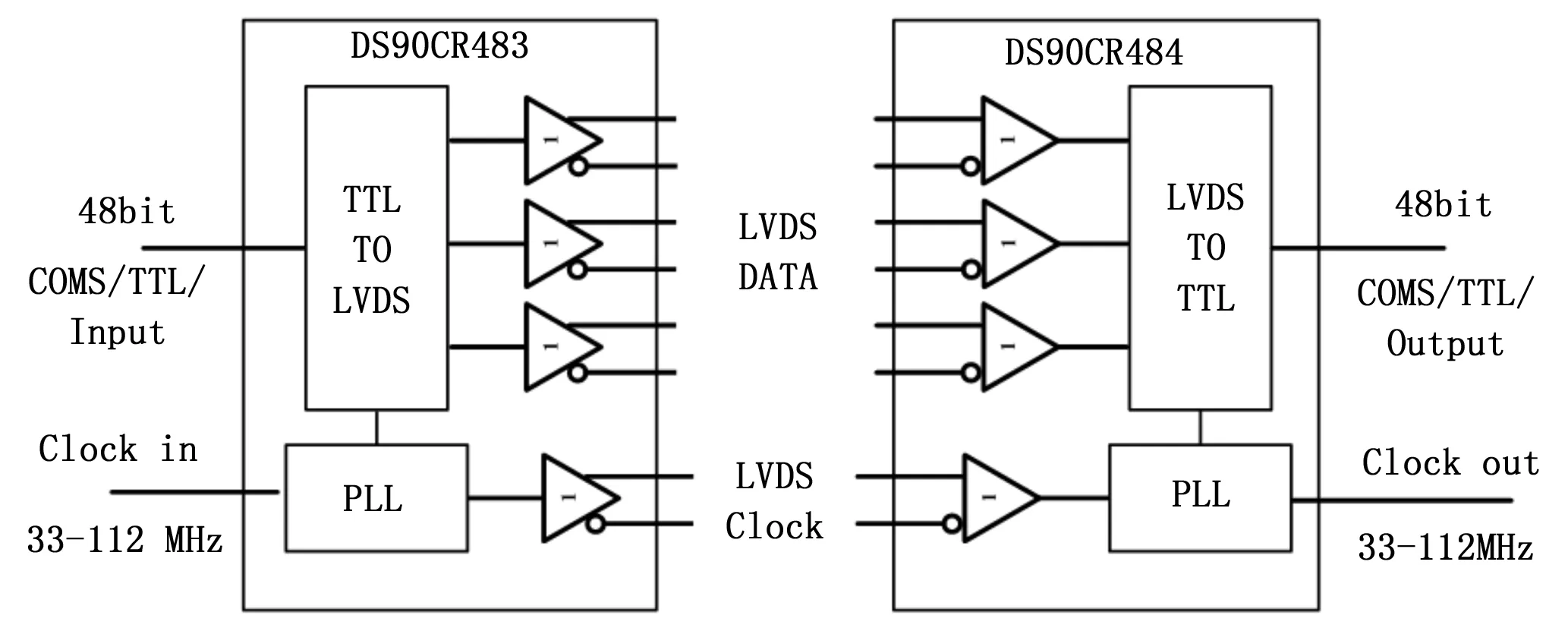

在传输高速LVDS数据信号时,为保证时钟与数据的同步,发送电路选用TI公司生产的LVDS信号驱动芯片 DS90CR483A[3]、接收芯片DS90CR484A。LVDS芯片内部结构如图3所示。驱动芯片 DS90CR483内部的串化器把并行48位TTL或CMOS电平转换为8对幅值只有300~400 mV差分信号。与单端信号传输相比,差分信号抗干扰能力强[5],适宜在电缆中传输;然而,由于电缆中线阻、寄生电容、时钟抖动、电源纹波等因素的影响,信号衰减比较严重。为有效提高传输信号质量本设计利用了驱动芯片的预加重功能,即通过改变芯片外部上拉电阻的阻值,从而增大输入“pre”管脚的电压值来补偿数据传输过程中的动态电流,可以平衡信号在电缆传输的稳定性,保证差分信号在电缆中传输的完整性。

图3 LVDS芯片内部结构

3 逻辑设计

3.1 IIC硬件逻辑设计

由于LVDS接口电路适合高速数据传输,传输控制信息不如IIC总线灵活且IIC总线具有双向传输功能,适合在设备初始化、建立基本连接时进行信息的传输。因此,该处利用IIC总线实现设备间初始化通讯。IIC总线的状态主要包括:主、从机连接状态(这里主机是AD采集设备、从机为IQ数据传输设备)、启动命令数据传输状态、命令数据传输状态、发送响应状态、数据信息发送状态、数据信息发送结束状态。

从机识别主机时序图如图4所示。首先,拉低主机驱动时钟总线,从机检测到clk_lowT大于用户定义的10 ms的连接时间,从机即认为与主机建立了连接;与此同时从机拉低数据总线,如图5所示,主机检测数据总线data_lowT大于用户定义10 ms的连接时间,主机即认为与从机建立了连接。

启动命令数据传输状态:主机驱动时钟线为低电平,同时从机保持数据线为高电平20 μs,即为“启动”命令数据传输状态。

命令数据传输状态:主机检测到从机发送“启动”的命令信号之后,通过时钟总线发出100 kHz的时钟。从机在主机发送时钟沿下,发出命令数据信息,当主机检测从机的命令数据为08h时,主机向从机发送数据信息(主机向从机发送数据信息包括:采样率、数据的最大电平值等)。当主机检测从机的命令数据为04h时,从机可以向主机发送数据信息。如图6所

示,发送响应状态:如图6所示,在发送完1个字节命令数据之后,主机驱动时钟线、从机驱动数据线为低电平保持100 μs时间,此段时间作为发送完一个字节数据的响应。

数据信息发送结束状态:当主、从机接收到00h字节数据信息时,标志着数据信息发送结束,结束数据信息的发送。

3.2 PRBS码检测LVDS接口电路

在传输AD采样数据之前,要对设备的LVDS接口电路进行误码检测以保证数据传输的高可靠性。PRBS码即伪随机序列,伪随机序列具有预先不可确定性和不可重复实现性,但是对于收发数据的双方,PRBS码却是确定的,因此可以利用FPGA内部的线性反馈移位寄存器产生伪随机数序列来检测LVDS接口电路的误码率。

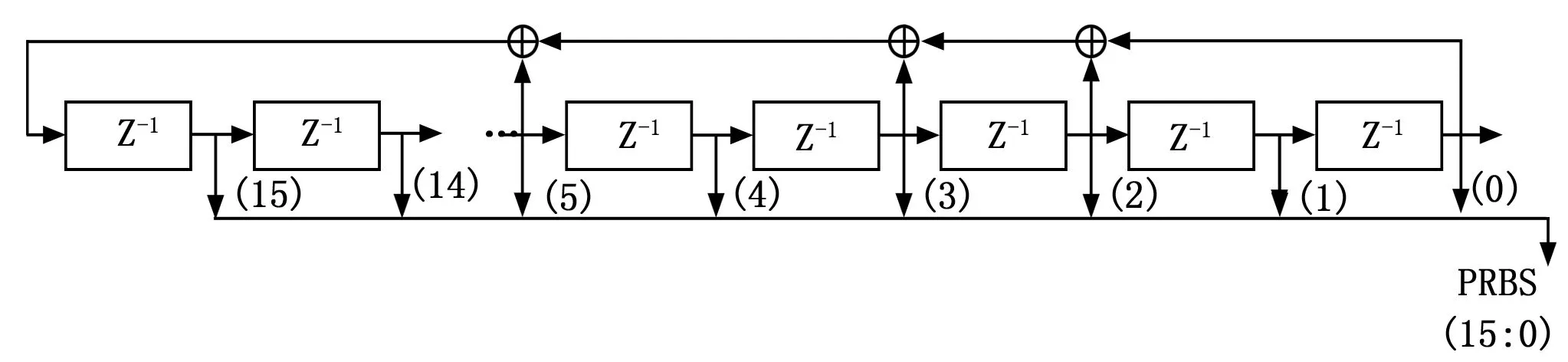

图7是16级线性反馈移位寄存器的电路结构(其数学表达式为p(x)=x16+x5+x3+x2+1)[6]。其中⊕表示门电路中的异或运算。

图7 移位寄存器结构示意图

利用FPGA内部丰富的触发器资源,可以生成16级反馈型的移位寄存器。

如图8所示PRBS码同步检测流程图。主机与从机通过低速的IIC总线启动PRBS码的校验命令之后,从机的同步数据检测模块实时检测主机发送来的数据。在检测到预设的数据时,同步数据检测模块产生的同步信号启动从机生成PRBS码与主机发送来的48位PRBS码逐位进行比较[6],当码型不同时,启动计数器累计误码的个数,上位机定时访问计数器的状态,计算出误码率并显示在上位机界面上。

图8 PRBS码同步检测流程

4 测试结果

误码率与数据速率、预加重电压、环境温度、芯片供电电压噪声等因素密切相关。这里控制环境温度为+25℃,芯片供电电压为恒压低噪声3.3V。利用设计的PRBS码检测电路测试被测设备的LVDS链路通信质量,得出误码率与数据速率、预加重电压、电缆长度关系如表1所示。

表1 误码率与数据速率、预加重电压、电缆长度关系

在环境温度+25 ℃、2米电缆、连续5h工作条件下,本文设计的LVDS接口电路在66 MHz、75 MHz、100 MHz时钟速率下传输PRBS数据的误码率为0,表明接口电路在此条件下通信稳定,数据速率达到3.09~4.68 Gb/s。

5 结语

本文设计的IIC电路满足在100 kHz时钟速率下快速进行双向传输信息的需求,同时自定义的IIC总线协议可以有效控制LVDS接口实现电路误码率检测以及数据信息传输;多通道LVDS接口电路在2米长的电缆、100 MHz时钟速率下,最大数据带宽可达4.68 Gb/s。满足前端AD高速采集的数据传输需求,为更高速AD采样提供宽余传输带宽。

[1] 张 威,苗克坚,陆 寅. 基于LVDS的多路SPI的PCI板卡设计与实现 [J].计算机测量与控制,2012,20(3):790-792.

[2] 任 伟,张彦军,白先民. 基于LVDS 的高速数据传输装置的设计 [J].科学技术与工程,2012,12(29):7759-7763.

[3] 邵 华,刘亚斌,徐志跃. 实时高速LVDS串行数据采集系统的设计[J].计算机测量与控制,2008,16(3):424-426.

[4] 应建华,石枝林,夏晓明. 一种串行时钟芯片的IIC总线接口电路设计[J]. 计算机与数字工程,2007,35(9):180-183.

[5] 孙 轩. 非接触式手机充电平台的设计[D]. 杭州:浙江大学,2010.

[6] 田永和,马小平. 基于FPGA的PRBS伪随机序列的实现与研究[J]. 山西电子技术,2006(1):41-43.

Application Research on High-speed Data Transmission Technology Based on LVDS and IIC bus

Wang Hongliang1, Liu Wei1, He Shaoheng1, Di Lixia2

(1.Science and Technology on Electronic Test & Measurement Laboratory,North University of China,Taiyuan 030051; 2.North Automatic Control Technology Institute, Taiyuan 030006)

LVDS interface has been widely used in high speed data system. In order to realize the intelligent recognition, automatic handshake and the communication test of LVDS high speed data link, FPGA IO circuit is used to design a kind of IIC bus protocol. The IIC bus is used for information transmission between devices; meanwhile, taking advantage of FPGA internal register resources to design PRBS circuit which is used to detect the bit error rate of LVDS interface chip. The experiment shows that the multi - channel LVDS transmission can achieve data stability, low error rate transmission in two meters cable connection, the data transmission rate can reach up to 4.68Gb/s when the clock is 100 MHz.

IIC bus protocol, PRBS code, LVDS signal

2015-12-11;

2015-02-15。

王红亮(1978-),男,副教授,主要从事测试系统集成、目标检测与识别、应用软件开发、超声成像方向的研究。

刘 伟(1988-),男,硕士研究生,主要从事测试计量技术及仪器、电路与系统方向的研究。

何少恒(1989-),男,硕士研究生,主要从事测试计量技术及仪器、电路与系统方向的研究。

1671-4598(2016)07-0181-02

:10.16526/j.cnki.11-4762/tp

TN919 文献标识码:A