体硅CMOS集成电路抗辐射加固设计技术

2016-10-26左玲玲

米 丹,左玲玲

体硅CMOS集成电路抗辐射加固设计技术

米丹,左玲玲

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

首先介绍了空间辐射环境,并对各种辐射效应及其损伤机理进行分析。然后对体硅CMOS集成电路的电路结构、抗辐射加固技术和版图设计抗辐射加固技术进行探索。测试结果表明,采用版图加固抗辐射技术可以使体硅CMOS集成电路的抗辐射性能得到明显提升。

体硅CMOS集成电路;总剂量效应;单粒子效应;电路结构加固;版图设计加固

1 引言

随着航天事业的快速发展,对于集成电路的需求也日益增加。在空间环境中,包含了地磁场所俘获的轻粒子(电子和质子)和一些重的正离子;以及来源于银河系或银河系外天体的宇宙射线,其中包含了一些重的高能粒子;还有太阳耀斑的突然爆发,会产生大量的紫外线和X射线。这些重的高能粒子构成了宇宙空间的辐射环境。这些高能粒子会对应用于空间环境中的集成电路产生各种辐射效应,使集成电路的性能发生退化,导致逻辑功能错误甚至完全永久性损毁。对于应用于空间环境中的集成电路,必须采取抗辐射加固措施才能保证其可靠性,因此对其抗辐射加固设计技术的研究至关重要[1]。

目前,集成电路的主流工艺是体硅CMOS集成电路制造工艺,它具有静态功耗低、电源电压范围宽、输出电压幅度无阈值损失等特点,所以本文主要对体硅CMOS集成电路的抗辐射加固技术进行研究。

2 辐射效应及损伤机理分析

在空间辐射环境中,会产生很多不同的辐射效应。在该领域的集成电路设计中,总剂量辐射效应(Total Ionizing Dose Effect,TID)和单粒子效应(Single EventEffect,SEE)是需要我们重点关注的两种辐射效应。

2.1总剂量辐射效应

样品在受辐射期间内吸收的累积剂量称为总剂量。总剂量辐射效应是累积剂量的电离辐射效应,是一个长期累积导致器件失效的过程。其存在的根本原因在于:集成电路的器件结构中存在SiO2层,电离辐射在SiO2中激发电子-空穴对。电子可以很快移出SiO2层,而空穴则一部分移出SiO2,一部分被SiO2层中的深空穴陷阱俘获成为正的固定空间电荷。在正偏压下,这些固定空间电荷比较多地集中在Si/SiO2界面附近。实际上电子也会被SiO2中的深电子陷阱俘获形成负的空间电荷,只是数量相对少得多,在整个SiO2层中净电荷量仍然表现为正电荷[1]。

在CMOS集成电路抗总剂量性能方面,有3个主要问题需要解决。首先是要抑制由总剂量辐射在CMOS晶体管栅氧化层中引入正电荷造成的阈值电压漂移。辐射引起的CMOS晶体管阈值电压漂移问题可以通过栅氧加固工艺来解决,而且随着工艺关键特征尺寸的缩小,按等比例缩小的原则,栅氧化层的厚度也越来越薄,总剂量辐射引起阈值电压漂移的问题得到了极大的缓解。

其次是要抑制NMOS器件栅和有源区与场区边缘构成的边缘寄生晶体管的源漏间漏电流。总剂量辐射在氧化层中产生的正电荷会导致边缘寄生晶体管的阈值电压降低,降到一定程度会产生漏到源的漏电通路,产生边缘漏电流。随着辐射剂量的增加,边缘寄生晶体管漏电流也迅速上升,当漏电流增加到接近本征晶体管的开态电流时,晶体管会永久开启,导致器件失效。图1为该漏电机制沿沟宽方向的剖面示意图。

图1 总剂量效应引起的源/漏区域漏电沿沟宽方向的剖面示意图

第三是要阻断在场区下方产生的漏电通道,以抑制由其导致的集成电路NMOS器件之间的漏电。场氧化层本来是可以为相邻NMOS管之间提供绝缘隔离的,但随着辐射剂量增大,总剂量效应在场氧化层中产生的正电荷会使场氧化层下的衬底反型,场区的阈值进一步降低,就会产生场区漏电。其漏电机制如图2所示,场氧化层下的漏电通路会延伸到邻近NMOS管的源漏区,这将增大VDD到VSS的静态漏电流。

2.2单粒子效应

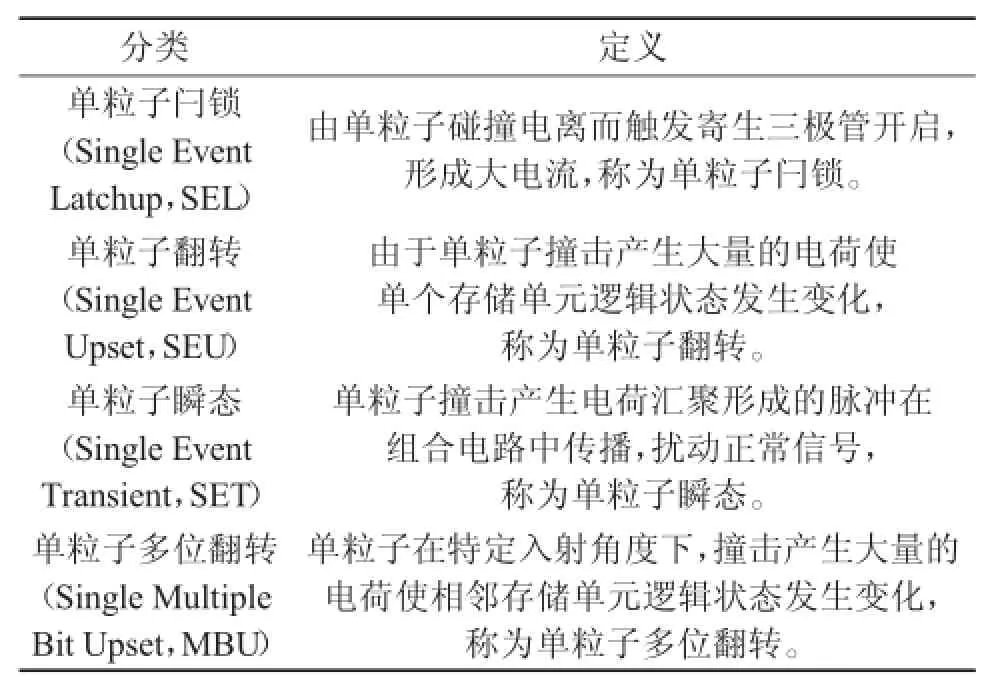

具有一定能量的单个重离子或质子射入集成电路,导致集成电路性能退化或功能失效的现象统称为单粒子效应。集成电路工作在辐射环境时,高能带电粒子穿过器件的敏感区域,由于碰撞电离,会产生大量的电荷。这些电荷被器件收集后,会造成器件逻辑状态的非正常改变或者烧毁。单粒子效应是一种随机离散的效应,它是由很多种效应综合而成的。这些效应都是由单个粒子作用的结果,所以被统称为单粒子效应。通常把单粒子效应引起的随机、非循环、可恢复的错误称之为软错误,而把单粒子效应引起的永久性损伤或烧毁称为硬错误。单粒子效应的分类及定义如表1所示。

图2 总剂量效应引起的场氧下漏电示意图

表1 单粒子效应的分类及定义

随着工艺特征尺寸的减小,电源电压降低、节点电容减小、器件密度不断增加,单粒子效应对器件的影响越来越严重。

3 体硅CMOS集成电路的抗辐射加固技术

对于体硅CMOS集成电路而言,通常通过以下两个方面技术对其进行抗辐射加固:电路结构抗辐射加固技术、版图设计抗辐射加固技术。

3.1电路结构抗辐射加固技术

从电路结构设计的角度考虑提高集成电路的抗单粒子翻转性能,最常用的方式是加入冗余电路。冗余的形式有三模冗余(TMR)、纠错与修正(Error Detection and Correction,EDAC)等[1]。

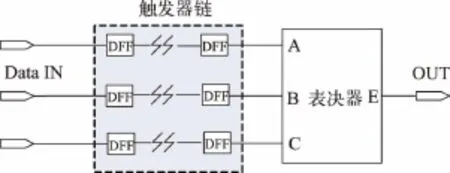

从系统结构进行加固,通常采用三模冗余结构,其理论基础是当集成电路受到单粒子的攻击时,只会使电路网络中的一部分发生错乱,而其他部分是正常的。三模冗余结构的单粒子效应加固是将原来在电路中的1路信号变成3路信号,最后通过1个表决器将最终的信号提供给下一级电路。且只要在被分成的3路信号中有2路或以上信号有效,则输出的信号有效。利用三模冗余加固的触发器链结构如图3所示。

图3 三模冗余结构示意图

三模冗余的表决电路的逻辑表达式为Y=A× B+B×C+C×A,其真值表如表2所示。

表2 三模冗余的表决电路真值表

如果某一路的触发器链信号受到单粒子效应的影响而产生改变,而其他两路的信号还保持正确,那么输出结果还是正确的。三模冗余技术为空间冗余技术。

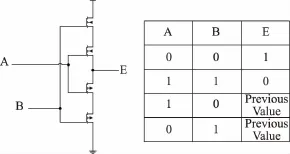

还有一种技术称为时间冗余技术[1]。与空间冗余技术相比,时间冗余技术面积开销低,性价比高。为消除敏感的内部节点,在内部馈线使用双联锁的锁存器。C单元可以阻塞由单粒子翻转诱发的软失效,图4所示为C单元的原理图。

图4 C单元原理图

如果两个输入信号是相同的逻辑值,C单元将输入信号的反相值传递输出。如果两个输入信号是不同的逻辑值,C单元将保持当前状态。C单元保持状态的特性可以阻止发生在内部节点的单粒子翻转,同时具有最小的硬件开销。C单元常用于CMOS的时钟或同步交换信号的同步器。

对于中央处理器(CPU)、数字信号处理器(DSP)、微控制器(MCU)类集成电路,也可采用错误检测与纠正电路来提高其抗单粒子翻转性能[1]。

3.2版图设计抗辐射加固技术

由于CMOS集成电路工作在辐射环境中,受到总剂量效应和单粒子效应的影响,会引起电路的静态漏电流增加、工作时出现大电流及器件烧毁等现象。因此,单纯使用电路结构加固技术已经不能满足芯片的抗辐射设计要求,还需要借助版图设计抗辐射加固技术来解决总剂量效应和单粒子闩锁效应带来的问题。

由于CMOS器件的边缘存在寄生MOS管,在总剂量辐射条件下,会形成漏电通路。为消除辐射条件下形成的器件内漏电通路,在版图设计时考虑采用消除边缘寄生管的方法。由于总剂量效应只会对NMOS管产生影响,形成漏电流,因此在版图设计上只对NMOS管进行设计加固。

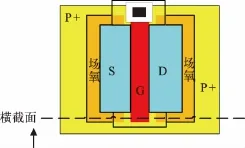

首先,可选择的器件版图结构是环形栅结构。环形栅结构的NMOS如图5所示。图中D端代表器件漏端区域,S端代表器件的源端区域,G为NMOS管的栅极,中间小方块为接触孔,外围为P+注入的保护环。利用该版图结构,消除了条形栅NMOS器件在边缘处的寄生管,使NMOS器件的源漏之间不存在漏电通路。并且,加了P+保护环之后,对于相邻NMOS器件之间由于总剂量效应引起场氧化层下反型导致的漏电,起到吸收作用。虽然通过环形栅结构能够改善NMOS管在总剂量辐射条件下的漏电,但采用环形栅结构,NMOS管的宽长比受到很大限制,用此结构去实现倒比例或小比例的NMOS管几乎是不可能的。

图5 环形栅NMOS管示意图

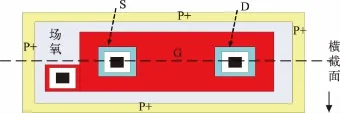

一种抗总剂量辐射效应的大头条形栅NMOS管版图加固结构,可以有效改善总剂量效应的影响。大头条形栅结构如图6所示,该结构利用栅和薄栅氧化层将源端和漏端隔开,消除了边缘寄生管,从而消除了源漏之间的漏电通路。同样,也要利用P+保护环把不同的NMOS器件隔开,防止总剂量辐射条件下场氧反型引起的器件之间的漏电。利用此版图技术,不但可以有效减小总剂量效应对器件的影响,而且NMOS管的宽长比设置更为灵活,可以实现小比例管,并且比环形栅结构更省面积[2]。

图6 大头条形栅NMOS管示意图

在抗辐射版图设计时,会遇到倒比例及小比例NMOS的设计,这时可以采用一种抗总剂量辐射效应的倒比例及小比例NMOS管版图结构,如图7所示。在此结构中,同样也是利用栅和薄的栅氧化层,将NMOS管的源端与漏端隔开,消除了边缘寄生晶体管,从而消除了总剂量条件下器件源漏端之间的漏电。周围也要采用P+保护环将不同NMOS器件隔开,保证在总剂量辐射条件下,不同器件之间不存在漏电[3]。

图7 倒比例及小比例NMOS管示意图

通过环形栅、大头条形栅、倒比例及小比例NMOS管几种特殊版图结构设计加固技术,消除了总剂量条件下器件的漏电通路,从而有效消除了由于总剂量效应引起的漏电。

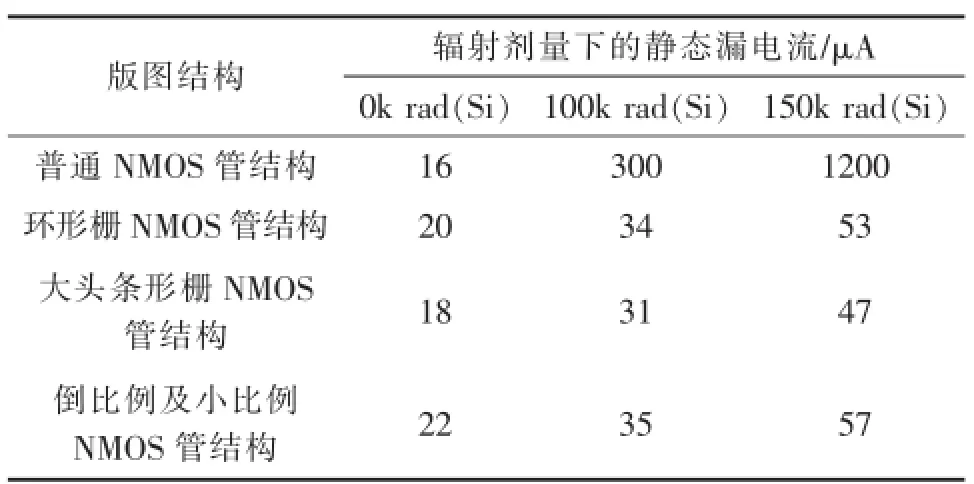

利用以上3种版图加固技术设计的NMOS管连同普通NMOS管分别制成相同的测试电路,在不同辐射剂量条件下,静态漏电流如表3所示。

表3 不同器件版图结构在不同辐射剂量下的静态漏电流

从表3可以看出,利用普通NMOS管版图结构设计的电路,静态漏电流随着辐射剂量的增加大幅度增加。而采用了以上3种抗辐射加固版图结构后,静态漏电流随着辐射剂量增加较小。说明上述3种抗辐射版图设计加固技术对于抗总剂量辐射效应有效。

以上3种抗辐射加固版图结构已经在某款宇航用抗辐射加固发射接收电路中得到运用,经辐射试验,性能指标满足抗辐射要求。

针对单粒子闩锁效应,所能采用的版图技术是:增加N阱中P+有源区到P阱中N+有源区之间的距离,尽可能多地增加阱的接触孔,在NMOS管周围加P+保护环,在PMOS管周围加N+保护环。通过这些版图技术进行加固,可以有效减小单粒子闩锁效应的影响。

4 小结

航天领域要求低成本、快速响应。采用标准商用线工艺,通过设计对集成电路进行抗辐射加固,具有广泛的应用前景,试验结果表明,抗辐射加固版图结构后,静态漏电流随着辐射剂量增加较小,有效提高了抗总剂量辐射的能力。采用这些抗辐射加固技术进行设计,通过标准商用线进行加工的电路,已经通过抗辐射试验的检测,证实其抗辐射性能可以满足航天领域的需求。

[1]韩郑生.抗辐射集成电路概论 [M].北京:清华大学出版社,2011.

[2]罗静,王栋,邹文英,薛忠杰,周昕杰,胡永强.一种抗总剂量辐射效应的大头条形栅NMOS管版图加固结构:中国,201110343583[P].2011-11-03.

[3]罗静,徐睿,邹文英,薛忠杰,周昕杰,胡永强.一种抗总剂量辐射效应的倒比例及小比例NMOS管版图结构:中国,201110344706[P].2011-11-03.

Study of Radiation Hardening Technology of Bulk CMOS Integrated Circuits

MI Dan,ZUO Lingling

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

The paper overviews space radiation environment and various radiation effects and damage mechanisms to explore the radiation hardening technology in circuit structure and layout design.The test result illustrates that the radiation hardening performance of bulk CMOS integrated circuit is greatly improved.

bulk CMOS integrated circuit;total ionizing dose effect;single event effect;radiation hardening of circuit structure;radiation hardening of layout design

TN402

A

1681-1070(2016)09-0040-04

米丹(1976—),女,辽宁绥中人,毕业于西安电子科技大学微电子技术专业,东南大学工程硕士,现就职于中国电子科技集团公司第58研究所,从事抗辐射集成电路设计研究工作。

2016-5-20