基于FPGA的多串口通信设计与实现

2016-10-22殷安龙张持健陈林许矛盾

殷安龙,张持健,陈林,许矛盾

(安徽师范大学安徽芜湖241000)

基于FPGA的多串口通信设计与实现

殷安龙,张持健,陈林,许矛盾

(安徽师范大学安徽芜湖241000)

为了实现PC机同时与多个外设终端实时进行通信显示的要求,从而达到PC机对所属串口设备的实时监测与控制,本文采用基于FPGA和NiOSⅡ软核的方法开发出一套多串口通信系统。文章通过以CycloneⅡ系列的EP2C8Q208C8N为MCU设计电路和Verilog语言描述生成UART IP软核实现多串口数据传输至处理器的设计方案,结合ModelSim仿真以及串口调试助手模拟PC机与串口设备之间通信的试验。结果表明,该系统能实现PC机与所属串口设备之间的通信,通信准确率高,速度快,具有可行性。

多串口通信;FPGA;软核

Altera公司自1984年以来,发明了第一块FPGA(现场可编程门阵列)芯片,随着半导体技术水平的不断提高,,在单位面积上硅片可以集成更多的晶体管,这使得FPGA价格继续下降,性能越来越强大。Altera公司与2000提出的SOPC技术以及SOPC Builder开发软件,其技术实现了在FPGA上嵌入处理器,利用SOPC来构建NiosII软核处理器,具有控制能力强、灵活裁剪等独特优势。

由于现代工业企业中在线监测的日益增长,需要PC机与更多设备进行通信,串口通信具有实现简单,使用灵活,数据传输准确等优点,在工业监控和实时监控系统中得到了广泛应用。由于监测设备的增加,PC机原有的串口不能再满足通信的需求,传统的设计方法是使用硬件扩展八个串口,但是额外增加了硬件设计成本和实际编程的难度。然而FPGA的UART IP可灵活定制的优点使得基于FPGA的设计方法无需额外的硬件串口扩展,减少了硬件开发调试的难度,同时满足串行传输的要求。文中将选择信号处理和控制能力强的CycloneⅡ系列FPGA来实现PC机与设备之间的多串口通信。

1 系统总体设计

文中选择Altera公司的信号处理和控制能力强的CycloneⅡ系列EP2C8Q208C8N FPGA芯片来实现PC机和设备之间的串行通信,串行端口处理模块使用对UART进行RS232电平转换的MAX3232芯片,再经过9针D型串行接口与设备以串行数据格式通信。

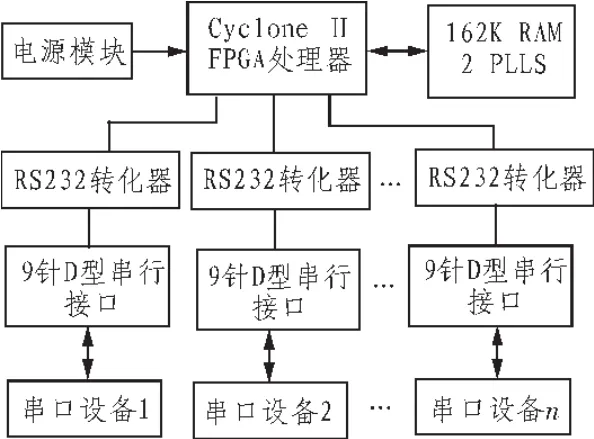

图1 系统总体框图

文中提出利用FPGA UART IP实现多串口数据传输至处理器的设计方案。方案中,8个UART IP实现8个串口数据的接收,传输波特率可调,8路并行数据合并为1路数据,串行传输至处理器。系统可分为硬件设计和软件设计两部分:硬件设计部分包括处理器模块、串口模块;软件设计部分包括系统启动代码实现、多串口通信设计。

2 系统硬件电路设计

电平转换电路中串口的数据在接入至FPGA的引脚之前,需要进行电平转换。利用4片MAX232芯片即可实现8路UART的电平转换,其中2路的电平转换电路图如图2所示,其它6路与此类似,不再赘述。

图2 电平转换电路

3Nios II UART IP软核设计

3.1UART串口通信模块

如图3所示UART串口通信由以下4个模块组成:发送模块(uart_tx)、接收模块(uart_rx)、接收波特率发生器(speed_rx)和发送波特率发生器(speed_tx),其中,发送波特率发生器主要用来产生发送模块发送数据时所需的波特率时钟,接收波特率发生器主要用来产生接收模块接收数据时的波特率时钟,发送模块主要负责在指定波特率的速率下将待发送字节发送出去,接收模块则主要负责接收来自其他设备发送过来的串口数据。

uart_top模块即串口收发顶层模块实现了各个模块间的信号连接功能,通过该顶层模块的连接,实现了将串口接收到的数据再发送出去的功能,即我们测试串口通信最常用的一种方式—回环测试。

图3 串口通信软核RTL视图

3.2UART串口通信ModelSim仿真

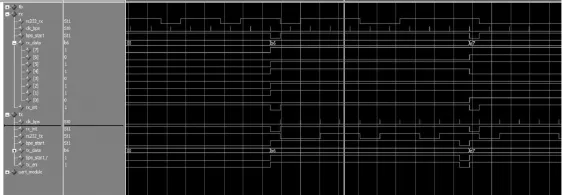

串口接收模块在检测到数据起始位时,rs_int置1,该信号作为启动串口接收波特率发送器的控制信号,然后在每个波特率时钟clk_bps上升沿到来时读取串口接收端口(rs232_rx)上的数据。一帧(字节)数据接收完成后,接收中断信号拉低,停止波特率发生器工作,接收完成,等待下一次的数据到来,由图4仿真波形图可以看出接收来自串口的三帧数据分别为00、b6、e7。

3.3串口数据传输测试

接收中断信号的下降沿也作为串口发送模块的发送使能信号(tx_en置1),使能串口发送波特率发生器,串口发送模块则在波特率时钟的上升沿到来时依次将接收模块接收到的数据的每一位依次发送出去,接收模块通过串口接收数据。如图5所示,测试时将串口调试助手的波特率设定为9600 bps,先以十六进制发送和接收字节10、AA、AB、68、69、hi六帧字节,而后发送和接收字符串abcdef,发送和接收数据均正确,验证了串口数据正常传输。

图4 串口通信仿真波形

图5 串口调试助手发送接收数据图

4 结束语

文章围绕着基于FPGA的多串口通信设计与实现的数据传输展开研究,根据通信要求,在系统数字平台FPGA上,完成了串口数据传输的硬件电路设计、UART IP软核设计以及串口通信数据传输的仿真与测试等的实现。

文中提出利用FPGA UART IP实现多串口数据传输至处理器的设计方案。在此方案中,8个UART IP实现8个串口数据的接收,传输波特率可调,8路并行数据合并为1路数据,串行传输至处理器。文中一改传统的串口扩展方案,并没有使用具有并转串功能的TL16C754芯片将8路并行的UART发送至处理器,解决多串口通信中硬件电路复杂、成本高、调试困难等问题,同时从ModelSim仿真波形图和串口调试助手测试可以看出,基于FPGA的UART IP串口通信设计正确快速地实现了8个串口数据的传输。

[1]SOC FPGA Product Overview Advance Information Brief[M].Altera Corporation,2012.

[2]张明.基于FPGA的UART控制器的多模块设计与实现[J].中国科技信息,2006(16):138-140.

[3]刘韬,楼兴华.FPGA数字电子系统设计与幵发实例导航[M].北京:人民邮电出版社,2005.

[4]Nios II ProcessorReference Handbook[M].Altera Corporation,2011.

[5]顾仁涛,王强.FPGA设计开发与工程实现[M].北京:北京邮电大学出版社,2013.

[6]胡志雄,华泽玺.基于Nios II的多串口转发通信处理机设计[J].物联网技术,2011(6):44-46.

[7]向乐乐,卢艳娥.基于Nios II的多串口数据通信的实现[J].电子设计工程,2011,19(2):24-26.

[8]QuartusII 9.1 SP1 HandbookVolume 5 UART Core[M].Altera Corporation,2009.

Design and implementation of multi-serial communication based on FPGA

YIN An-long,ZHANG Chi-jian,CHEN Lin,XU Mao-dun

(Anhui Normal University,Wuhu 241000,China)

In order to achieve the computer simultaneously with multiple peripheral terminal display real-time communication requirements,so as to achieve the real-time monitoring and control between the computerand its serial equipments.Based on FPGA and NiOSⅡsoft core,this paper developed a serial communication system.The article using the CycloneⅡseries' EP2C8Q208C8N for the MCU circuit's design and Verilog language to describe the generation UART IP soft-core to achieve theMulti-serialdatatransmissiondesign.CombinedwithModelSimsoftware'ssimulationandserialdebugging assistantsimulation communication between computer and serial devices.The results show that the system can achieve communication between computer and its serial equipments,the communication is High accuracy and speedy,and the system has feasibility.

serial communication;FPGA;soft core

TN911.72

A

1674-6236(2016)17-0045-03

2015-09-01稿件编号:201509004

殷安龙(1990—),男,安徽芜湖人,硕士研究生。研究方向:嵌入式开发与智能控制。