一种宽输入电压范围高PSRR线性稳压器

2016-10-22辛晓宁张雷

辛晓宁,张雷

(沈阳工业大学辽宁沈阳110870)

一种宽输入电压范围高PSRR线性稳压器

辛晓宁,张雷

(沈阳工业大学辽宁沈阳110870)

基于HHNEC BCD工艺,设计了一种输入电压范围为5.4~40V,输出电压为5V的线性稳压器。为了获得高电源电压抑制比,电路采用二级稳压结构,基于耗尽型MOS管的预稳压器将输入电压稳压到5.2V,再使用一种输出端接2.2 μF电容的低压差稳压器(二次稳压器)得到最终输出电压5V。Hspice仿真表明,PSRR在100kHz以下时优于-90 dB,在1 MHz以下时优于-70 dB。

二级稳压;宽输入范围;高电源电压抑制比

线性稳压器是一种应用广泛的芯片,其作用是为系统提供稳定的工作电源。许多应用领域的输入电压范围很宽,例如,工业自动化领域的两线制仪表和各种现场总线仪表的典型供电电压范围为9~32V,且系统需要利用电源线传输信号,要求系统内部的高精度电路不受供电电源和高频信号影响。在此类系统中,稳压器的输出电流一般只需要几十毫安,最重要的性能指标是电源电压抑制比(PSRR)。典型低压差稳压器(LDO)的输入电压范围较窄,高频区的PSRR比较低[1-4]。目前,只有少数国外厂家[5-6]能够提供宽输入范围、高PSRR的产品。目前,国内BCD工艺已可提供多种高耐压器件,可以解决耐高压问题,文中基于HHNEC的BCD工艺提出了一种新的设计方案。

在典型的LDO结构中,要提高PSRR,需要提高误差放大器的开环增益,但这将影响系统的稳定性。为保证稳定性,需要采用频率补偿措施,而任何频率补偿都不可避免地会降低高频环路增益,因此普通LDO结构在高频区的PSRR很难提高。此外,由于基准电压直接工作在输入电压下,本身受电源电压影响,且其变化量将被环路放大,也是导致PSRR难以提高的因素。对于不需要大的输出电流的应用,可以考虑二次稳压技术,即先使用一个不需要外部电容的内部稳压器先对输入电压进行初步稳压,再使用LDO电路进行二次稳压。这种技术的关键是保证一次稳压器在无输出电容时的稳定性。采用两级稳压的另一个优点是可以将芯片中的高压区集中在一个小的范围内,有利于节省版图面积并提高可靠性。

1 电路设计

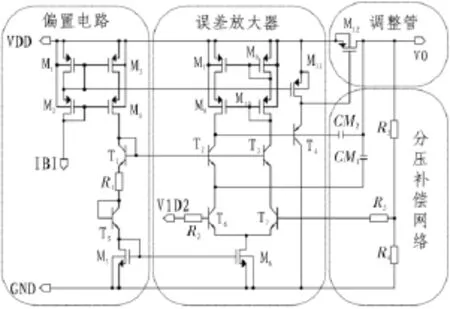

图1是包括基准电压电路的预稳压器完整电路,它主要由降压电路、差分放大器、偏置电路和带隙基准电路四部分组成。降压电路由M1采用M2和R1构成,这里M1和M2都是高耐压耗尽型NMOS管。M1是电压调整管,其尺寸要满足输出电流的需要。M2与R1构成恒流源,限制了从输入端流入的电流。

芯片上电时,由于M1管为耗尽型,电流可以流过M1管为后面电路提供一个启动电压。为避免产生较大的过冲电压,在调整管栅极放置了电容C1,可将过冲电压限制在10V以下。图1中所有器件的耐压能力都在10V以上,故保证电路安全。

在电路正常工作后偏置电路为差分放大器和带隙基准提供偏置电流。假设所有同型双极晶体管特性相同,偏置电路中T7、T8、R8组成了恒流源电路,电流大小为:

图1 预稳压及基准电路

T9、T10、T11、R6、R7组成了比例电流镜,T11集电极电流I11与IR8关系为:

T12、T13、T14组成了电流镜,T12、T13集电极电流I12、I13与I11关系为:

将公式(1)、(2)代入(3)得(4)

T13是基本电流它经过T18镜像给T4,为差分放大器提供电流,而T12、T15为通过M3、M4在IBI端为二次稳压器提供偏置电流。

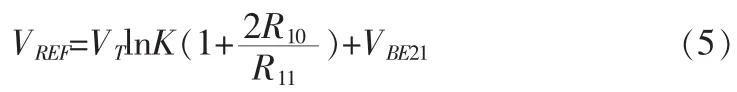

图2中带隙基准电路为系统提供参考电压,带隙输出电压为[7]:

图书馆纸质图书借阅信息反映,该校大学生阅读的经典著作很少(马列主义类除外),经济类图书排名前10名的图书没有一本是经典著作,阅读的主要是怪诞行为学、牛奶可乐经济学、魔鬼经济学等大众普通读物。这种阅读偏好说明学生不重视学科专业基础理论的学习,读书旨趣偏离了大学教育的方向,与大学的思想性、理论性、高层次性、前瞻性、引领性等神圣身份不相符,也即学风存在问题。

图2中带隙基准与差分放大器将决定输出电压VO1,其电压关系式为:

式(6)中看出调整R2、R3电阻比例可调整输出电压VO1为5.2V。由于差分放大器是单级电压放大器,T1、M1可以看作电压跟随器无电压放大作用,因此预稳压器不需要进行频率补偿,所以不需接外部电容和补偿电容。

图2 二次稳压电路

1.2二次稳压器电路设计

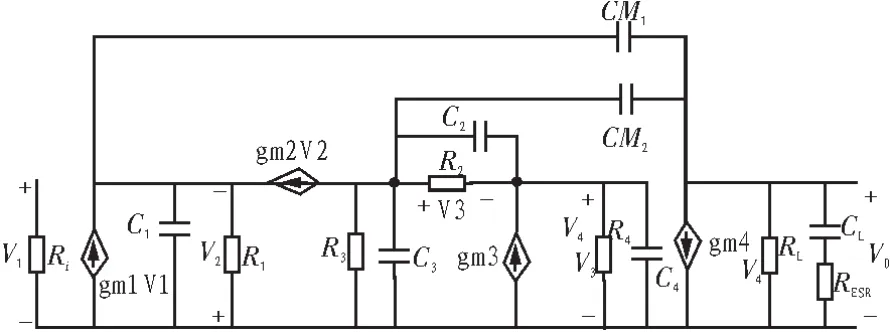

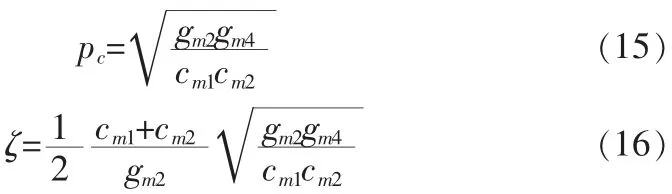

由于预稳压器的开环增益较低,要提高PSRR需要二次稳压,二次稳压器的关键是要在具有高开环增益且保证在较大的输出电容变化时的稳定性。图2是二次稳压详细电路,它采用LDO结构。误差放大器采用共源共栅结构,其优点是提高环路增益和电源电压抑制比。在图2中误差放大器与调整管M12构成了三级电压放大器与一级射级跟随器,小信号等效模型在图3中。图2中的T6、T7,T2,T4与M12分别对应图3里面的gm1V1,gm2V2,gm3V3,gm4V4。在图2、图3中CM1、CM2是补偿电容,用于对多级放大器进行补偿。我们在利用图3求解环路增益时做如下假设:

因此小信号模型环路增益为:

直流环路增益为:

图3 二次稳压小信号模型

电路的主导极点为:

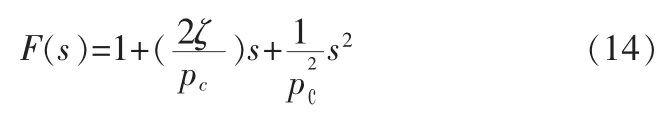

在式(11)中对分母二次项因式从新整理得:

为确保环路稳定,在单位增益频率内应只有一个极点,因此pc应该放置在增益带宽积外(一般取2GBW≦pc)。

式(17)是约束条件,当器件满足此条件时电路可以稳定工作。解式(11)中分子二次项因式得:

观察式(18)、(19)可以发现这两个零点都在非常高的频率下,它们对电路的极点影响很小,因此可以忽略。

2 仿真结果与性能对比

下面测试结果无特殊说明时,默认测试条件为:CL=2.2 μF,IL=10 mA,Vi=7V,T=25℃。图4是在不同负载电流PSRR曲线,在1 MHz以内拥有良好的电源电压抑制比,从图中可以看出,在0~10kHz范围内,PSRR优于-120 dB,在10~100kHz范围内优于-90 dB,在100kHz~1 MHz范围内优于-70 dB。

图4 电源电压抑制比

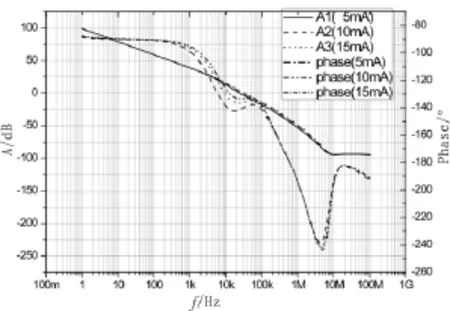

图5 环路增益与相位稳定裕度

图5展示了不同负载电流下的环路增益与相位稳定裕度,最坏相位裕度是40°。表1给出了与一些典型电路的比较结果,从中可见,本文给出的方案在PSRR与输入电压范围都有明显优势。仿真结果表明,二次稳压技术对提高PSRR有显著效果,该方法的主要问题是预稳压器的调整管会占用较大芯片面积。

表1 仿真结果对比

3 结束语

基于国内BCD工艺,利用二次稳压结构,设计了输入电压范围在5.4~40V,输出电压为5V,输出电路为30 mA的稳压器,该电路的突出优点是在很宽的频率范围内具有很高的电源电压抑制比。

[1]LEUNG K N,MOK P K T.A capacitor-free CMOS low dropout regulator with damping factor control frequency compensation[J].IEEE J Sol Sta Circ,2003,38(11):1691-1702.

[2]CHEN C Z,WING H K.Output Capacitor Free Adaptively Biased Low-Dropout Regulator for System on Chips[J].IEEE Trans Elec Dev,may 2010,57(10):1017-1028.

[3]Or P Y,Leung K N.An output-capacitor less low-dropout regulator with direct voltage-spike detection[J].IEEE J Sol Sta Circ,2010,45(8):458-466.

[4]HUANG W J,LIU S I.Capacitor-free low dropout regulators using nested Miller compensation with active resistor and 1-bit programmable capacitor array[J].IET Circuits Devices Syst,2008,3(10):306-316.

[5]ADI公司.ADP7142手册[EB/OL].(2014-9)[2015-08-03].www.analog.com.

[6]美信半导体器件公司.MMAX15006手册[EB/OL].(2015).[2015-08-03].www.maximintegated.com.

[7]毕查德拉扎维.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2008.

A wide input voltage range and high PSRR linear regulator

XIN Xiao-ning,ZHANG Lei

(Shenyang University of Technology,Shenyang 110870,China)

Based on HHNEC BCD process,liner voltage regulator has been designed when input range is 5.4~40V output voltage is 5V.In order to achieve high PSRR,two stages structure is used.Input voltage is pre-regulated to 5.2V based on high voltage tolerance depletion MOSFETs,LDO(secondary voltage regulator)of output have 2.2 μF capacitor once again is used voltage regulator which finally output voltage to 5V.the circuit is simulated with Hspice,PSRR is-90 dB under 100kHz and-70 dB under 1 MHz.

two stages regulator voltage;wide input range;high PSRR

TN4

A

1674-6236(2016)17-0185-03

2015-09-11稿件编号:201509084

辛晓宁(1965—),男,辽宁沈阳人,教授。研究方向:大规模集成电路和SOC低功耗设计法、现场总线技术。