基于NIOS II软核的数字频率计实现

2016-10-17沈珊瑚芦浩宇

吴 军, 沈珊瑚, 芦浩宇

(杭州师范大学杭州国际服务工程学院,浙江 杭州 311121)

基于NIOS II软核的数字频率计实现

吴军, 沈珊瑚, 芦浩宇

(杭州师范大学杭州国际服务工程学院,浙江 杭州 311121)

本文利用Cyclone IV E 系列FPGA芯片内部资源及NIOS II软核设计完成一款等精度数字频率计,其测频功能利用Verilog语言实现,对测频模块得到的各项数据利用C语言编程实现,并通过实时运算将数据传送给液晶模块.本设计具有测量带宽大、实现面积小、数据传输可靠稳定等特点,并且由于各部分相互独立,两两之间不相互依赖,系统灵活高效.

NIOS II软核,FPGA,SOPC,数字频率计

数字频率计是一种将被测信号的频率用十进制数字显示的数字测量仪器,数字频率计主要用于测量正弦信号、方波信号、脉冲信号以及其它在单位时间内变化的物理量等的频率或周期,也可以用于对这些被测信号的占空比进行测量,或者对其进行计数,以达到计时的目的[1-2].

早期的频率计采用的是分立式元件,其设计的周期时间长,而且出来的成品功耗高、体积大、稳定性也差,在精度上也得不到保证.中期的频率计功耗开始降低,体积也大大减小,稳定性也得到了提高,最重要的是在精度上有了较大的改善,但是由于数字频率计在电路设计上仍是复杂困难的,所以同样导致设计周期时间长、测量频率的范围有限和灵活性差等问题.在2004年,Altera公司推出了基于FPGA器件之上的NIOS处理器,它是一款由用户自定义的32位RISC嵌入式处理器,能够自由分配RAM和ROM的大小,用户通过SOPC Builder[3-5]工具选择最合适的CPU、外设接口和存储接口而不必改动电路板的设计,可以针对某一特定的功能而进行优化改造,在真正意思上实现了集成电路硬件的软设计,大大节省了设计的成本和周期,同时也提高了电路设计的灵活性和可移植性,为现代工业的生产带来了极大的方便[6-8].

本设计是一款基于NIOS II处理器的数字频率计.其测量要求是对于2.5~5V的脉冲信号:所测量的频率范围在1~400MHz,其误差不超过10-4;所测量的占空比范围在10%~90%(2MHz之内),其误差不超过10-1.

本设计的创新特点如下:1) 采用32位的计数器,大大增加了测量范围,其理论测量范围可达4GHz;2) 采用NIOS II软核计算和处理计数器的各项数据,在很大程度上节省了芯片内部资源;3) 采用NIOS II软核控制液晶,增加了数据传输的可靠性与稳定性.

1 原理

1.1频率计整体方案原理

图1 计数法测频原理Fig. 1 Frequency measurement by counting method

本设计选择采用计数法来实现频率计的设计.计数法测频就是在闸门单位时间内对频率信号的周期个数进行计数.其原理可用图1来说明:

假设a为脉冲信号,其周期为TA;b为闸门信号,其闸门时间为T;c表示计数的结果,当闸门信号由低电平翻转为高电平时开始对a进行计数,若计数的结果为N;那么理论上它们三者之间存在着如下关系:

N=T/TA

(1)

但实际上由于闸门时间T和脉冲信号的周期时间TA并不存在关系,也即无法确定闸门时间T就是脉冲信号周期TA的整数倍,所以理论上算出来的计数结果N和实际中的计数结果有计数出入.

假设△t1是闸门信号开启时间到首个计数脉冲上升沿的时间间隔,△t2是闸门信号关闭时间到最后一个脉冲信号上升沿的时间间隔,那么在闸门信号的有效计数时间内,存在如下关系:

T=N*TA+ △t1-△t2=(N+△N)*TA

(2)

其中

△N=(△t1-△t2)/TA

(3)

从式(2)可以看出,在闸门有效时间内得到的计数结果理论值和实际值存在着偏差,偏差值△N的存在是由于系统的工作时间、闸门信号的开启时间与被测信号的上升沿之间并不一定同步而导致的,被测信号上升沿出现在闸门时间内的不确定性决定了△N出现的必然性.当闸门时间T接近或等于脉冲周期TA的整数倍时,△N的绝对值取到最大值,即△N的取值只能在±1之间.所以脉冲计数的最大量化误差(绝对误差)为:

△N=±1

(4)

最大相对误差为:

△N/N=±1/N

(5)

以上就是对脉冲计数法测频的原理分析和误差分析,但在实际的项目实践中,往往是根据被测信号频率的大小,直接划分成为直接测频法和间接测频法(周期测频法),以及定制闸门时间的大小,以减小量化误差,使误差在允许的范围之内.

在实际的应用中,当被测信号的频率较高时,采用直接测频法,当被测信号的频率较低时,采用间接测频法,由于它的精度仅取决于基准时钟的精确度和计数的误差(通常计数的误差只在正负1之内,对于计数个数为10万以上的频率来说,在误差允许的范围之内),所以用计数法测频无论在高频段还是在低频段都可以达到较高的精确度.

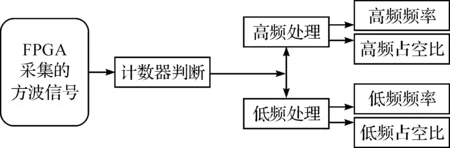

如图2所示,先把待测信号接入放大整形电路中处理,将其转换成固定幅度的方波信号,但保持频率和占空比不变;然后由FPGA芯片进行采集,在FPGA内部的计数器模块将对其进行判断并执行相应的处理,最后将数据传输给NIOS II嵌入式处理器,由该处理器对这些数据进行运算和处理,并控制液晶显示最后得出的频率测量结果.

1.2频率测量模块的原理

频率测量模块的主要组成部分是计数器,首先对经前端处理后的信号进行预判,若判断的结果为高频段,则进入直接测频法模块进行测频;若判断的结果为低频段,则进入间接测频法模块进行测频.其中直接测频模块中需要用到的闸门信号由基准时钟经分频模块后产生,对测频输出的数据不做处理,全部传输给NIOS II软核进行计算和处理.该模块原理可以用图3来说明.

图2 基于FPGA方案频率计的系统框图Fig. 2 System framework for cymometer based on FPGA

图3 频率测量模块的原理图Fig. 3 Illustration for frequency measurement module

1.3液晶显示模块的原理

图4 液晶显示模块的原理图Fig. 4 Illustration for LCD display module

液晶显示模块用于显示测量的频率结果,它的控制将由NIOS II处理器来完成,对于频率测量模块的各项数据能够在经过计算后正确地显示在液晶上.液晶显示模块的原理可以用图4来说明.

2 频率计设计的实现

2.1频率测量模块的实现

频率测量模块主要采用32位的计数器来实现,系统基准时钟设为200MHz.依据高低频段不同的方式处理,其理论可测量的频率范围为1~4GHz,且其精度在10-4之内,满足频率测量的要求;其理论可测量占空比的频率范围在1~2MHz,理论可测量的占空比大小在10%~90%,且其精度在10-2之内,满足占空比的测量要求.利用Verilog HDL语言编写了以下几个模块来共同实现频率的测量功能:分频计数模块、周期计数模块、占空比计数模块和频段判断和处理模块.下面对这4个子模块进行详细的介绍.

2.1.1分频计数模块

分频计数模块的核心原理是由一个17位的计数器构成,主要用于对系统时钟信号进行分频,进而产生需要的闸门信号,本设计中要用到的闸门时间为1s,故可对200MHz的系统时钟进行200M分频(分频系数越大,分频后的信号误差越小),分频后的周期正好为1s,符合要求.

该分频计数模块的主要特点在于不是在最后一个计数结果抬高电平,而是在中间就开始抬高电平,这样分频后的信号,其占空比可以仍为50%;而且分频的系数是由用户自己定义,极大的方便了对该模块的调用,下面对该模块进行仿真说明.

图5 分频模块仿真图Fig. 5 Simulation for frequency division module

设置的系统频率信号周期为5ns(也是下面几个模块工作的系统时钟信号);由图5可知,分频系数为10,根据理论计算,分频后的频率信号周期为:5ns*10=50ns;

由图5红色方框内的信息可知,仿真得到的信号周期为:340ns-290ns=50ns;与前面的计算结果一致,所以仿真结果正确;同时可以发现,分频后的信号在高电平和低电平计数个数是一样的,即占空比为50%,符合设计初衷.由于高频模块能够正常工作,而低频模块的误差只会更小,所以验证了高频,也就相当于验证了低频.

2.1.2周期计数模块

周期计数模块的核心原理是一个32位的计数器,该模块的主要功能是对待测频率信号进行一个周期内的计数,并输出计数结果;该模块的主要特点在于不是对信号的半个周期进行计数,而是对整个周期进行计数,到下一个周期时又清空计数结果,重新计数,这样计数的好处在于当被测频率信号占空比不为50%时仍能给出正确的频率计数结果.下面将结合时序图对该模块进行仿真说明.

图6 周期计数模块仿真图Fig. 6 Simulation for cycle count module

设置待测信号的周期为55ns;根据理论计算,计数结果应该为:55ns/5ns=11;由图6红色方框内的信息可知,仿真结果为:(687.49ns-632.49ns)/5ns=11;仿真得到的结果为11,与理论计算值一致,说明该模块正常工作.因为被测信号周期越长,测量的结果就会越准确.因此只要在高频的信号下测量,计数结果是不是正常,就能知道整个模块能不能正常工作.

2.1.3占空比计数模块

占空比计数模块的核心也是一个32位的计数器,与前一个模块不同的是,该模块只在被测信号翻转为高电平时开始计数,这样做的目的在于可以基于前一个模块的计数结果计算出该信号的占空比.假设在周期计数模块对被测信号的计数结果为full,在占空比模块对被测信号的计数结果为dH,则占空比的计算公式为:

duty=(t(dH)/t(full))*100%

(6)

该模块的主要特点是只针对被测信号的高电平持续时间内进行计数,并对下一个高电平到来之前情况计数结果,下面将根据图来对占空比模块进行仿真说明.

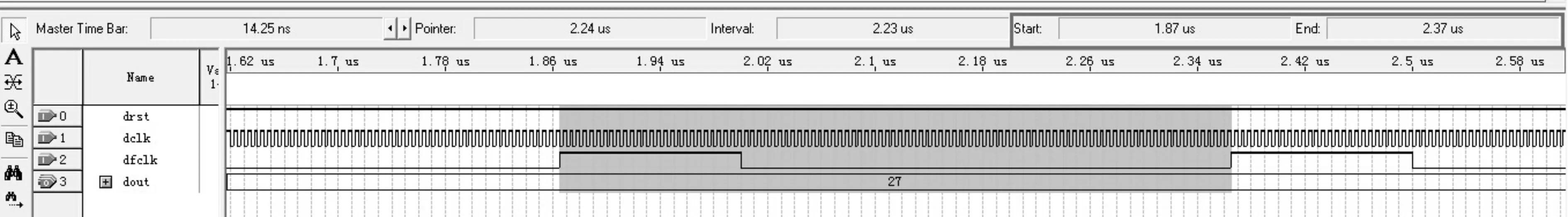

图7 占空比计数模块仿真图Fig. 7 Simulation for duty cycle count module

被测信号的周期设为500ns,其占空比为27%;根据理论计算,计数结果为:(500ns*27%)/5ns=27;

由图7可知,计数结果为:((2.37us-1.87us) *27%/5ns)=27;即仿真结果为27,与理论计算结果相同,说明该模块工作正常.由于在实际过程中,占空比计数模块所测量的频率越高,误差越大,所以只要验证误差较小的高频信号,若正常,说明此频率下的其它信号也能正常工作.

2.1.4频段判断和处理模块

频率判断和处理模块为频率测量模块的核心重点,相当于一个小型的顶层文件,它综合了前面的分频、周期和占空比计数3个模块,通过例化这3个模块,使其在这一个模块中同时工作;该模块的主要工作是判断出被测信号的频率段,并根据判断的结果将待测信号送入不同的模块中进行计数测量;当判断结果为高频时,在闸门时间内采用直接测频法对该被测信号进行计数,若计数结果为cH,则该被测信号的频率计算公式为:

f=cH/(1Hz)=cH

(7)

若判断该信号为低频信号,则把该被测信号当作闸门信号,采用间接测频法对其计数,如果计数结果为cL,则该被测信号的频率计算公式为:

f=(1/5ns)/cL=200000000/cL

(8)

因为本设计要求的精度为10-4,所以判断一个信号为高频还是低频的中间频率为:

1Hz/10-4=10KHz;

图8 频段判断和处理仿真图Fig. 8 Simulation for frequency range judgement

被测信号的周期设为1us,占空比设为14%,依据理论计算,计数结果为:

icnt=1us/5ns=200;

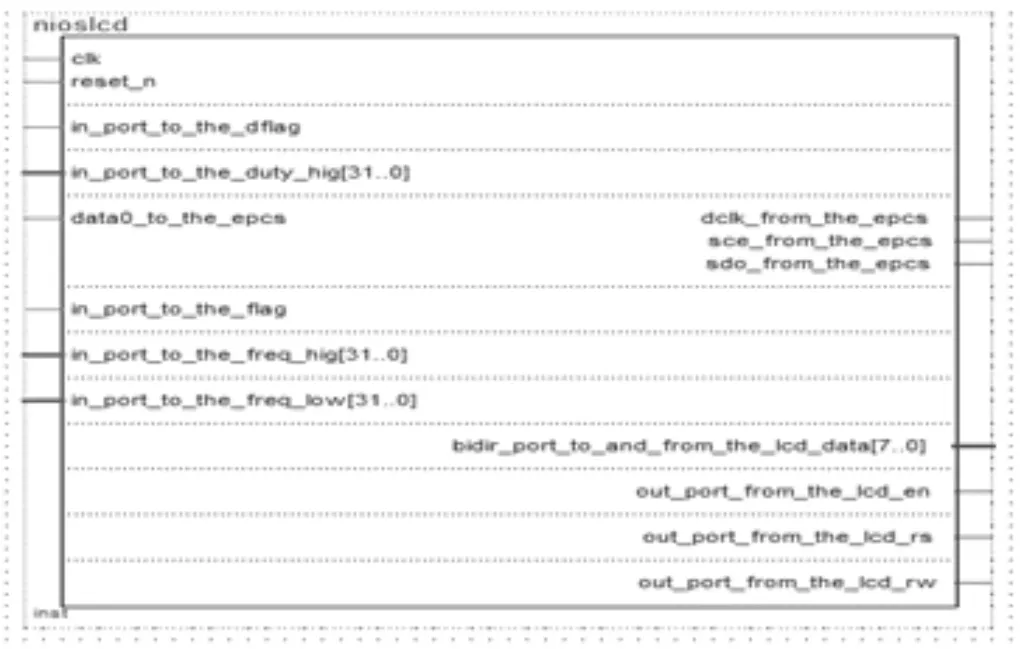

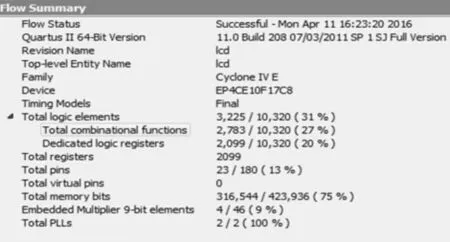

即100 高频段计数结果: cH=1s/1us=1000000; 占空比计数结果: dH=1us*14%/5ns=28; 由图8可知,flag=1,dflag=0,cH=1000000,dH=28;这与理论计算的结果相同,所以频段判断和处理模块工作正常.经过该模块后的数据,其频率的具体计算都将传输给NIOS II处理器,通过在顶层文件用原理图的方式相连接,可以省去大量的引脚. 2.2液晶显示模块的实现 图9 液晶的初始化程序图Fig. 9 Initialization program for LCD 液晶显示模块主要在NIOS IDE中用C语言编写程序对其控制,根据液晶的时序来编写程序,发送指令控制显示. 在给液晶传达指令时,需要注意液晶执行各个命令的时间,在本设计中所用的液晶清屏指令和地址归为指令执行时间为1.6 ms,其它指令均为72us.所以在程序设计中对液晶初始化的步骤如图9所示,等待时间大于指令执行时间. 在本设计中要求频率显示要根据结果自动切换单位,如当被测频率信号的频率测量结果大于1000Hz时,则后面的单位自动切换成KHz,同理大于1000KHz时,切换为MHz,这部分比较容易实现,在NIOS IDE中用C语言对测量结果进行判断并控制液晶显示即可. 3.1NIOS II 处理器结构图 图10 NIOS II软核原理图Fig. 10 Illustration for NIOS II soft-core 本设计中用到的NIOS II软核是由SOPC Builder工具构建而成,CPU选择性能最高的NIOS II/f型,系统时钟定义为50MHz,RAM选择片内存储器,设置其大小为32KB,此外还设置了EPCS存储控制模块,并锁定其地址为0x00000000,主要用于程序的调试和下载;JTAG接口选择默认的标准型,其它数据和控制口全部由PIO来定义. 图10是最后生成的NIOS II软核原理图.从图中可以看到生成了众多的IO口,都是前面自己定义好的,左边的端口为输入口,右边的端口一般为输出,但也可以是双向口,如负责传输数据给液晶的8位数据口就是双向口.其中端口名以EPCS结尾的接口是由EPCS存储控制器自动生成的,需要根据芯片型号自行分配引脚.该原理图需要放在顶层文件中与前面生成的模块相连接,实现数据的传递. 在顶层文件编译通过后,就可以使用NIOS IDE对NIOS II软核进行编程控制,主要对传递进来的数据进行处理和计算,然后将处理后的数据传递给液晶显示,从而完成整个系统的流程. 3.2顶层文件原理图分析 整个系统方案实现的原理图如下: 图11 整体方案实现原理图Fig. 11 Illustration for the whole system implementation 由图11可知,整个系统用到了两个锁相环,其中一个用于生成各种系统时钟信号,另一个用于生成各种测试用的信号,分频模块、周期计数模块和占空比计数模块都被整合到了频段判断和处理模块里,不在顶层文件里显现出来;经过频段判断和处理模块后的数据全部交给了NIOS II处理器处理,这样可尽量减少调用资源,使整个系统运行得更加流畅. 3.3系统占用资源分析 图12 整个系统占用资源分布图Fig. 12 Resource distribution map for whole system 由于数据的计算和处理都是在NIOS嵌入式处理器中完成,这大大减少了系统资源的占有率,整个系统占用的资源情况分布如图12所示. 由图12可知,即使使用了32位的计数器,整个系统所占用的LES也只在31%左右,寄存器资源更是只占20%,由于该芯片内存储总量为42KB,而在NIOS II软核中就分频了32KB,所以在存储方面共占用了75%的资源,PLL锁相环使用了2个,芯片也支持2个,所以占用100%,虽然本设计用了32的计数器,但由于32位的数据口并没有引出,而是在芯片内部的电路直接通过顶层文件连接起来,所以引脚占用也很少,这也是FPGA器件的一大优点. 3.4系统硬件测试分析 图13 液晶显示测量数据图Fig. 13 LCD display for the measured data 本设计是基于NIOS II软核的频率计设计,其主要功能是测量脉冲信号的频率和占空比,并将结果显示在液晶屏上.所测量的频率范围在1~400MHz,误差不超过10-4;占空比测量范围在10%~90%(频率小于2MHz时),其误差不超过10-1;在此附上液晶成功显示测量结果的图,并以此作简单的说明. 如图13所示,该信号是由FPGA芯片内部锁相环分频后发出的,然后将其接到待测信号的输入口上,通过设计好计数器和频段判断将计数结果传送给NIOS II处理器,NIOS II处理器对计数结果进行运算后转换成频率和占空比,最终通过液晶显示在液晶屏上,由于是由同一块芯片产生的信号,所以误差极小,在精度要求范围内. 本设计基于Altera的NIOS II软核,实现了一款高精度、高带宽、紧凑灵活的数字频率计.对脉冲信号进行频率测量时,其理论最高测量频率可达4GHz,但在实际中有很多频率信号不一定是方波的形式,像正弦波、三角波和锯齿波等必须要将其转换成方波形式才可以进行测量,这时需要在前端加一个放大整形电路.其次是在本设计中对液晶的控制是并行模式的,如果能将其改为串行模式,其接线将大大减少,虽然显示速度会因此而下降,但就目前的运行速度而言,降低后也在接受范围内.最后是在后续的研究中可以使用更低版本的芯片来实现,因为这个版本中芯片资源还大有剩余,只占30%左右. [1] ZHOU W. Systematic Research on High-Accuracy Frequency Measurements and Control[J].静冈大学大学院电子科学研究科研究报告,2001,22:189-191. [2] ASHOUR M A, SALEH H J. An FPGA implementation guide for some different types of serial-parallel multiplier structures[J]. Microelectronics Journal,2000,31(3):161-168. [3] 潘松,黄继业,潘明.EDA技术实用教程:VerilogHDL版[M].4版.北京:科学出版社,2010. [4] 吴军,沈珊瑚,何忠.基于SOPC的U盘加解密系统实现[J].杭州师范大学学报(自然科学版),2016,15(1):95-101. [5] 王诚.Altera FPGA/CPLD设计[M].2版.北京:人民邮电出版社,2011. [6] 包本刚.基于FPGA的全同步数字频率计的设计与实现[J].测试技术学报,2008,22(2):99-102. [7] 张谨,宗发保,邹鹏毅,等.基于FPGA的铯光泵磁力仪频率计设计[J].海洋测绘,2015,35(2):80-82. [8] 孙虹,何宏,张大建,等.基于VHDL和FPGA的自适应数字频率计的研究与设计[J].天津理工大学学报,2008,24(1):24-27. Implementation of Digital Frequency Meter Based on Nios II Soft-core WU Jun, SHEN Shanhu, Lu Haoyu (Hangzhou Institute of Service Engineering, Hangzhou Normal University, Hangzhou 311121, China) In this paper, a precise digital frequency meter was implemented using Cyclone IV E series FPGA chip resources and NIOS II soft-core. Verilog Language was used for the frequency measurement function, while C language was used for the data manipulation. Then the data was transferred to the LCD module based on real-time operations. This design owned the features of large measuring bandwidth, small area and stable data transformation. Also each module in the whole system was independent to each other, and the whole system was flexible and highly effective. NIOS II soft-core; FPGA; SOPC; digital frequency meter 2016-04-19 浙江省信息安全联盟课题-安全芯片预研项目(kz13013003);浙江省科技创新计划项目(2013TD03);杭州师范大学科研启动基金项目(PF14002004005). 沈珊瑚(1981-),女,讲师,博士,主要从事嵌入式系统及安全芯片实现相关研究.E-mail:shshen88@163.com 10.3969/j.issn.1674-232X.2016.05.017 TP368 A 1674-232X(2016)05-0549-07

3 整体方案分析

4 总结和展望