音视频数据采集接口电路设计及实现

2016-10-17那彦,底鹏

那 彦,底 鹏

(西安电子科技大学 电子工程学院,陕西 西安 710071)

音视频数据采集接口电路设计及实现

那彦,底鹏

(西安电子科技大学 电子工程学院,陕西 西安 710071)

针对普通缓存器存储溢出或者读空的问题,对音视频数据采集系统的接口电路进行了设计和实现。该接口电路可实现压缩后的音频和视频数据的FPGA缓存和PCI总线传输。利用乒乓操作的方法控制缓存器的切换,以保证数据的无缝传输。仿真试验结果表明,所设计的接口电路,其准确性和稳定性均满足项目要求,且具有较好的工程使用价值。

音视频数据压缩;FPGA;缓存器;PCI总线

视频应用在高速发展的同时,也面临着一些必须解决的问题,这主要是原始的信息量过大造成的[1]。音视频压缩已发展得较为成熟,因此对于音视频压缩数据的存储和传输就显得尤为重要。并且针对具体的项目还要设计专用的缓存器和接口电路以配合相关的音视频数据采集系统[2]。

1 系统总体设计

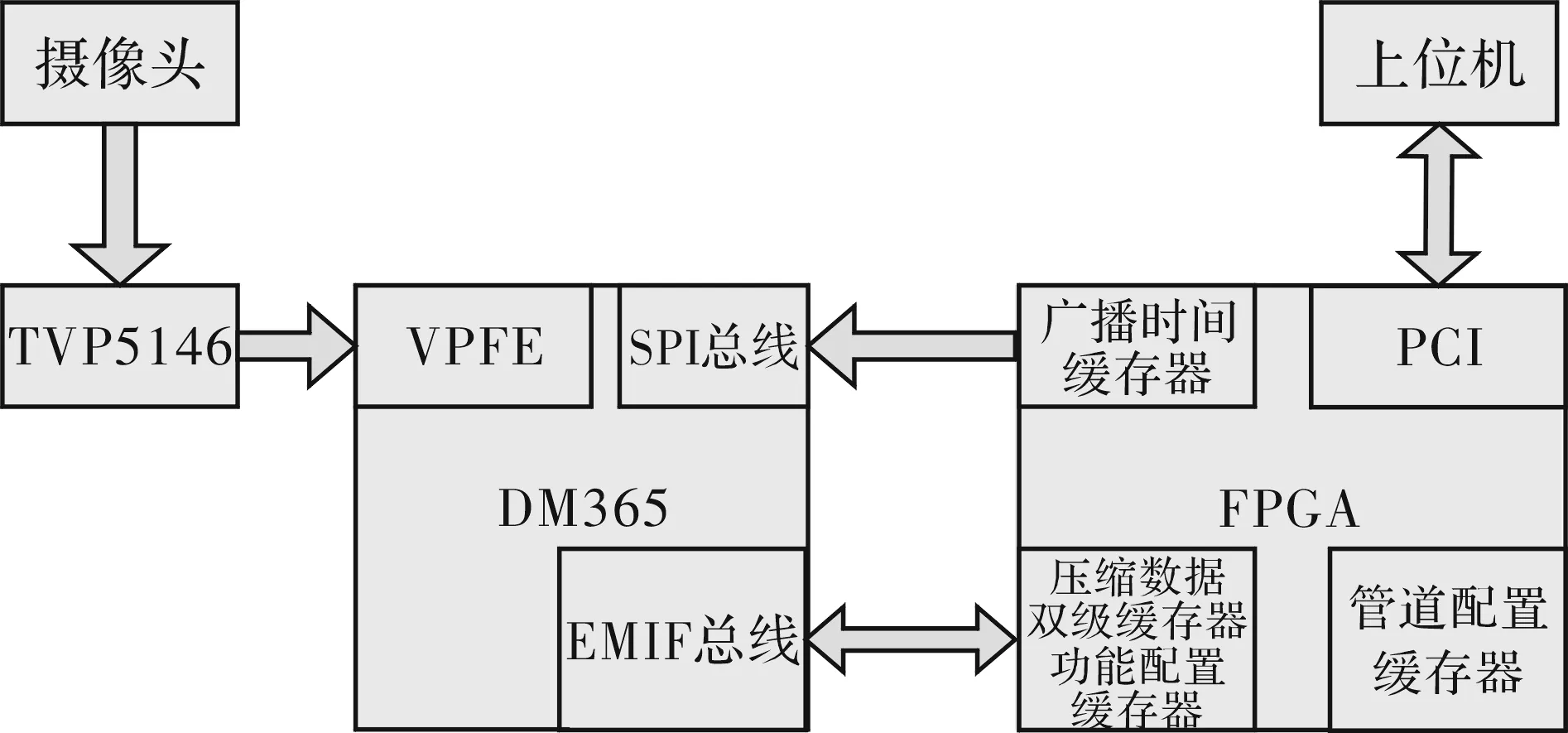

音视频压缩编码传输方案如图1所示。上位机通过PCI总线将功能配置信息、管道配置信息和广播时间信息传入FPGA对应的缓存器中,这些信息包括对DM365的配置信息,对FPGA内部的压缩数据双级缓存器的配置信息和对视频显示时间的管理信息。只有先通过这些配置手段,DM365和FPGA才能正常工作[3]。

图1 音视频数据采集系统原理框图

配置完成后就可对音视频进行采集。先通过摄像头采集到的RGB模拟视频流,传入TVP5146做采样处理,输出YCbCr4∶2∶2格式的视频流,再传入TMS320DM365的视频处理前端VPFE,在DM365中完成色彩空间转变,形成YCbCr4∶2∶0格式的视频流,由此完成模拟视频的采样工作,视频信号转换为数字视频[4]。通过MIC采集到原始声音传入TLV320AIC3101中进行采样处理,由模拟声音变为数字声音,传输到DM365中,等待下一步压缩处理。

在DM365对数字视频流和数字音频流进行MPEG-4压缩编码,形成ES流。ES流是经过音视频编码器编码后得到的音视频基本流[5-6]。ES流通过复用器打包,形成供传输和存储的TS流。DM365通过EMIF总线,将TS流数据传入FPGA的压缩数据双级缓存器中。由于压缩数据双级缓存器中每小周期传输的数据数量,已由管道配置信息进行了设置。因此,通过输入输出开关切换,将第一级缓存区中的数据传输到第二级缓存区中。在每个小周期信号到来时,通过第二级缓冲区与PCI总线,将TS流数据传到上位机,由此完成数据采集工作[7]。

上位机接收到TS流后,将其经过解复用器及MPEG-4解码器,形成可供播放的音视频[8-9]。

2 接口电路主要分系统设计

2.1压缩数据双级缓存器

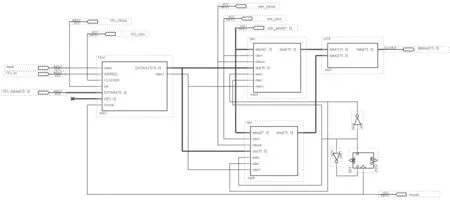

针对项目需求,设计一种满足条件的存储器显得尤为重要。在此设计一种双级缓存器。第一级为FIFO存储器,第二级为RAM存储器。因此要满足项目的要求,这里所说的存储器不是典型的FIFO存储器和RAM存储器,而是对其进行了更改或改进。双级缓存器逻辑如图2所示。

图2 双级缓存器逻辑图

在每一次小周期信号到来时,类FIFO缓存区均会对其内部数据进行一次判断。若此时的数据量满足管道缓存区中配置信息要求的数据量,那么类FIFO缓存区就会将对应的数据量写入此时接收数据的RAM中,而下一个小周期到来时,再将数据输出。若此时数据量不满足管道缓存区中配置信息要求的数据量,则类FIFO缓存区就会输出对应数量的空数据(16bit的0),供RAM接收。下一个小周期到来时,RAM将空数据输出。

2.2功能配置信息缓存器设计

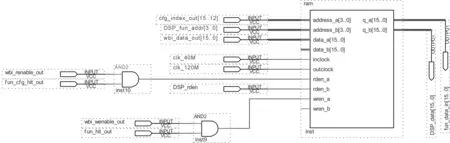

功能配置信息缓存区,用于存储由上位机发送过来的功能配置信息,这一缓存区由地址线cfg_index_out高4位进行寻址,在前12位管道索引均为0时,通过后4位索引功能配置信息缓存器地址。功能配置信息,主要包括管道数量、最高采样率、最低采样率、输入上限、输入下限、功能管理[10]。还有其他和音视频数据压缩有关的配置信息,主要包括视频参数、音频参数、字幕选项、字幕位置等。

图3 功能配置信息缓存器逻辑图

图3为功能配置信息缓存器逻辑图。当功能配置信息及管道配置信息被写入板卡后,再通过EMIF接口向DSP传输配置信息之前,还需对配置信息进行回读验证。回读验证,是将配置信息完全通过数据线回读,在上位机验证无误后,主控板会发出一个握手信号,将设备命令总线dev_cmd_out[2]置高,从而提供验证无误使能,使DSP读取配置数据。功能信息的配置信息回读时,将功能空间的配置信息输入到片上总线桥的fun_data_in接口,以对功能空间的配置信息进行验证。

2.3广播时间缓存区

经解压缩后的视频播放时要加入时间信息,因此在每一个小周期开始时,均会由主设备发送时间信息,通过PCI总线存储在时间信息缓存器中,以备DSP进行读取,用来验证DSP记录时间是否准确。

广播时间存储区的读写时序如下:采用40MHz的写入时钟,使能端包括写使能和广播时间击中使能,由地址线brdcase_offset_out来完成寻址工作。

图4 广播时间缓存器逻辑图

因为DSP要由广播时间缓存区读取时间信息,由此设计通过DSP芯片的SPI总线读取广播时间缓存器信息。设计的广播时间缓存器如图4所示,sipo模块用于接收从DSP的SPI总线传输过的地址信息。经过sipo模块的串并转换将串行地址线转变为4位并行地址线[11]。通过这4位地址线寻址RAM模块中的时间信息,读出此时间信息。再通过16位数据总线传输到piso模块,piso模块将16并行数据位数据转为串行数据输出。

3 接口电路仿真试验

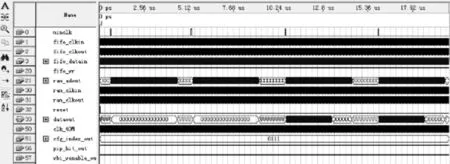

3.1压缩数据双级缓存器仿真

如图5所示,为压缩数据双极缓存器的仿真结果。可看出图中共有4个小周期信号到来,第1个小周期信号到来时,开始在类FIFO存储器中存储数据,第2个小周期到来时,类FIFO开始在第1个类RAM存储器中写数据。第3个小周期到来时,类FIFO开始在第2个类RAM存储器中写数据。此时,第1个类RAM存储器开始通过输出端读出数据。并经过细微验证数据无误,且可看出输出数据具有连续性,并无数据输出延迟等情况发生。

图5 压缩数据双级缓存器仿真结果

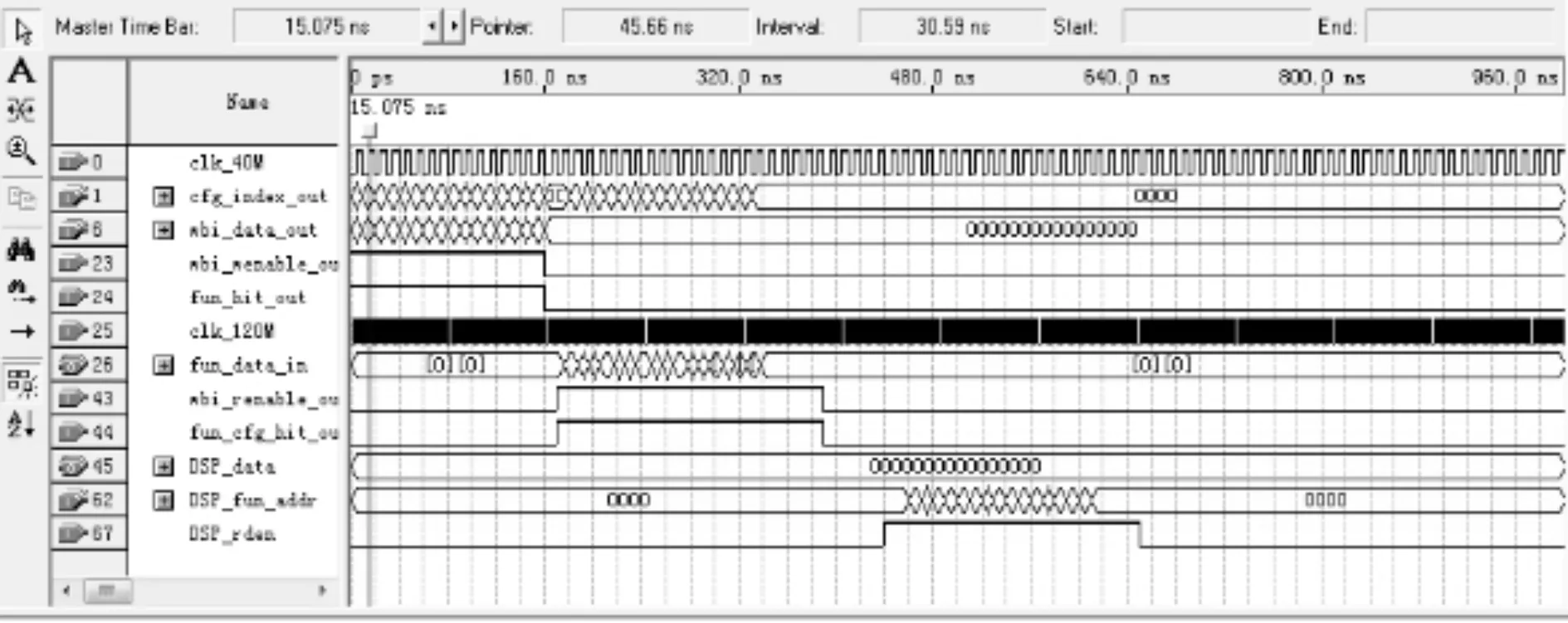

3.2功能配置信息缓存器仿真

如图6所示,为功能配置信息缓存器的仿真结果。在第一阶段中,通过wbi_data_out向缓存器中写入数据。第二阶段为数据回读验证阶段,此阶段中数据通过dun_data_in数据总线回读,经过PCI总线流向上位机,并在上位机进行验证。第三个阶段为DSP读数据阶段,DSP通过EMIF接口将数据读入,并通过此数据进行视音频数据采集参数的配置。通过仿真结果中输出数据和输入数据的对比,设计的功能配置信息缓存器的准确性得到了验证。并可看出输出数据具有连续性,并无数据输出延迟等情况发生。

图6 功能配置信息缓存器仿真结果

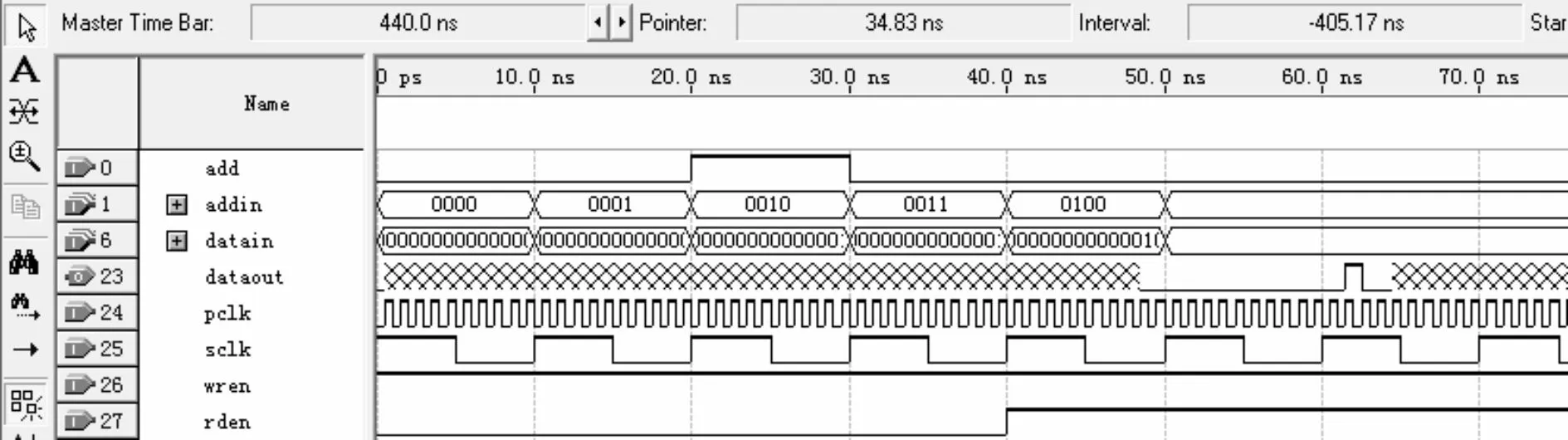

3.3广播时间信息缓存器

如图7所示,为广播时间信息缓存器,可看出地址位是0100,对第5个寄存器中的信息进行寻址,第5个寄存器中信息为0000000000000100,对比dataout数据线的数据,可看出数据的正确性。

图7 广播时间信息缓存器仿真结果

4 结束语

本系统实现了对于音视频数据采集接口电路的设计,该接口电路可实现压缩后的音频和视频数据FPGA缓存和PCI总线传输,解决了普通缓存器存储溢出或读空的问题。经反复修改和多次仿真,系统工作的稳定性和准确性已得到了验证,为音视频接口电路的设计提供了方向。

[1]王小红,周渊平,方晓翠.嵌入式视频监控系统的设计和实现[J].通信技术,2011,44(6):105-106.

[2]闫光.基于H.264的实时视频监控系统的设计与实现[D].北京:北京邮电大学,2012.

[3]王飞.基于DaVinci技术的视频编码系统实现[D]. 西安:西安电子科技大学,2012.

[4]高厚琴,杨盈昀.电视原理与接收技术[M].北京:国防工业出版社,2002.

[5]许春冬,陈良军.嵌入式数字视频监控系统中串口通信的设计与实现[J].电子科技,2005(11):105-106.

[6]王建平,季学锋,穆道明.基于DSP的多路音/视频采集处理系统设计[J].电子设计工程,2006(6):27-31.

[7]赵保军,史彩成,毕莉,等.基于FPGA和DSP实现的实时图像压缩[J].电子学报,2003,31(9):1317-1319.

[8]李莉.AlteraFPGA系统设计实用教程[M].北京:清华大学出版社,2014.

[9]陈宗仁.论音视频数据采集传输系统的设计与实现[J].科技情报开发与经济,2011,21(27):120-122.

[10] 胡烨.音频数据采集系统的设计与实现[D].西安:西安电子科技大学,2012.

[11] 金鹏飞,毛永毅,张宏君.一种基于FPGA的PCI接口设计[J].测控技术,2013(7):79-82.

Design and Realization of the Audio and Video Signal Acquisition Interface Circuit

NAYan,DIPeng

(SchoolofElectronicEngineering,XidianUniversity,Xi’an710071,China)

Inthispaper,theinterfacecircuitofanaudioandvideodataacquisitionsystemisdesignedandrealizedtosolvetheproblemofbuffermemoryoverfloworreademptyissue.TheinterfacecircuitisdesignedforaudioandvideocompressiondataFPGAcacheandPCIbustransfer.Themethodofcontrollingtheuseofping-pongoperationswitchbufferensuresseamlesstransferofdata.Simulationresultsshowthattheaccuracyandstabilityoftheinterfacecircuitdesignedmeetstheprojectrequirementsandhasgoodengineeringapplicationvalue.

audioandvideocompression;FPGA;buffer;PCIbus

2015- 11- 17

那彦(1964-),男,博士,教授。研究方向:图像融合,信号处理。底鹏 (1989-),男,硕士研究生。研究方向:信号采集及处理系统设计。

10.16180/j.cnki.issn1007-7820.2016.09.041

TN919.8

A

1007-7820(2016)09-148-04