Flash存储器并行耐久测试方法

2016-10-15王小强蔡志刚吕宏峰

罗 军,王小强,蔡志刚,孙 宇,吕宏峰

(工业和信息化部电子第五研究所,广东 广州 510610)

Flash存储器并行耐久测试方法

罗军,王小强,蔡志刚,孙宇,吕宏峰

(工业和信息化部电子第五研究所,广东 广州 510610)

传统闪存(Flash)芯片耐久测试需要对整块芯片按扇区串行进行擦写测试,测试时间长、效率低、成本高,不利于其批量耐久测试和产业化发展。该文基于“资源换速度”的思想提出一种高效的Flash存储器并行耐久测试方法,通过对多片Flash芯片并行进行擦写测试,对不同芯片擦写不同扇区来提升其耐久测试效率,并进一步对耐久测试Flash芯片的不同扇区等效性进行分析,对等效性需要满足的条件和要求进行探讨。实验结果表明:并行耐久测试能有效缩短测试时间,其效率提升程度与并行测试的芯片数量成正比,加速测试结果与理论曲线符合较好。

闪存;存储寿命;耐久测试;扇区等效性;并行测试

0 引 言

随着移动存储技术的快速发展和移动存储市场的不断扩大,Flash存储器的市场需求快速增长[1]。由于具有低成本、高密度、掉电不丢失、便携、可靠等优点,其在移动产品中获得了广泛的应用[2-3]。随着大规模集成电路工艺的进步,Flash存储器的质量可靠性成为影响其大量应用的关键因素[4]。为保障芯片在全寿命期间能够稳定可靠地工作,Flash存储器在出厂前需要进行全面细致的测试;其中,耐久测试为保障Flash存储器芯片擦写次数满足寿命周期要求的重要途径。

为了使耐久测试的流程规范化,国外早在20世纪70年代就发布了用于评价非易失性存储器编程/擦除耐久和数据保持试验的方法。在2010年版的MIL-STD-883H《微电子器件试验方法标准》中就包含了编号为1033的耐久寿命试验方法[5]。目前国内比较通用的方法是采用固态电子技术协会(joint electronic engineering council,JEDEC)2011年版的JESD22-A117C《电可擦除可编程只读存储器(EEPROM)编程/擦除耐久和数据保持应力试验》[6],该标准规定了用于耐久和保持试验的要求,然而并没有详细说明对非易失性存储器进行耐久和保持试验的效率提升方法。由于Flash存储器只能将存储单元内的数据从“1”写为“0”,而不能从“0”写为“1”,故在对Flash存储器进行写入之前需要将整个扇区或整个存储器芯片的数据擦除,这是一个非常耗时的过程;因此,在对Flash存储器进行耐久测试的时候,为了达到全寿命周期(如10万次擦写次数)的测试要求,迫切需要开发高效的耐久测试技术。

近年来,Flash存储器测试的研究热点主要集中在测试算法的优化改进方面。如张曦等[7]针对Flash存储器的直流及漏极干扰,在Mohammand失效模型的基础上提出了一个更优的测试算法。高剑等[8]在详细分析Flash存储器结构和测试原理基础上提出了一种比传统棋盘格测试更高效的算法。王续朝等[9]通过对大规模数字集成电路测试系统的算法图形功能进行改善,研究了适应于地址复用型Flash存储器的测试技术。然而,上述研究主要通过Flash存储器测试算法的优化和改进来提升其测试效率,而较少关注Flash存储器测试流程的优化和改进。

“资源换速度”的思想在集成电路设计中获得了广泛的应用[10-11],通过消耗更多的芯片资源可以大大提高系统的速度,增加吞吐量。通过引入这一思想,本文提出了一种高效的Flash存储器并行耐久测试方法。传统上为了验证Flash存储器芯片是否能够达到预期寿命,通常采用串行的顺序对多片Flash芯片依次进行所有扇区的耐久测试,测试效率低。本文提出的方法基于同批次的Flash存储器芯片,分别对不同芯片的不同扇区同时进行耐久测试,对传统耐久测试流程进行了改进,从而提升了测试效率、降低了成本。

1 Flash存储器耐久失效机理及测试标准

Flash存储器是一类重要的非易失性存储器(nonvolatile memory,NVM),其耐久测试失效[12]主要由以下方面引起:

1)隧道氧化层击穿

隧道氧化层的性能可以在工艺可靠性中的隧道氧化层击穿电荷(Qbd)测试中来反应,编程一定次数后,随着隧道氧化层缺陷的增加、Qbd的逼近,最后导致氧化层崩溃而无法实现编程和擦写。

2)电荷俘获

电荷俘获为编程操作时电荷被氧化层俘获。这些俘获的电荷改变了注入电场,也改变了输入和输出浮栅的电荷数量。这将导致阈值电压在高低电平间差异变小,从而可能不被感应电路判别出来,导致失效。

3)隧道薄氧化层

氧化层中的缺陷在高电场的作用下将会导致氧化层漏电,是限制NVM器件耐久失效的主要原因。当氧化层的总面积随存储器密度增加而增加时,单个存储器单元失效的概率也在增加。而氧化层中缺陷密度主要取决于工艺条件,并随着先进工艺技术的使用而降低。

Flash存储器的耐久测试方法依赖于国际通用测试标准JESD22-A117《电可擦除可编程只读存储器(EEPROM)编程/擦除耐久和数据保持应力试验》。2011年JESD22-A117C正式发布,其中规定了对耐久和保持试验程序的要求,如间歇时间、试验应力、试验内容方法等,可适用于从晶圆级到器件级的产品。JESD22-A117C中规定不必对存储器中所有的存储单元进行擦写耐久试验,只需要满足用户认可的循环模式、电压、温度和频率,以便缩短试验时间。然而从用户的角度来看,对存储器中所有的扇区进行耐久试验更有利于对其质量可靠性的控制,而传统的耐久测试方法具有测试时间长等局限,不利于耐久测试效率的提升。

2 Flash存储器耐久测试流程

Flash存储器的耐久测试表征了其反复存储、擦除数据的能力。耐久特性表现于存储器的阈值电压区间,它与编程次数有密切的关系。随着编程次数的增加,存储器的阈值电压区间逐渐变小直至失效。传统的Flash存储器耐久测试流程包含设定擦写次数、启动耐久测试、测试结束记录测试结果等过程。由于对Flash芯片进行写入之前要进行擦除操作,故对Flash芯片进行擦写是一个非常耗时的过程。如对典型的一块包含32个扇区的Flash芯片,完成10万次擦写测试需要高达10h,如果要做大量的Flash存储器耐久测试,时间的耗费将会更长。因此,如何提升Flash芯片耐久测试的效率是一个影响其发展的关键问题。

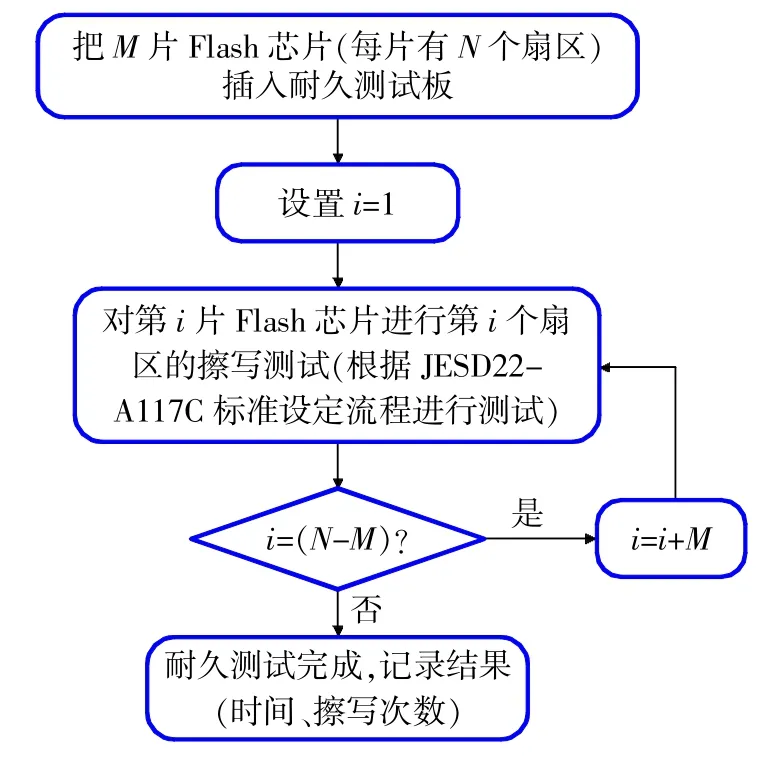

本文通过引入“资源换速度”思想,将多片Flash芯片的不同扇区同时进行耐久测试来提升其测试效率,缩短测试时间。改进的Flash存储器耐久测试流程如图1所示,通过采用多片Flash芯片并行耐久测试来实现效率的提升。图中共有M片Flash芯片,每片Flash芯片包含N个扇区(M≤N),通过选择M片Flash芯片中的M个扇区同时进行耐久测试,从而达到并行测试的目的。其中,M可以根据实际需要选择,它表征了Flash芯片中不同扇区的并行测试程度,是一个可以反映效率提升程度的数值。理论上,M值越大,Flash芯片耐久测试效率越高,同时使用的Flash芯片个数也越多。

3 Flash存储器耐久测试扇区等效性

在Flash存储器的并行耐久测试中,需要对不同Flash存储器的不同扇区同时进行耐久测试以便提升测试效率,并以此耐久测试结果来表征单片Flash存储器的耐久能力,前提条件是保证多片Flash存储器芯片的质量一致性。由于待测Flash存储器是同一个批次并且经过质量检测和筛选,因此Flash芯片的质量一致性在实验中是默认得到有效保障的。文中通过对不同Flash芯片中的不同扇区进行耐久测试来表明同一批次中的Flash存储器芯片的不同扇区在耐久测试中具有等效性,从而进一步说明对多片Flash芯片的不同扇区进行耐久测试可以等效成单片Flash芯片所有扇区的耐久测试。图2展示了多通道Flash芯片耐久测试试验装置,拥有12个并行通道和LED显示器,可以实时显示各个通道中Flash芯片的测试状态。

图1 改进的Flash存储器耐久测试流程

图2 Flash芯片并行耐久试验装置

耐久测试步骤如下:首先将测试主板、Flash转接板准备好,调节直流稳压电源到9V输出,连接电源,确保测试通路正常。准备受试器件(DUT)配置文件(CFG文件),在硬件系统上电后,个人计算机(PC)启动耐久测试客户端软件,设定DUT信息和定时信息,打开串口,然后进行Flash存储器的耐久测试。

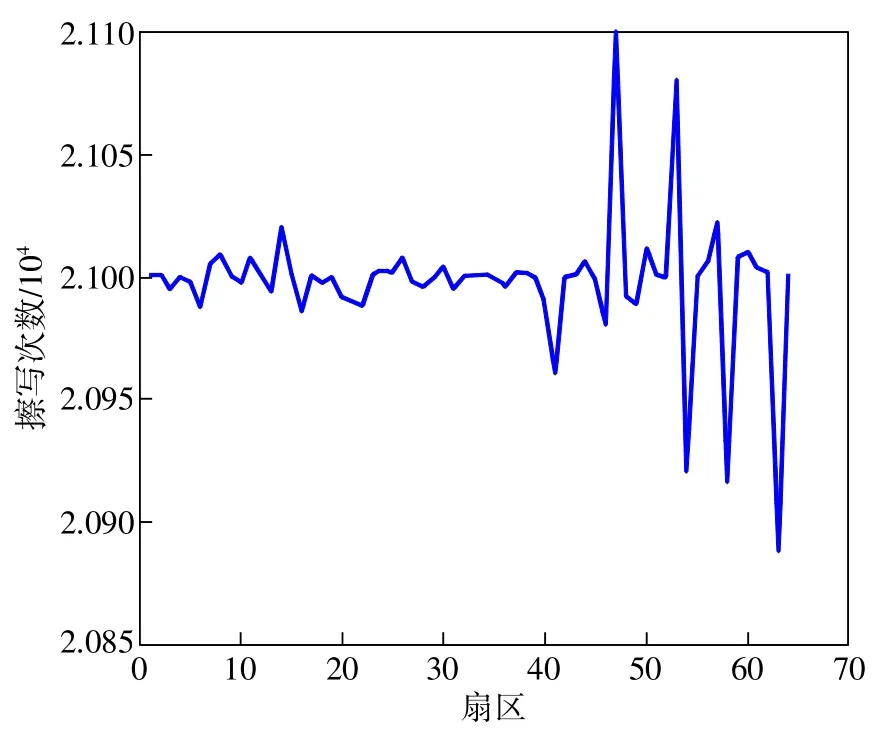

实验从同一批次的Flash存储器中随机选择了4片Flash芯片,然后从每片Flash芯片中随机选择16个扇区来对每个扇区单独进行耐久测试,得到64个耐久测试数据,如图3所示。从图中可以看出同一批次芯片不同扇区之间的耐久擦写次数(寿命)具有一定的差异性,但这种差异的范围是可以得到有效控制的,这表明同一批次中不同芯片的扇区的擦写寿命是可控的,其可控性可以进一步从图4和图5中的数据中分析得出。

图3 Flash芯片不同扇区下擦写次数统计

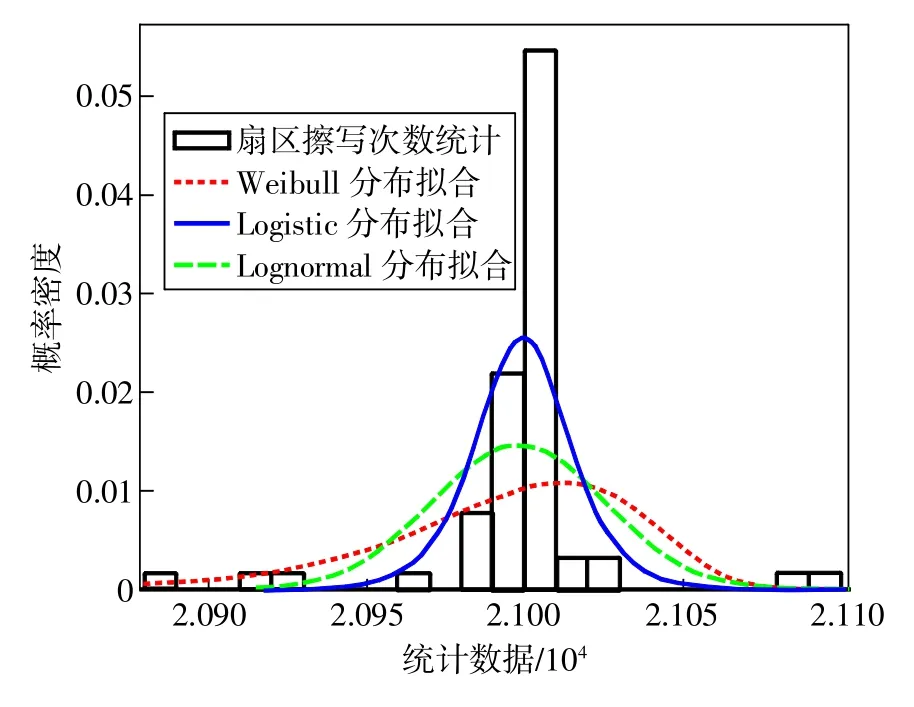

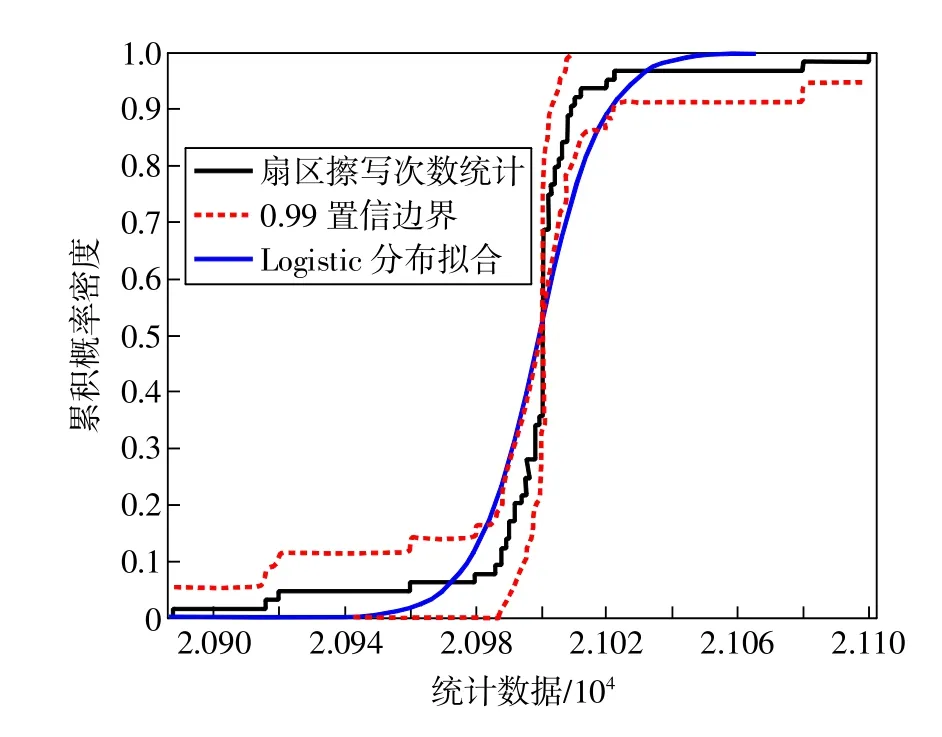

图4对图3中不同Flash存储器芯片不同扇区的耐久擦写次数进行了统计,并给出了不同函数的拟合曲线。从图中可以看出Logistic分布在耐久擦写次数的中心部分具有最大的权重,这说明相比Weibull和Lognormal函数,Logistic函数具有最好的拟合,更能够反映出Flash存储器耐久擦写次数的统计特性。

图4 Flash芯片不同扇区擦写次数统计及概率分布

图5给出了Flash存储器芯片擦写次数统计及其0.99置信区间,从图中可以看出Logistic分布曲线基本上落入0.99置信区间的范围。因此,结合图3~图5的分析,可以发现在Flash存储器芯片扇区的全寿命耐久擦写测试中,Logistic分布相比Weibull和Lognormal分布能够更好地表征Flash芯片中扇区的擦写次数统计特性,而且Logistic分布曲线基本能够满足Flash芯片中扇区的擦写次数统计0.99置信区间的概率分布要求,在此情况下可以认为同批次不同扇区的Flash存储器芯片满足扇区等效性的要求。

图5 Flash芯片不同扇区擦写次数统计及置信区间

4 Flash存储器耐久测试效率分析

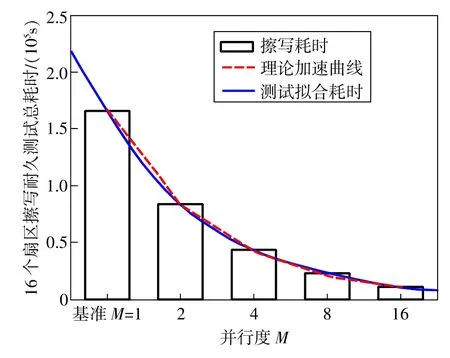

通过耐久测试分析不同并行程度下耐久测试的加速效果,耐久测试流程如图1所示,图中M的大小表明了Flash芯片耐久测试的并行程度(M越大,则并行程度越高,测试效率提升越大)。图6展示了不同并行程度下的Flash芯片擦写耗时,图中柱状矩形是在不同M值下的实际耐久测试耗费时间,蓝实线是实际的拟合耗时曲线,而红虚线则是根据理论得到的加速曲线(理论上M每增加一倍,效率提升一倍)。从图中可以看出随着并行程度(M)的增加,Flash芯片耐久测试效率明显提升,有效缩短了测试时间。同时可以发现测试拟合耗时与理论加速曲线基本吻合,他们之间差异形成的原因主要是由耐久测试流程中预处理和后处理的相关操作造成的。因此,文中提出的Flash存储器并行耐久测试方法可以有效的降低测试时间,提升测试效率。

图6 不同并行程度下的Flash芯片擦写耗时对比

5 结束语

本文针对传统Flash存储器耐久测试耗时长、成本高等不足,引入“资源换速度”的设计思想,改进了传统耐久测试流程,提出了并行耐久测试方法。通过实验分析了Flash存储器芯片的扇区等效性,为其并行耐久测试需要满足的条件和前提进行了积极的分析和探索。文中提出的Flash芯片并行耐久测试方法有效的降低了Flash存储器芯片的耐久擦写测试耗时,提升了耐久测试效率,并且可以根据实际情况调整并行程度,具有较大的灵活性和适应性,可以为其他非易失性存储器芯片的高效耐久测试提供指导和借鉴。

[1]郑文静,李明强,舒继武.Flash存储技术[J].计算机研究与发展,2010,47(4):716-726.

[2]RAJSUMANR.Designandtestof large embedded memories:an overview[J].IEEE Des Test Comput,2001,18(3):16-27.

[3]吴东坡.Flash存储器技术与应用[J].微电子学与计算机,1998(6):55-56.

[4]潘立阳,朱钧.Flash存储器技术与发展[J].微电子学,2002,32(1):1-5.

[5]李锟,张秋.EEPROM耐久和数据保持试验方法标准分析[J].信息技术与标准化,2012(4):62-66.

[6]Electrically erasable programmable ROM(EEPROM)prog ram/eraseenduranceanddataretentionstresstest:JESD22-A117C[EB/OL].JEDEC Solid State Technology Association,2011-12-20.http:∥www.jedec.org/standardsdocuments/results/JESD22-A117.

[7]张曦,朱一杰,俞军.一种优化的Flash存储器测试算法[J].微电子学与计算机,2004,21(5):121-123.

[8]高剑,郭士瑞,蒋常斌.Flash存储器的测试方法[J].电子测量技术,2008,31(7):117-120.

[9]王续朝.地址数据复用型Flash存储器测试技术研究[J].电子测试,2012(10):17-22.

[10]LUO J,HUANG Q J,CHANG S,et al.High throughput cholesky decomposition based on FPGA[C]∥Proceedings of International Congress on Image and Signal Processing,2013(11):1644-1648.

[11]LUO J,HUANG Q J,Chang S,et al.Compact beamformer design with high frame rate for ultrasound imaging[J].Sensors&Transducers,2014,168(4):237-242.

[12]SEIICHI A,RIICHIRO S,GERTJAN H,et al.Reliability issues of Flash memory cells[J].Proceedings of the IEEE,1993,81(5):776-788.

(编辑:莫婕)

Parallel endurance testing method for Flash memories

LUO Jun,WANG Xiaoqiang,CAI Zhigang,SUN Yu,LÜ Hongfeng

(CEPREI,Guangzhou,510610,China)

Traditionally,the endurance test of Flash chips is unsuitable for massive production of Flash memories because its sector-by-sector serial procedure is time consuming,inefficient and uneconomical.To promote the test efficiency,a parallel method has been proposed in this paper by using of multi-sectors of different Flash chips at the same time.It has been derived from the idea of tradeoff between resource usage and speedup.Experimental results show that the speed of endurance test is accelerated and the degree of efficiency promotion is in direct proportion to the number of Flash chips.The test results tally with the theoretical results.

Flash;memory lifetime;endurance test;equivalence of sectors;parallel test

A

1674-5124(2016)05-0024-04

10.11857/j.issn.1674-5124.2016.05.005

2015-11-20;

2015-12-29

罗军(1986-),男,湖南衡南县人,工程师,博士,主要从事元器件检测、信号处理等相关工作。