基于FPGA的IRIG-B(AC)时间码解码器的设计*

2016-10-13贾磊崔永俊杨兵王晋伟

贾磊,崔永俊*,杨兵,王晋伟

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

基于FPGA的IRIG-B(AC)时间码解码器的设计*

贾磊1,2,崔永俊1,2*,杨兵1,2,王晋伟1,2

(1.中北大学电子测试技术国家重点实验室,太原030051;2.中北大学仪器科学与动态测试教育部重点实验室,太原030051)

为了解决IRIG-B(AC)码解码精度低的问题,提高解调系统的稳定性,提出了一种利用高性能FPGA实现解调IRIG-B(AC)码的解码器。通过调用FPGA的IP核生成乘法器与FIR低通滤波器,将B(AC)码中的交流分量滤除掉,然后根据其幅值进行解调。该解码器能够快速准确地解调出IRIG-B(AC)码的时间信息,并输出与此时间信息对应的秒脉冲,通过输出端口将解调出的时间信息传输到上位机显示。通过大量试验证明该解码器准确度高、稳定性强,能够满足各种应用场所对IRIG-B(AC)码授时的要求。

IRIG-B码;解码;滤波;A/D转换;秒脉冲

IRIG时间编码序列,是由美国靶场间仪器组IRIG (Inter Range Instrumentation Group)提出来的,被广泛应用于时间信息传输系统中[1-2]。常规的IRIG-B码解码设备采用自动控制增益电路、比较器以及过零检测电路实现解调,由于信号经过比较器和过零检测电路时易受干扰影响产生抖动和零点漂移,从而造成输出的时间信息出现抖动,降低了传统解码设备的精度。

针对以上问题,设计了一种基于FPGA的IRIG-B (AC)码解码器,该设计以FPGA为控制核心,通过LTC1068-200滤波芯片和ADS8365模数转换芯片对交流码进行采集,并将其转换为数字量,供FPGA内部解码模块分析与解调,通过程序的输出模块将解调出IRIG-B码的时间信息与秒脉冲输出。该解码器体具有体积小、精度高、兼容性强等特点,能够满足多种场合对IRIG-B(AC)码授时的要求。

1 IRIG-B码格式

IRIG-B码通常采用串行时间码格式,时帧速率为1帧/s,每一帧由100个码元组成,每个码元的周期为10 ms[3];IRIG-B码分直流、交流两种,未经幅度调制的为IRIG-B(DC)码(直流),经过幅度调制的为IRIG-B (AC)码(交流)[4]。IRIG-B码中每一个脉冲信号代表一个码元,时间信息用码元使用二进制来表示,占空比为1∶4的码元表示‘0',占空比为4∶1的码元表示‘1',占空比为1∶1的码元表示位置标识位‘P'[5]。

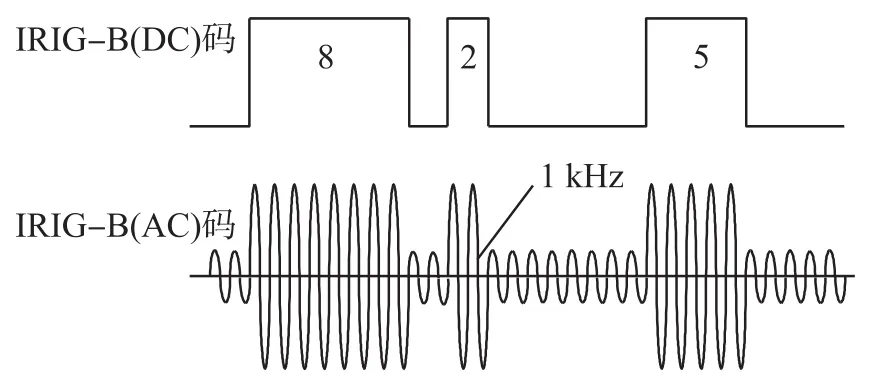

IRIG-B(AC)码标准载波(通常为1 kHz的正弦波)幅度调制而成,标准的调制比为3∶1,且使其过零点与码元的上升沿对齐[6]。B(AC)码的高幅值对应B(DC)码的高电平,B(AC)码的低幅值对应B (DC)码的低电平,如图1所示。

图1 IRIG-B(AC)码格式

2 总体设计

本解码器采用FPGA作为控制核心实现IRIG-B (AC)码的解调。硬件电路主要包括:接收电路、滤波电路、模数转换电路、FPGA控制电路以及输出电路。

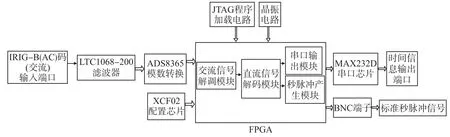

本解码器在解调IRIG-B(AC)码时,首先通过接收电路接收B(AC)码信号,此信号通过滤波电路将噪声滤除掉,模数转换电路将噪声去除后的信号转换为数字信号,FPGA接收到数字信号之后首先对其进行数字解调,FPGA内部对其处理时相乘与其载波同频同相的波形,之后再滤波得到IRIG-B (DC)码,然后根据直流码码元的占空比对码元进行赋值,根据码元的位置与赋值解调出其包涵的时间信息和秒脉冲,通过输出电路送入上位机。系统的整体设计框架如图2所示。

图2 系统硬件结构图

3 系统硬件设计以及器件选型

系统硬件以FPGA为核心,采用模块设计的思路,结构明确,功能强大,主要包含滤波模块和AD转换模块等。FPGA采用XILINX公司的XC3S400,利用LTC1068芯片及外围电路构成低通滤波器,通过ADS8365芯片对采集的交流信号进行模数转换,解码后的时间信息通过MAX232D芯片上传到上位机。

3.1滤波模块

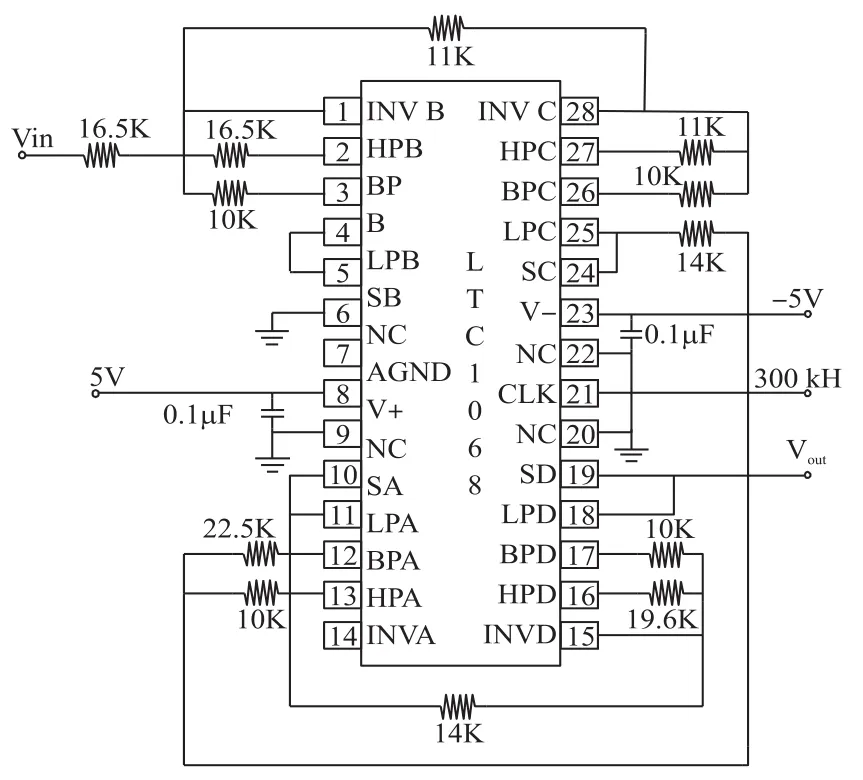

为了确保IRIG-B(AC)码的解码精度,本设计在模数转换模块之前添加滤波电路,根据输入信号的特征,采用的滤波芯片是LTC1068,利用FliterCAD软件生成滤波芯片的外围电路,电路连接图如图3所示。

图3 滤波器外围电路图

本设计中输入的交流信号频率为1 kHz,IRIG-B (AC)码用于远距离传输,在传输过程中易受其它信号的干扰引入噪声,为此,设定低通滤波电路的截止频率为1.5 kHz,阻带衰减为40 dB,有效的去除了噪声。通过使用高精度滤波电路,减小了温漂,提高了信噪比,保证了交流采集电路的精度和可靠性。

3.2AD转换模块

本设计中的模数转换模块采用美国德州仪器的低功耗、高性能ADS8365模数转换芯片,具有6个独立的16 bit并行接口通道,本设计采用直接地址模式,通过控制地址信号端选择采样通道。

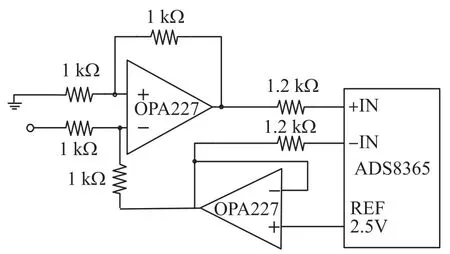

在本设计中,IRIG-B(AC)码的电压范围是±10 V,ADS8365芯片的模拟输入电压范围是0~5 V(以2.5 V为基准),为了使输入信号与ADS8365的输入电压相匹配,在ADS8365前添加闭环调理电路,如图4所示,两片OPA227UA组成差分输出电路,将单端输入信号的电压降低至0~5 V范围内,满足ADS8365对输入信号电压的要求。

图4 双极性输入电压转换电路

4 系统软件设计

交流B码经过硬件电路处理后传输给FPGA,FPGA程序采用模块化设计思路。调用FPGA内部乘法器和IP内核生成滤波器,滤波器对交流B码进行解调,得到模糊直流B码,通过门限检测模块后使其变清晰,再按直流B码对其处理。脉宽检测模块通过对脉冲宽度的判断完成码元的赋值,帧头检测模块完成对B码中秒脉冲的提取,时间序列提取模块通过码元距离帧头的位置按二进制将码元的赋值转换为8421BCD格式的时间信息,通过输出模块传递到上位机。

4.1IRIG-B(AC)码解调

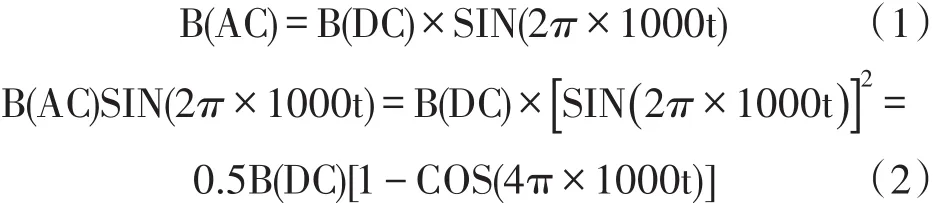

IRIG-B(AC)码是由B(直流)码以1 kHz的正弦波为载波调制成的,对交流码的解调关键是获得其过零点和幅度信息。数学推导过程如下:

式(1)表示IRIG-B(AC)码,式(2)表示AC码与其载波相乘,通过式(2)可以得出,经过乘法器相乘之后,数字信号变为一个由直流分量和交流分量相耦合的信号,再经过数字滤波器滤除掉交流分量,信号就由交流(AC)B码变为直流(DC)B码。

使用SIMULINK软件进行仿真,数字解调的过程如图5所示。

图5 交流B码转换为直流B码的仿真示意图

经过低通滤波器得到直流分量,但是低通滤波器不可能完全将信号中的交流分量去除,因此,需要添加阈值检测模块,将模糊的直流B码还原为精确的直流B码。为了提高检测精度,阈值需要设置为一个动态值,判断每一个码元宽度的阈值需要根据上一个码元的最大值确定,因此将阈值设为上一个码元的2/3,当检测到数字信号大于阈值时,输出为1,反之为0。脉宽检测模块根据阈值检测模块的输出值确定脉冲宽度,根据脉冲宽度判断码元的赋值。

严格来说,从阈值检测模块输出的直流B码不是标准的直流B码,因此对脉冲宽度的判断采用近似比较。设计中采用的晶振为40 MHz,当脉宽计数模块检测到信号上升沿时,计数器开始工作,下降沿时停止工作。计数结果cnt送入寄存器中进行顺序比较,如果cnt大于7 500且小于85 000,该码元为0;如果cnt的值大于195 000且小于205 000,该码元为1;如果cnt的值大于315 000且小于325 000,;该码元为P码。

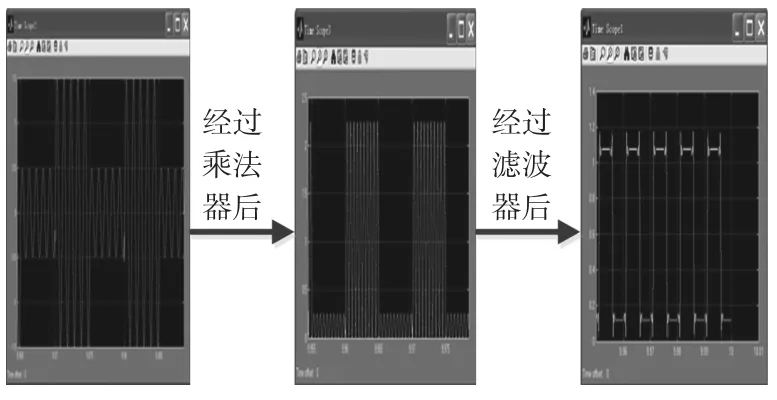

4.2IRIG-B(DC)码解调

FPGA解调B码主要是提取B码中包含的时间信息和秒脉冲。要提取B码的秒脉冲信号,首先要判断B码的帧头[7],通过帧头的判断确定其它码元的位置[8]。当检测到两个标志位相连接后开始计数,当计数到99时,产生一个持续的高电平,将此高电平和下一个码元相与,得到秒脉冲信号。不同帧位码元的赋值表示某刻时间的具体信息,时间信息解调模块按照B码协议将其转换为8421BCD格式,并通过MAX490芯片转换为差分形式输出。

在一秒的中间时刻,时间信息解调完成,在下一秒的秒脉冲上升沿出现时输出,因此需要对时间信息进行加一处理。其解调过程如图6所示。

图6 IRIG-B(DC)码解调流程图

5 试验与分析

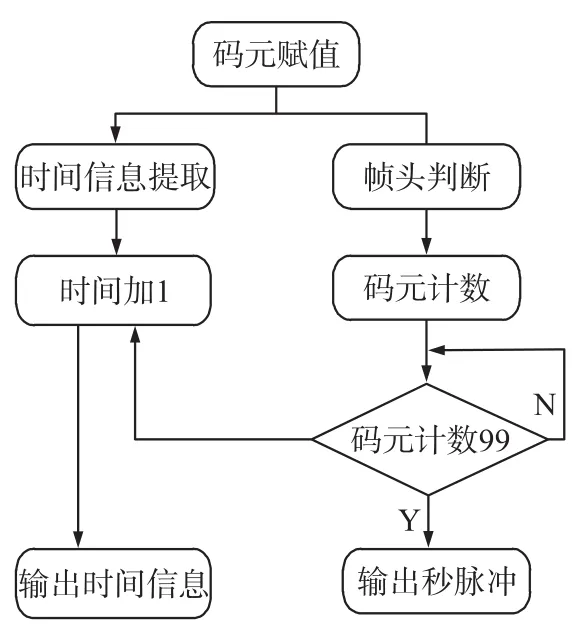

为了验证IRIG-B(AC)解码器的可靠性与可行性,进行了大量的B码解调试验。使用某型号的B码产生器作为B码源,该产生器自带20 m外置天线可以接收GPS与北斗信号,并以此为基准产生IRIGB(AC)码。采用C语言编写的上位机软件,通过RS232串口将时间信息送到上位机,不但可以显示该时刻的时间也可以将信息保存并打印。当前时间是2015年3月6日下午2点16分25秒,对应的显示控件上显示的时间总共是65 d 14 h 16 min 25 s,如图7右侧所示。

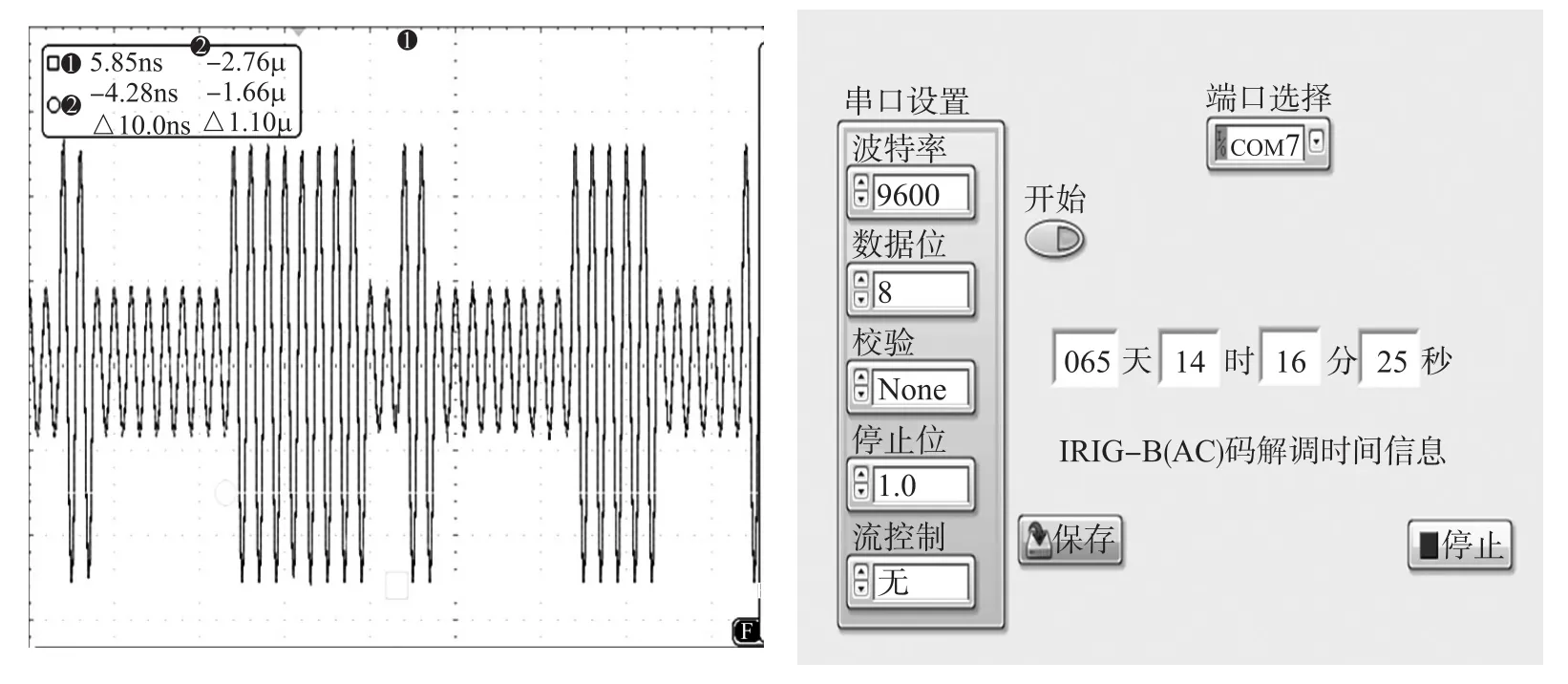

检验授时精度的主要标准是检验授时仪器产生的秒脉冲的上升沿与基准脉冲上升沿的间隔,间隔越小精度越高。解码器通过BNC端口输出秒脉冲,基准脉冲则取自于卫星同步时钟,将两个脉冲同时接入安捷伦的53132A通用计数器的两个输入端测量上升沿的时间间隔,53132A通用计数器的精度可以达到100 ps,完全满足试验要求。检测脉冲的时间间隔如图8所示。

图7 解调时间显示

图8 脉冲的时间间隔测量结果

由图8可见两个秒脉冲的间距为45.432 62 μs,测量结果时取前50个计数结果的值求平均值得出。解码脉冲与基准脉冲相比延迟45.4 μs,控制在50 μs内,满足设计要求。解码的秒脉冲延时是固定的,在FPGA内部程序添加计数模块,使得秒脉冲和下一秒的基准脉冲对齐,可以进一步提高授时精度。

6 结论

本文介绍了采用FPGA芯片实现的IRIG-B (AC)码解码器的设计,通过调用FPGA内部的IP核以及采用模块化设计实现对交流B码的解调功能,可以精确地提取时间信息和秒脉冲信号。解码器结构简单、成本低、功耗小、解码精度高,可以与多种授时仪器协同工作。满足国军标GJB3947A要求,具有广阔的应用前景。

[1]王智平,佟刚,曹永刚,等.FPGA在IRIG-B码源设计中的应用[J].微计算机信息,2009,12(2):167-168.

[2]唐博,李锦明,李士照,等.基于FPGA的高阶FIR滤波器强抗干扰数据采集系统[J].电子技术应用,2009,12(2):89-92.

[3]雒俊鹏.基于FPGA的IRIG-B(DC)码产生电路设计[J].电子设计工程,2012,38(9):146-148.

[4]吴卫,陈建军,宋虎,等.基于FPGA的IRIG-B码解码器的实现[J].雷达与对抗,2009(3):37-40.

[5]熊立智,唐普英.基于FPGA的IRIG-B解码电路设计与实现[J].通信技术,2010,43(8):231-232.

[6]张斌,张东来,王超.基于FPGA的IRIG-B(DC)码同步解码设计[J].测控技术,2008,27(2):45-47.

[7]吴炜,周烨,黄子强.FPGA实现IRIG-B(DC)码编码和解码的设计[J].电子设计工程,2010,18-12:162-164.

[8]李万山,郑海昕.用GPS校时的IRIG-B(DC)时间码产生器设计[J].装备指挥技术学院学报,1999,10(1):93-96.

贾磊(1989-),男,山西吕梁人,硕士研究生,专业:仪器仪表工程,研究方向为电路与系统;

崔永俊(1973-),山西忻州人,博士生,副教授,主要研究方向为纳米测试技术与仪器,704815175@qq.com。

Design of FPGA-Based IR IG-B(AC)Time Code Decoder*

JIA Lei1,2,CUI Yongjun1,2*,YANG Bing1,2,WANG Jinwei1,2

(1.Ministerial Key Laboratory for Instrument Science and Dynamic Test North University of China,Taiyuan 030051,China;2.National Key Laboratory for Electoenic Measurement Technology,North University of China,Taiyuan 030051,China)

In order to solve the IRIG-B(AC)decoding low accuracy problems and improve the stability of the demod⁃ulation system,a high-performance decoder is presented useing FPGA implementation demodulation IRIG-B(AC)codes.By calling the FPGA IP core generation multipliers and FIR low-pass filter,the AC components in the B(AC)code are filtered,then demodulated according to their amplitude.The decoder can demodulate time information of IRIG-B(AC)code accurately,transmit it quickly,and outputs the second pulse which is corresponding with time in⁃formation,through the output port to the demodulated PC display.Through extensive testing the decoder shows its accuracy,stability,and meets the requirements of various applications for IRIG-B(AC)code of timing.

IRIG-B code;decoding;filtering;A/D conversion;the second pulse

TN787

A

1005-9490(2016)02-0370-04

EEACC:6120D10.3969/j.issn.1005-9490.2016.02.025

项目来源:国家自然科学基金项目(61335008)

2015-05-26修改日期:2015-07-03