某型多调制方式低相噪毫米波频率源设计*

2016-10-13陈昌明黄刚

陈昌明,黄刚

(成都信息工程大学通信工程学院,成都610225)

某型多调制方式低相噪毫米波频率源设计*

陈昌明*,黄刚

(成都信息工程大学通信工程学院,成都610225)

介绍了一种低相噪、多调制方式毫米波频率源方案,采用直接数字频率合成(DDS)+锁相环(PLL)技术,通过引入FPGA解决了同时产生多调制编码单元的难题。详细分析了数字调制编码单元,给出了软件控制流程、m序列Modelsim仿真结果以及环路滤波器设计参数。实测结果表明,调制信号中心频率30 GHz,输出功率大于4 dBm,相位噪声优于-100 dBc/Hz@100 kHz。关键词:多调制;直接数字频率合成(DDS);锁相环(PLL);FPGA

虽然4G网络在全球还处于普及期,但是5G网络已经开始布局,2015年4月23日,工信部、发展改革委、科技部共同支持成立IMT-2020(5G)推进组,作为5G推进工作的平台;中国通信业巨头华为将为2018年俄罗斯世界杯足球赛建设5G实验网,其通信速率将达到10 Gbit/s;韩国三星电子在2014年研发出用于5G网络的实验性通信系统,其工作于28 GHz毫米波频段,数据速率为7.5 Gbit/s。毫米波频率源作为现代通信系统核心部件之一[1-4],其性能好坏对整个通信链路起着至关重要的作用,其中频率源调制方式对系统关键指标相位噪声、频率稳定度、数据速率以及频谱纯度等有着重要影响。而目前研制的频率源调制方式较为单一,无法满足4G、5G网络下超高速、大容量以及高速数据率传输等要求。基于此,本文以毫米波通信系统为应用背景,采用DDS+PLL技术,通过引入FPGA,利用其丰富的逻辑单元来解决同时产生多种调制方式编码单元的难题,设计了一种低相噪、可用于毫米波通信系统的多调制方式频率源。

1 系统方案设计

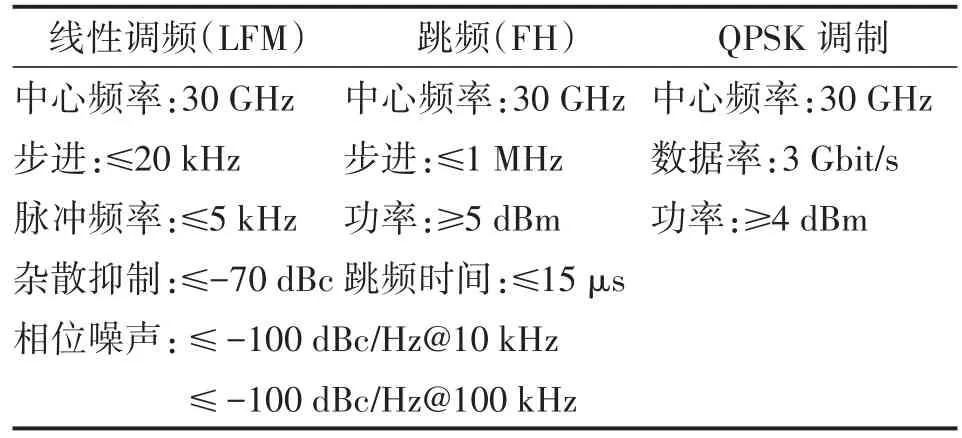

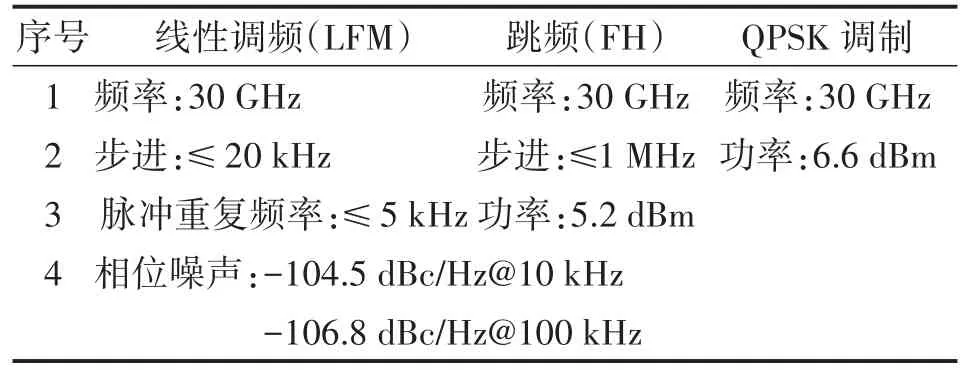

系统主要指标如表1所示。

表1 系统主要指标

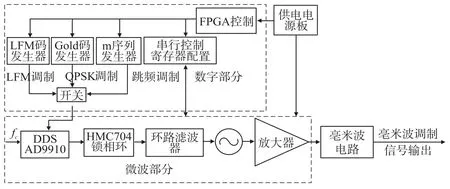

结合毫米波频率源设计指标要求,通过对系统和频率点的精确规划,系统设计方案如图1所示。主要由数字电路,微波电路和毫米波电路3部分组成,其中数字调制编码单元作为系统的核心,包括线性调频(LFM)编码单元,QPSK调制的Gold编码和跳频的m序列发生器。微波电路部分由DDS、PLL、环路滤波器、VCO和放大器组成,毫米波电路包括倍频器、滤波器和放大器等部分。其中FPGA芯片选用Altera公司的Cyclone II EP2C35F672C6,其逻辑单元数为33 216个,DDS芯片选用ADI公司的AD9910,锁相环芯片采用HMC704LP4,毫米波电路选用MMIC,有利于减小系统体积,降低功耗。多调制方式频率源是在单一调制方式基础上改进的一种新型频率合成器,其关键技术是数字调制编码单元,由于其需要实现多种调制方式,在时序设计、逻辑单元以及系统时钟上有特殊要求,因此通过引入FP⁃ GA可以很好的解决这个难题。文中充分利用FP⁃GA功耗低、速度快、逻辑资源丰富等优势,设计了用于LFM调制方式的LFM码发生器、QPSK调制的Gold码发生器和FH调制方式的m序列发生器,然后通过开关选择具体的某一种调制编码控制AD9910输出相应的参考信号。其中LFM方式时DDS输出100 MHz参考信号,QPSK调制方式时输出100 MHz QPSK信号,跳频调制时DDS输出频率为74 MHz~76 MHz,步进10 kHz的跳频信号。参考信号通过PLL实现第一次频谱搬移,输出7.5 GHz信号,与倍频相比有效的降低了系统相位噪声,避免了相噪的恶化,最后微波信号通过毫米波倍频器、微带滤波器和放大器输出毫米波调制信号。

图1 系统设计方案图

1.1数字调制编码单元及软件设计

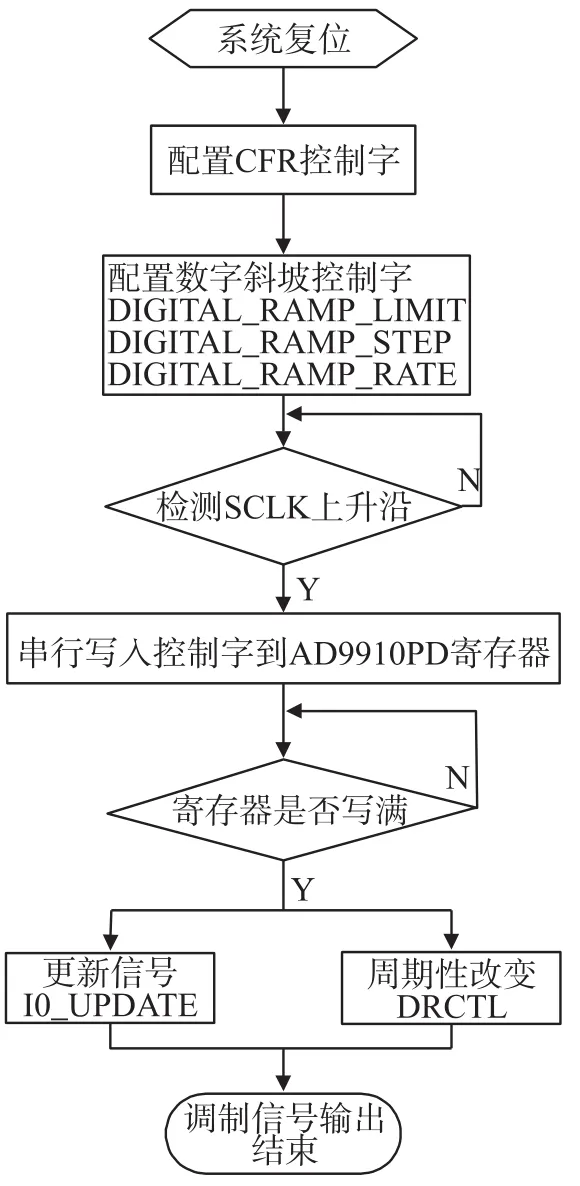

LFM信号需要保证频率具有双向线性扫频功能而信号相位、幅度不发生改变,应当使用数字斜坡(DRG)模式来实现设计。DRG模式下需要FPGA配置的参数包括起始频率、频率步进、斜坡上升/下降斜率以及调谐方向,由两个64 bit寄存器DIGI⁃TAL_RAMP_LIMIT、DIGITAL_RAMP_STEP和一个32 bit寄存器DIGITAL_RAMP_RATE来实现,向相应寄存器写入的十六进制参数值为DIGITAL_ RAMP_LIMIT=64'h2147_AF14_1C28_F533、DIGI⁃TAL_RAMP_STEP=64′h0000_0000_000D_1C71以及DIGITAL_RAMP_RATE=32'h0000_B350,实现了频率步进0.1 MHz和斜坡上升/下降斜率300 μs的LFM信号输出,其软件编码及控制流程如图2所示。DRG模式下实现线性扫频,为保证系统扫频方式更加灵活,可以输出多种调制波形,需要引入No-dwell非驻留斜坡发生器[5-7],用于控制系统扫频方式,它包括两个32位功能寄存器,分别是CFR1和CFR2,其配置的十六进制参数值为CFR1=32′h014C_0420和CFR2=32'h1F3F_C000。当No-dwell不使能时,DRG输出达到编程设定的上限或下限值时,如果工作状态不改变,DRG会一直保持该限值输出;当No-dwell使能时,DRG输出达到上限或下限值时,DRG会立即自动跳到下限或上限值,而不是以斜坡方式返回,这样有利于保证系统输出的LFM信号脉内具有好的线性度。

图2 LFM编码及控制流程

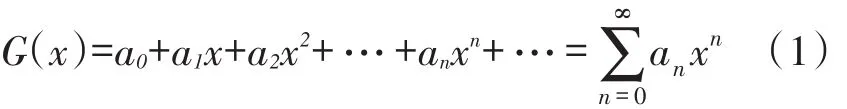

为缓解频谱资源紧张,增强系统安全保密性和可靠性,跳频(FH)和QPSK调制均采用基于m序列的伪码发生器作为其编码核心单元。m序列即最长线性移位寄存器,它由移位寄存器通过线性反馈叠加后形成,具有好的均衡性和伪随机性,能够有效地减小调制后信号产生的载漏,使信号更加隐蔽而不易被截获。m序列多项式为[8-9]

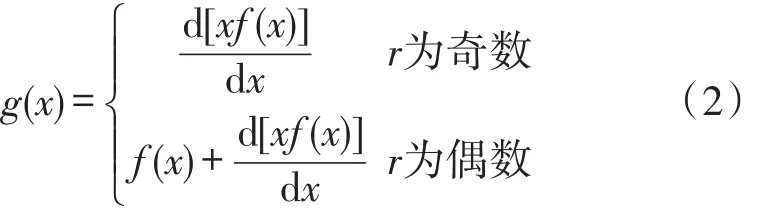

生成函数g(x)表达式为

则生成函数g(x)和序列多项式G(x)的关系为G (x)=g(x)/f(x),其中f(x)为m序列特征多项式,r为移位寄存器级数,由此可以推导出m序列反馈系数。

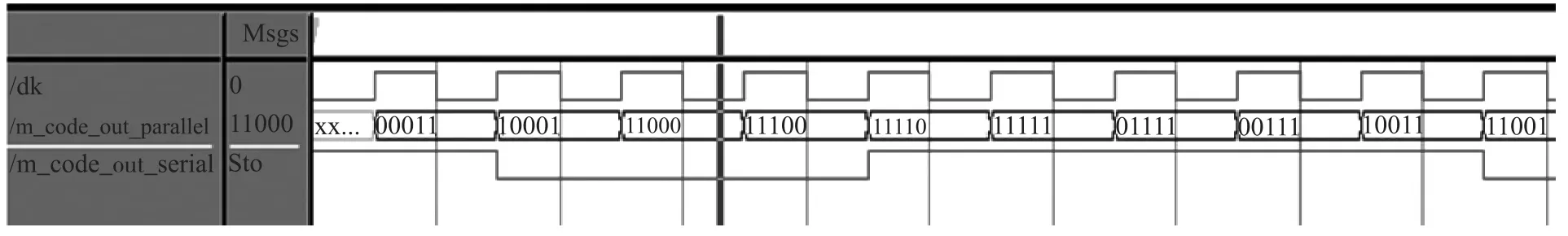

结合系统频点和相位设计要求,伪码发生器采用5级线性移位寄存器实现,其特征多项式f(x)= x5+x2+1,初始值为00011,因此通过5阶线性移位寄存器后m序列输出为100011111001101…。采用Verilog语言编写m序列发生器部分代码如下所示。

always@(posedge clk_in)begin

if(!rst_n)begin

//系统复位,设置初始值为00011

Shift_register<=5'b00011;

end

elsebegin

//移位寄存器实现反馈叠加运算Shift_register[4]<= Shift_register[3]^Shift_register[0];

//线性移位寄存器输并行输出

m_code_out_Parallel<={Shift_register[4],Shift_register [3:0]};

end

//m序列串行输出

assign m_code_out_Serial=Shift_register[0];……

基于Modelsim m序列伪码发生器仿真结果如图3所示,与理论分析完全吻合。

图3 m序列伪码发生器仿真结果

跳频点设计值为74 MHz~76 MHz,步进10 kHz,跳频转换时间8 μs,相应功能寄存器值为Add_Data3_ tmp_0=72′h0E_08B5_0000_0C47_C30D、Add_Da⁃ta3_tmp_1=72′h0F_08B5_0000_0C48_6AD3。QPSK调制时相位跳变为45°、135°、225°315°、90°、270°和180°,信号频率和幅度保持不变,其相应功能寄存器设计参数值为Data3_QPSK_0=72′h0E_08B5_2000_ 1999_999A、Data3_QPSK_1=72′h0F_08B5_6000_ 1999_999A……。

1.2环路滤波器设计

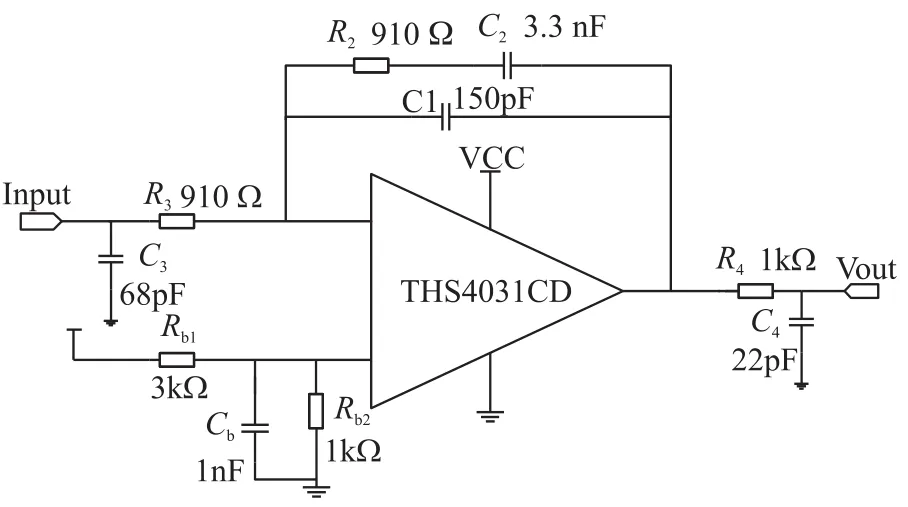

系统设计难点在于3种调制方式共用一个信号通道,其中PLL环路滤波器是设计的关键,对3种调制信号既要兼顾FH调制跳频时间要求又要满足QPSK调制时对数据率以及系统相位噪声要求。综合考虑设计指标,环路滤波器带宽设计为200 kHz,相位裕度59°,这样既能有效滤除了鉴相器本身输出的噪声和载频分量噪声,又能使环路建立起稳定的环路动态特性[10-12]。由于HMC704LP4最大输出电压为5 V,所以需采用有源环路滤波器来实现设计,这里选用低相噪高速运算放大器THS4031CD,其电压噪声为1.6压控振荡器选用HMC507LP5E。四阶有源环路滤波器如图4所示。

2 系统测试结果与分析

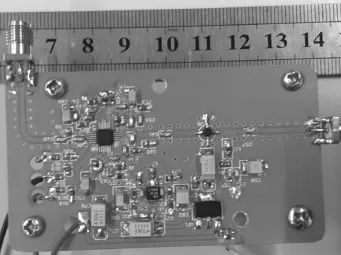

系统微波电路部分采用ROGERS 4350B(介电常数3.66,厚度0.508 mm)板材,为达到较好电磁屏蔽效果,减小相互串扰,采用金属屏蔽盒实现电路间互相隔离。由于屏蔽盒存在谐振效应,容易引起电路部分能量被吸收从而产生衰减尖峰,因此在使用HFSS设计腔体时,应当使其谐振频率远离工作频段。锁相环部分实物如图5所示。

采用Agilent N9030A PXA信号分析仪对系统多调制方式毫米波频率源测试结果如表2所示。

图4 有源环路滤波器

图5 锁相环实物图

表2 系统测试结果

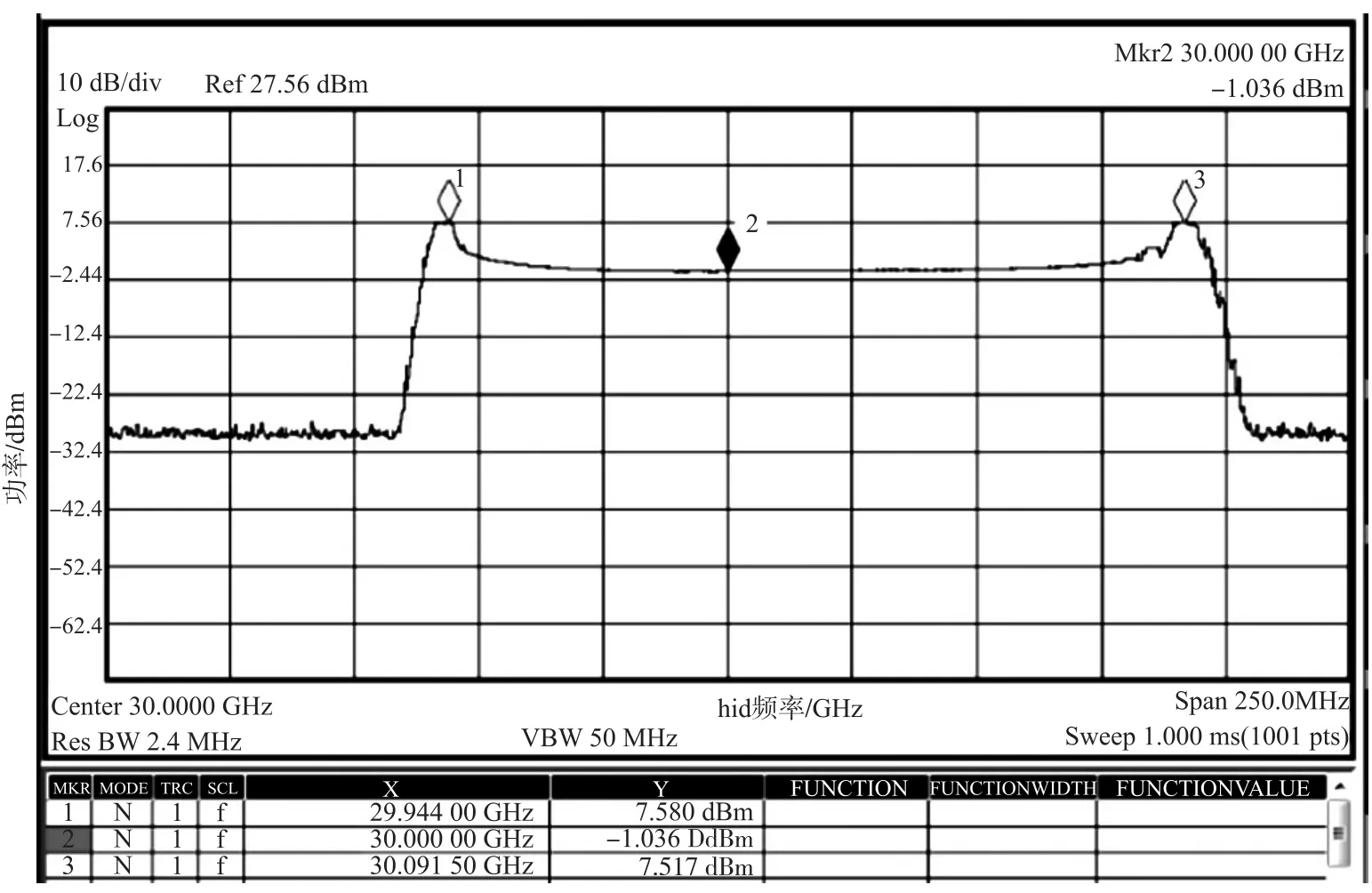

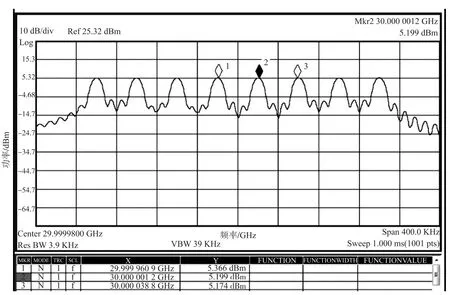

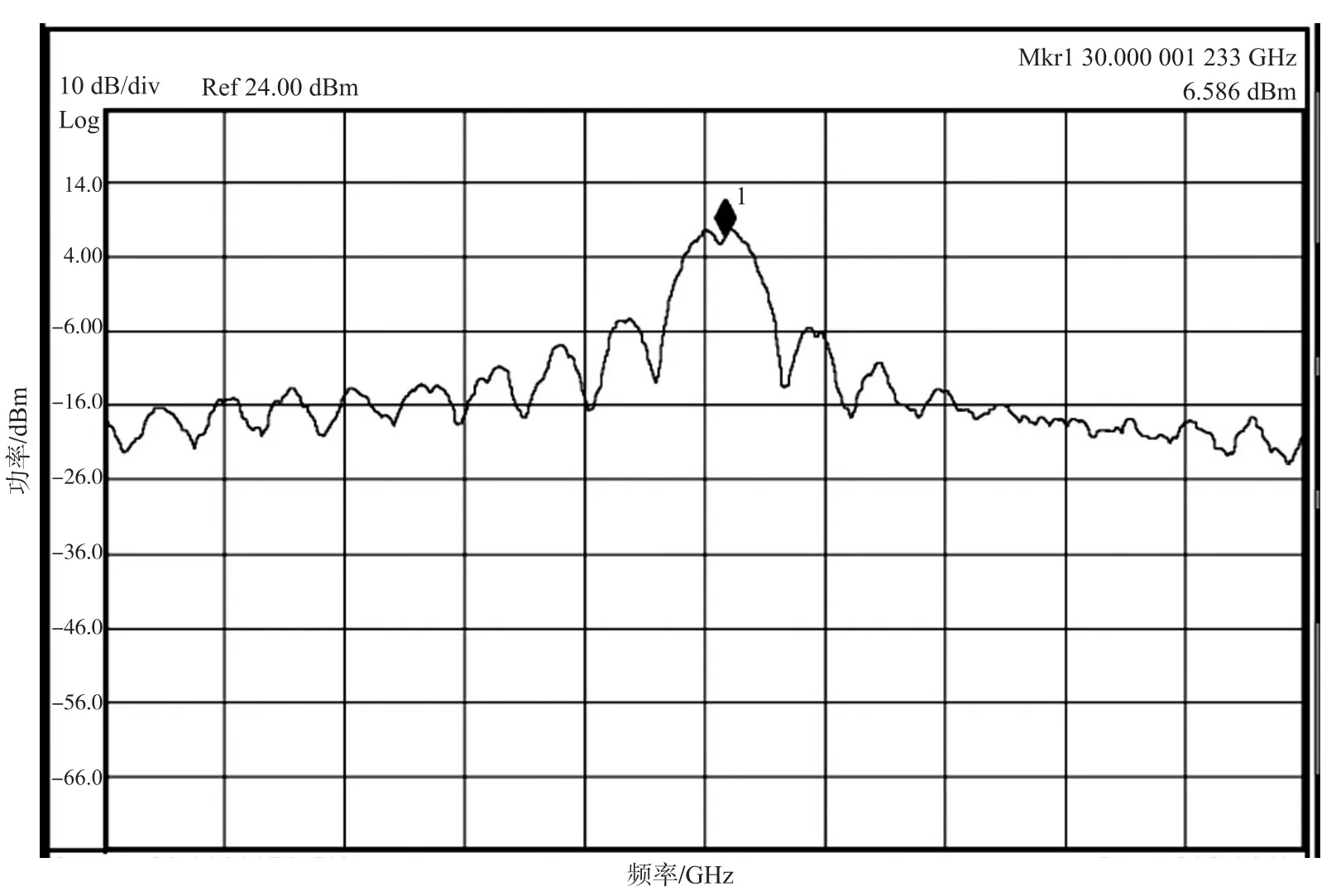

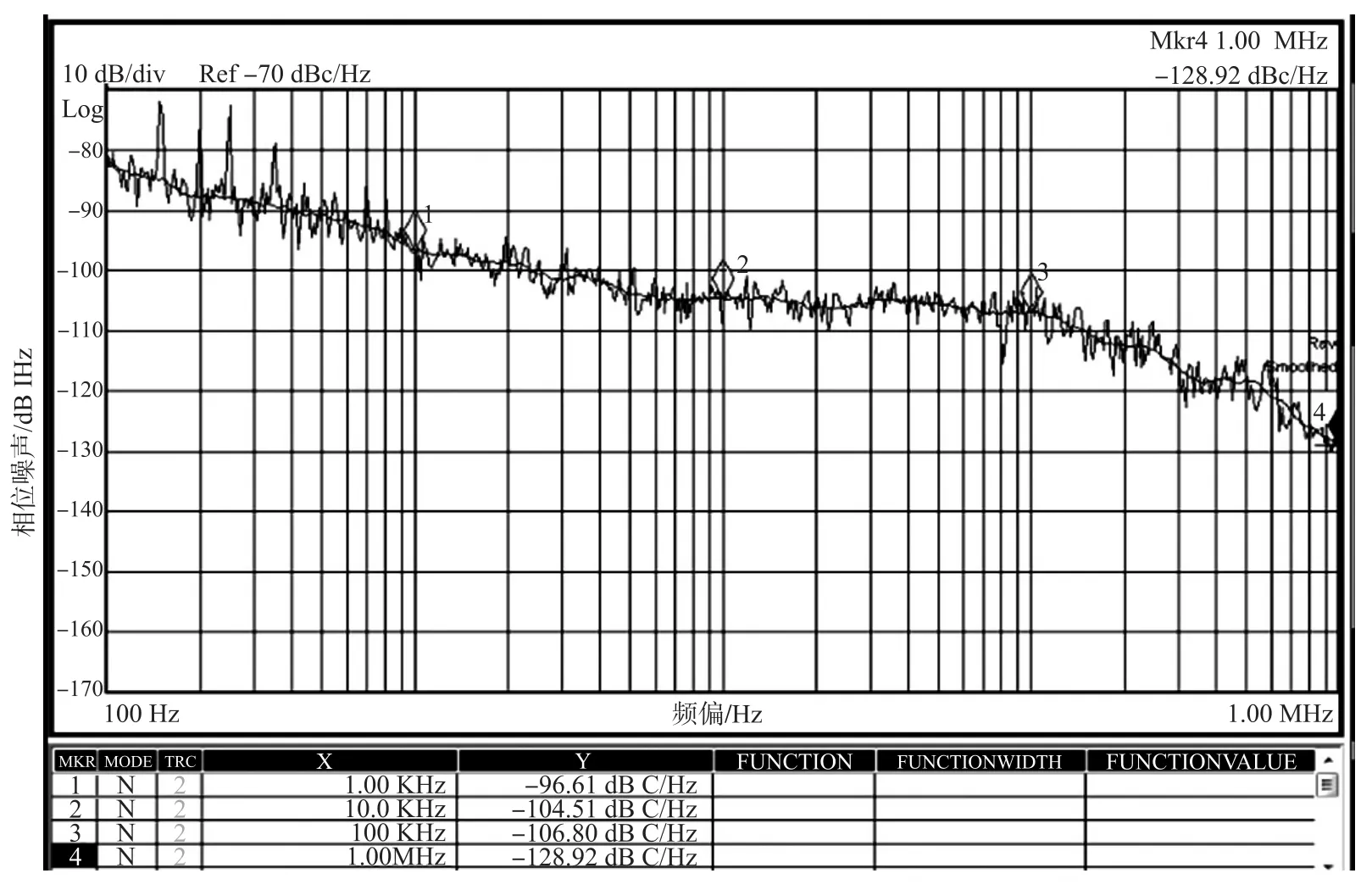

图6~图9分别为LFM、FH和QPSK调制信号测试图及30 GHz载波处相位噪声测试图。实测结果表明,满足设计指标要求,但是存在一定误差,分析主要原因是电源和数字电路干扰以及滤波器加工尺寸误差所引起。

图6 LFM调制信号测试图

图7 FH调制信号测试图

图8 QPSK调制信号测试图

图9 30GHz载波处相位噪声测试图

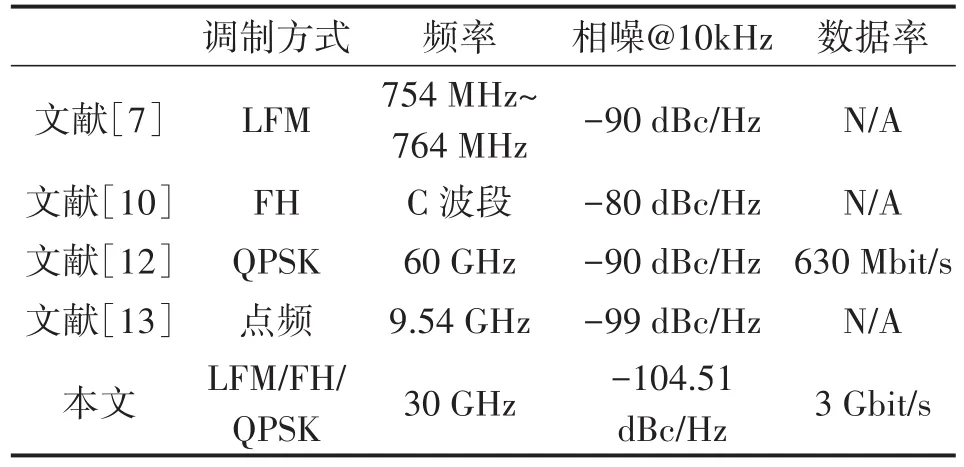

表3中给出了本文研究成果与国内外部分文献指标的对比情况。

表3 本文研究成果与国内外研究指标对比

3 结束语

本文以毫米波通信系统为背景,设计了一种可用于4G、5G网络的多调制、低相噪毫米波频率源,采用DDS+PLL方案,同时兼备了DDS高分辨率、低相位噪声和PLL输出频率高、杂散性能优异等优点。系统中三种调制信号共用一个信号通道有效降低系统成本和调试难度,同时也减小了系统体积,利于小型化和低功耗,对其它频率源设计具有一定实际参考价值。

[1]杨远望,蔡竞业,刘镰斧.毫米波低相噪捷变频高分辨率雷达频率源设计[J].电子技术应用,2011,37(10):56-59.

[2]Sarkhosh N.Carrier Frequency Independent RF Photonic QPSK Modulator[J].IEEE Microwave Theory and Techniques Society,2014,62(2):373-379.

[3]吴刚,罗运生,汪宇,等.X波段低相噪合成频率源设计[J].固体电子学研究与进展,2012,32(3):286-289.

[4]管凝,卢起斌,李正祥.基于ADF4001与MAX2620的宽带锁相频率源设计[J].电子器件,2011,34(4):424-427.

[5]张茂春,刘恺.基于DDS技术的调频连续信号发生器设计[J].制导与引信,2010,31(2):14-18.

[6]王文才,陈昌明,黄刚.PLL驱动DDS的低相噪小步进LFM信号源设计[J].电子器件,2015,38(2):348-351.

[7]黄小东,习友宝.ADF4111在锁相式频率源中的应用[J].电子器件,2012,35(6):751-754.

[8]曾兴雯.扩展频谱通信及其多址技术[M].西安:西安电子科技大学出版社,2005:39-45.

[9]袁慧琴,郭春生.C波段锁相环式本振源设计[J].现代雷达,2008,30(1):84-87.

[10]邓茜,梁小朋.高性价比小型C波段宽带跳频源的研制[J].压电与声光,2011,33(3):432-435.

[11]李兵,李剑平,吴中伟.X波段捷变频频率综合器[J].微波学报,2012(S2):278-280.

[12]Reynolds S K,Floyd B A,Pfeiffer U R,et al.A Silicon 60-GHz Receiver and Transmitter Chipset for Broadband Communications [J].IEEE Solid-State Circuits,2006,41(12):2820-2831.

[13]赵亚妮,陆继炳,杨涛.基于锁相环原理的X波段频率源的设计与实现[J].压电与声光,2012,34(4):636-639.

陈昌明(1971-),男,汉族,四川安县人,教授,主要研究方向为射频、微波/毫米波电路与系统;

黄刚(1989-),男,汉族,四川资阳人,硕士研究生,主要研究方向为射频、微波/毫米波电路与系统,326052253@qq.com。

Design of a Multi-Modulation Millimeter Wave Frequency Source with Low Phase Noise Performance*

CHEN Changming*,HUANG Gang

(College of Communication Engineering,Chengdu University of Information Technology,Chengdu 610225,China)

The method of multi-modulation millimeter wave frequency source with low phase noise performance is introduced.DDS and PLL technology as system design and the problem of multi-modulation was solved by FPGA. The digital modulation coding unit was analyzed.The software control process,m sequence of Modelsim simulation results and loop filter design parameter have been presented.The measured results show that modulation signal fre⁃quency center at 30 GHz,output power greater than 4 dBm and phase noise level is better than-100 dBc/Hz at 100 kHz offset frequency.

multi-modulation;DDS;PLL;FPGA

TN74

A

1005-9490(2016)02-0344-06

EEACC:130010.3969/j.issn.1005-9490.2016.02.020

项目来源:四川省教育厅重点项目(13ZA0087)

2015-05-24修改日期:2015-07-02