基于0.11 μm CMOS工艺的时域SAR模数转换器

2016-10-13李莎

李莎

(西南林业大学计算机与信息学院,昆明650100)

基于0.11 μm CMOS工艺的时域SAR模数转换器

李莎*

(西南林业大学计算机与信息学院,昆明650100)

为避免因多种延迟线之间不匹配造成的线性退化,提出了一种基于时域比较器的逐次逼近型SAR(Successive Approximation Register)模数转换器。通过使用单个延迟线来实现该模转换器的时域比较器,此延迟线包括数控延迟线和压控延迟线。提出的模数转换器具有8个有效位,使用面积为0.128 mm2的0.11 μm CMOS工艺实现。实验结果表明,当工作电源电压低至0.6 V时,提出的时域SAR模数转换器功耗为1.8 μW。

CMOS;模拟数字转换器(ADC);时域比较器;逐次逼近寄存器(SAR)

随着CMOS技术的不断进步与发展,其使用的标称电源电压也随之不断降低,已经接近1.0 V[1]。在电压低的情况下,设计高性能的模拟电路成为一件极具挑战性的事情[2-3]。为了降低设计的困难程度,时域模拟信号处理技术开始获得了广泛关注。例如,使用时域比较器来实现模数转换器ADC(An⁃alog to Digital Converter)的电压比较器。

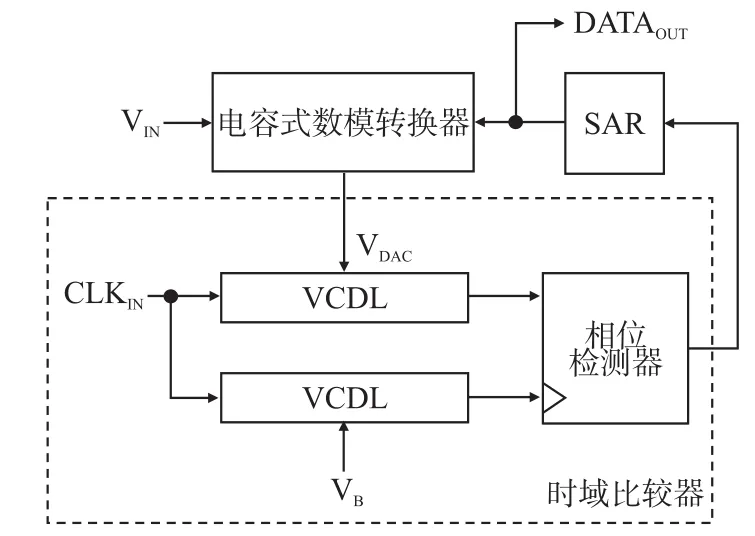

传统的时域比较器将两个模拟电压输入转换成带有两个延迟线的时间延迟,并且对各自输出的到达时间进行比较[4-5]。图1是使用时域比较器的SAR ADC的简化结构。将电容式数模转换器的基准电压VB和输出VDAC分别应用至下压控延迟线和上压控延迟线VCDL(Voltage Controlled Delay Line),完成电压到时间的转换[6-7]。由相位检测器对上下VCDL的延迟进行比较。如果两个VCDL相同,且电压到延迟的特征无变化,相位检测器的输出能够判断VDAC和VB之间哪个较大。如果两个VCDL之间存在不匹配,电压比较会出现误差,且ADC的线性度会退化。

图1 带有两个延迟线的传统SAR型TDADC

本文提出了一种基于时域比较器的逐次逼近型ADC,使用时域比较器来实现电压比较。其时域比较器通过使用唯一延迟线以避免因多个延迟线之间不匹配造成的性能退化的。该ADC可实现较高的分辨率,采样速率为100 ksample/s。当工作电源电压较低仅0.6 V时,提出的时域SAR模数转换器功耗为1.8 μW。

1 提出的时域ADC结构设计

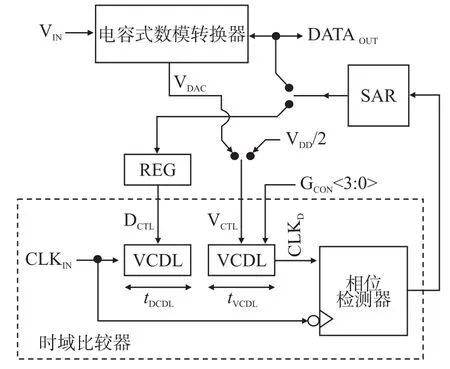

本文提出的时域ADC是以SAR结构为基础,由带有唯一延迟线的时域比较器进行电压比较,如图2所示。延迟线包括数控延迟线DCDL(Digital Controlled Delay Line)和VCDL,两者的延迟分别由数字码DCTL和模拟控制电压VCTL进行控制。最初,对DCDL的延迟tDCDL进行了控制,所以,tDCDL和VCDL延迟tVCDL的总和等于时钟输入CLKIN周期的一半TCLK/2(假设占空比为50%),然而,VCDL的控制电压VCTL固定为VDD/2。由SAR逻辑对DCDL的延迟进行控制,且生成的控制代码DCTL存储在寄存器REG中。

完成初始操作之后,分别将电容式数模转换器的输入和输出与SAR逻辑的输出和VCDL的控制输入VCTL连接用以完成模数转换。在初始操作期间,将tDCDL和tVCDL的总和校准为TCLK/2且VCTL=VDD/2。因此,只有当电容式数模转换器输出VDAC等于VDD/2时,CLKIN的下降沿和CLKD的上升沿才会对齐。然后,基于CLKIN下降沿和CLKD上升沿的到达次数,可确定电容式数模转换器的输出大于还是小于基准位准VDD/2。

图2 本文提出的带唯一延迟线的ADC

VCDL的延迟与控制输入VCTL成反比。因此,如果电容式数模转换器的输出VDAC大于(小于)VDD/2,tDCDL和tVCDL的总和会小于(大于)TCLK/2,且SAR逻辑会使CDAC输出VDAC等于VDD/2。

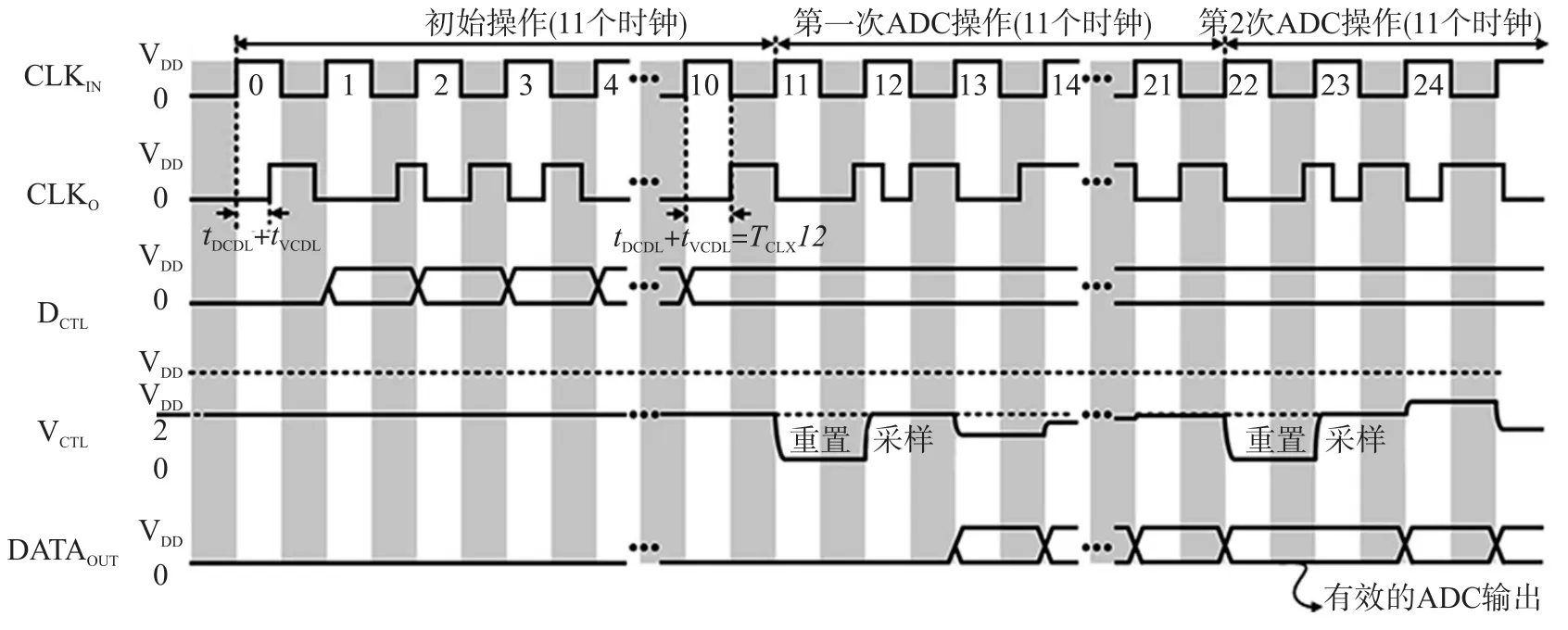

图3是提出的ADC的时序图。当分辨率为9 bit时,初始操作和正常的AD转换均会采用11个时钟周期。因此,22个时钟周期之后就可获得提出的ADC的第1个有效输出。执行一次可确定DCDL延迟的初始操作,然后进行正常的AD转换。如果温度飘移改变了大于1 LSB等值的DCDL 或VCDL延迟,必须再次进行初始操作设置基准延迟。可能需在系统的闲置期内重新进行初始操作,系统使用了本文提出的ADC。可由集成温度传感器对温度飘移进行检测[9-10]。

图3 本文提出的时域ADC的时序图

2 电路实现

2.1延迟线设计

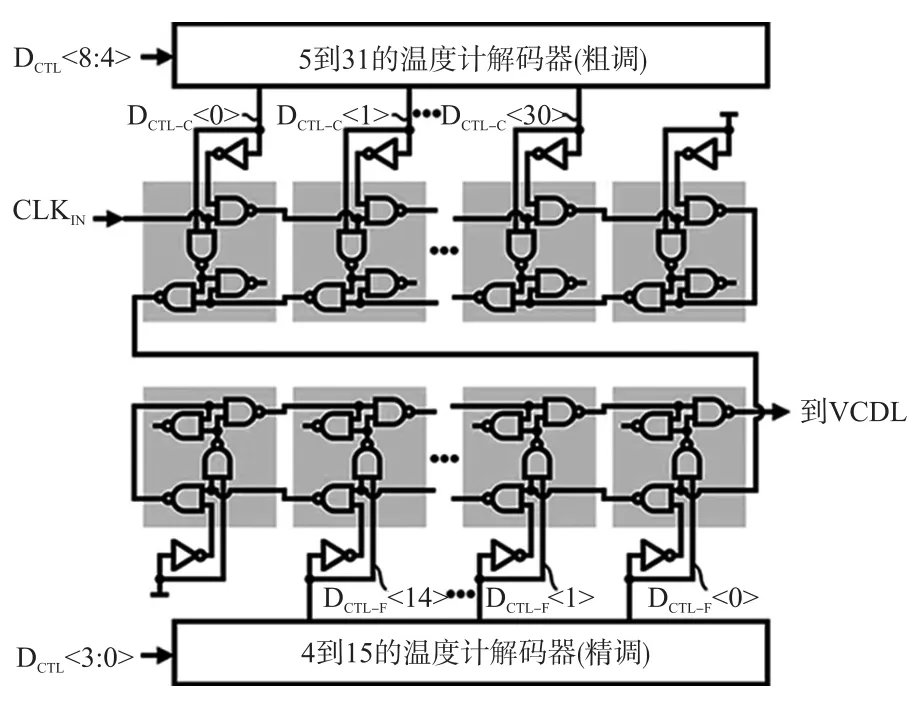

在初始操作结束时,DCDL和VCDL延迟的总和成为时域AD转换的基准延迟[11]。因此,DCDL延迟控制的分辨率必须比等于1的VCDL延迟的分辨率高。图4的DCDL包括粗糙和精细的延迟线,两种延迟线分别包括32个和16个延迟元件。DCDL由9 bit的控制代码DCTL〈8:0〉控制。将9 bit的控制代码DCTL〈8:0〉解码为温度计码DCTL_C〈30:0〉和DCTL_F〈14:0〉以便分别对粗糙和精细的延迟线进行控制。

图4 DCDL结构

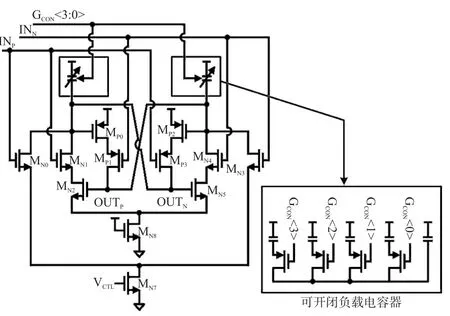

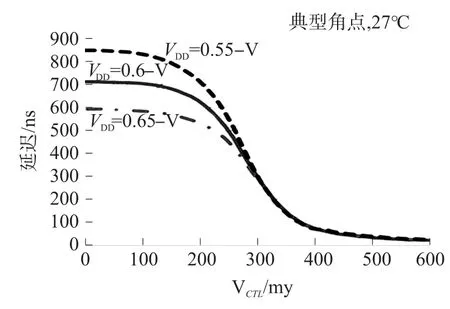

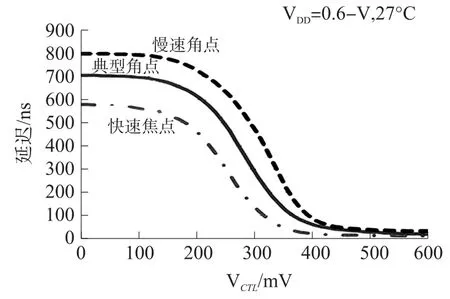

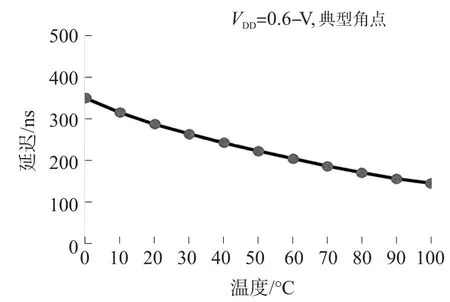

为了使时域比较器的灵敏度最大化,希望VCDL的电压到延迟增益尽可能的大。VCDL使用了如图5(a)所示的晶闸管型延迟单元,众所周知,其具有较大的电压到延迟增益[3]。通过偏置晶体管MN7的电流确定了输入信号路径的强度,并由模拟控制电压VCTL对电流进行控制,然而,通过晶体管MN6的电流确定了正反馈的强度。通过对带有数字代码GCON〈3:0〉的开关负载电容阵列的电容进行控制,可对正反馈的强度及VCDL的延迟特征进行调节。图5(b)和5(c)分别是当GCON〈3:0〉=1000时电源和工艺变化下的晶闸管型延迟单元的模拟延迟与控制电压VCTL。因工艺变化导致延迟产生的巨大变化可通过选择GCON〈3:0〉的不同代码进行补偿。对于典型的工艺拐点、VDD=0.6 V及室温,当控制电压VCTL等于VDD/2时,VCDL与控制电压VCTL的最大灵敏度约为1.7 ns/mV。图5(d)是当VCTL等于VDD/2时的延迟与温度。

当控制电压VCTL接近0 V或VDD时,VCDL的电压到延迟传输特征是非线性的。然而,电压到延迟特征的线性度并非关键。当VCDL的控制电压VCTL约为VDD/2时,重要的是电压到延迟增益。如果电压到延迟特征无变化,且增益足够大以便由1 LSB等效电压导致VCTL产生的变化可能会生成大于相位检测器计时不准的延迟差异,可进行无误的时域比较。

从VCDL和DCDL的模拟延迟特征可看出,如果温度变化超过3℃,必须再进行一次初始操作。可容忍的温度变化比较小,原因在于,当VCTL=VDD/2时,VCDL的偏置晶体管MN7在亚阈值区域中运行。如果实现了由GCON〈3:0〉控制的可开闭负载电容器的电容用以具有正温度系数,可对其进行改进。

图5(a) VCDL晶闸管型延迟单元结构

图5(b) 当电源变化时VCDL晶闸管型延迟单元的延迟情况

图5(c) 当工艺变化时VCDL晶闸管型延迟单元的延迟情况

图5(d) 当GCON〈3∶0〉=1 000时,VCDL晶闸管型延迟单元对应温度的延迟变化情况

2.2相位检测器设计

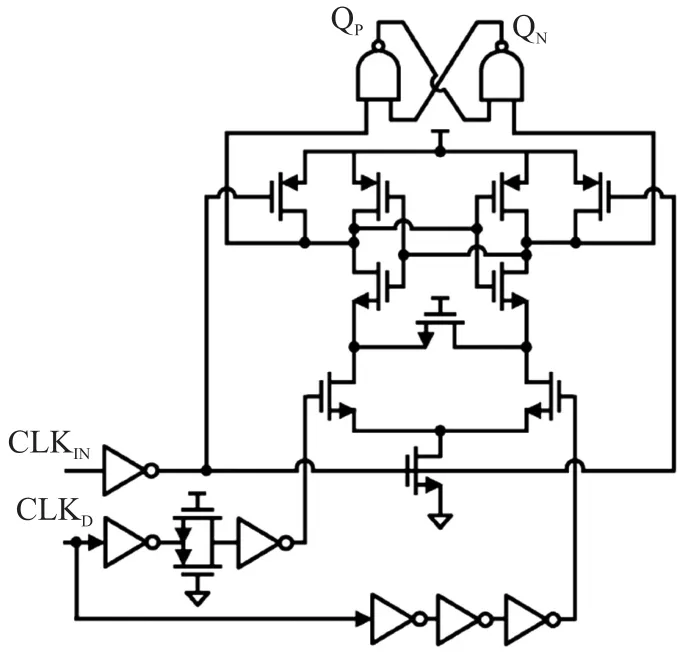

使用检测放大型的触发器实现了相位检测器,如图6所示。将VCDL的输出CLKD转换成微分输出,并通过输入时钟CLKIN的上升沿取样。在所有拐点,相位检测器的模拟设置和保持时间窗口小于80 ps。

图6 相位检测器

2.3电容式数模转换器设计

如图7所示,电容式数模转换器具有二进制加权分裂电容阵列结构。抽取输入式样之前,对全部电容器进行重置,如图7(a)所示。若未进行重置,电容器内的电荷可能会引起记忆效应,因此,抽取输入式样之前,必须将电容器放电。重置阶段之后,抽取模拟输入VIN的式样,且将适当比例的电荷存储在电容器中,如图7(b)所示。电阻低时,取样开关的控制信号会提升至1.2 V。在转换阶段,如图7(c)所示,根据时域比较器和SAR逻辑的输出,将存储的电荷重新分配给每个电容器。

图7

3 实验结果

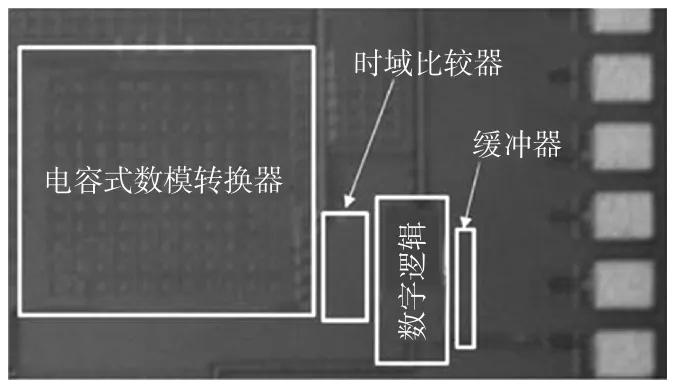

使用0.11 μm CMOS工艺实现了本文提出的时域ADC。图8是芯片的显微照片,面积为0.17 mm2。提出的基于时域比较器的SAR ADC时钟工作频率为1.1 MHz,采样率为100 kS/s且电源为0.6 V时,ADC功耗为1.8 μW。

图8 芯片的显微照片

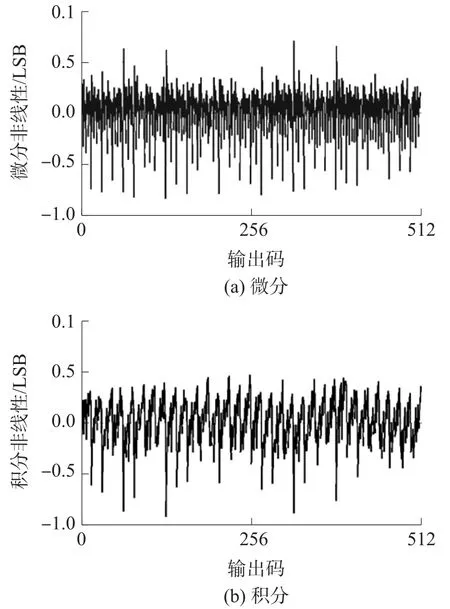

当分辨率为9 bit时,经测量的微分非线性和积分非线性分别是+0.71/-0.84 LSB和+0.47/-0.91 LSB,如图9所示。

图9 提出的经测量的非线性误差

积分非线性是锯齿形,原因在于电容式数模转换器衰减电容器CATT的寄生电容器。当CATT影响了输出VCTL时,CATT会使衰减电容器CATT左边节点上的寄生电容器的效应减弱。然而,CATT右边节点上的寄生电容器的效应会出现在VCTL,且未出现衰减。由于CATT右边节点的连接每隔16个节点就会产生变化,积分非线性和微分非线性也会每隔16个节点产生巨大变化。

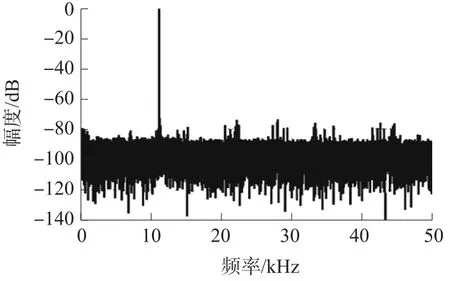

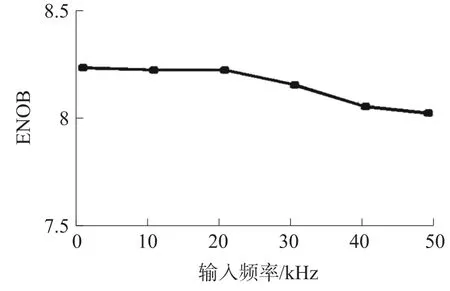

对于11.1 kHz的全额正弦波输入,图10是提出的SAR ADC输出的快速傅里叶变换,有效位数(effective number of bits,ENOB)计算为8.3。对应正弦波输入频率的ENOB变化如图11所示。直到最大输入信号频率为50 kHz,本文提出的ADC的ENOB才会接近8。

图10 11.1 kHz正弦波输入的输出频谱

图11 随着输入频率变化的ENOB结果

表1对本文提出的时域SAR ADC的性能与其它SAR型ADC做出了比较。

表1 与其它SAR型ADC的性能对比

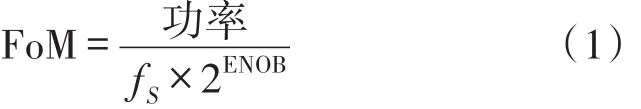

为了公平的比较,品质因数(FoM)可界定为

其中,fS是取样率。本文提出的时域SAR ADC的FoM为65 fJ/转换步骤。[2]中的功率消耗和取样率与本文提出的ADC类似,然而ENOB比文中的ENOB更好,其ENOB更好的原因在于差分输入,在相同的电源电压下,差分输入会使输入动态范围增加一倍。

4 结论

本文提出了一种基于单延迟线时域比较器的SAR ADC,其单一延迟线包括串联DCDL和VCDL,能够避免因延迟线之间不匹配造成的线性度退化。最初,VCDL的控制电压固定为VDD/2,且将DCDL的延迟校准为基准延迟。在正常的AD转换过程中,将反馈DAC的输出应用至VCDL的控制电压,且将DCDL的控制代码固定为初始操作期间发现的代码。通过对延迟线的延迟与基准延迟进行比较,我们可以判断数模转换器输出大于还是小于VDD/2。最后实验测试使用了0.11 μm CMOS工艺的芯片进行了验证,该ADC采样率为100 ksample/s且电源为0.6 V时,功耗为1.8 μW。

[1]Kim G,Kim M K,Chang B S,et al.A Low-Voltage,Low-Power CMOS Delay Element[J].IEEE Journal of Solid-State Circuits,1996,31(7):966-971.

[2]Lee S K,Park S J,Park H J,et al.A 21 fJ/Conversion-Step 100 kS/s 10-bit ADC With a Low-Noise Time-Domain Comparator for Low-Power Sensor Interface[J].IEEE Journal of Solid-State Circuits,2011,46(3):651-659.

[3]Yang R J,Liu S I.A 40-550 MHz Harmonic-Free All-Digital De⁃lay-Locked Loop Using a Variable SAR Algorithm[J].IEEE Jour⁃nal of Solid-State Circuits,2007,42(2):361-373.

[4]李晓娟.折叠内插模数转换器的高精度设计研究与实现[D].西安:西安电子科技大学,2012.

[5]Verma N,Chandrakasan A.An Ultra-Low Energy 12-bit Rate-Resolution Scalable SAR ADC for Wireless Sensor Nodes[J]. IEEE J Solid-State Circuits,2007,42(6):1196-1205.

[6]陈娟,陈鑫.适用于数字锁相环的快速建模方法[J].电子器件,2012,35(5):535-539.

[7]杨思宇.基于差分时域比较器的逐次逼近模数转换器的研究和设计[D].复旦大学,2011.

[8]施琦锋,薛晓博,何乐年.新型数模转换器时域误差校正方法[J].浙江大学学报(工学版),2013,11:2025-2030.

[9]Xu R,Liu B,Yuan J.Digitally Calibrated 768-kS/s 10-b Mini⁃mum-Size SAR ADC Array with Dithering[J].IEEE J Solid-State Circuits,2012 47(9):2129-2140.

[10]Huang G Y,Chang S J,Liu C C,et al.A 1-08W 10-bit 200-kS/s SAR ADC with a Bypass Window for Biomedical Applications[J].IEEE Journal of Solid-State Circuits,2012,47(11):2783-2795.

[11]徐峰,陈杉,李小珍,等.一种基于90 nm工艺的10位电荷再分配型逐次逼近模数转换器IP[J].电子器件,2009,32(3):596-600.

李莎(1987-),女,汉族,籍贯江西进贤,毕业于华中科技大学微电子学专业,硕士研究生,现就职于西南林业大学,助教;主要研究方向为数模混合集成电路,lisha0871@163.com。

Time Domain SAR Analog-to-Digital Conversion Based on 0.11 μm CMOS Process

LI Sha*

(School of Computer and Information Science,Southwest Forestry University,Kunming 650100,China)

In order to avoid the linear degradation caused by multiple delay lines,an approximation register analogto-digital converter based on the time domain comparator is proposed.By using a single delay line to implement the time domain comparator of the mode converter,the delay line includes the numerical control delay line and the volt⁃age controlled delay line.The proposed analog-to-digital converter has 8 effective bits,with the use of an area of 0.11 μm CMOS process to achieve 0.128 mm2.Experimental results show that the power consumption of the time do⁃main SAR ADC is 1.8μWwhen the power supply voltage is 0.6 V.

CMOS;ADC;time domain comparator;SAR

TN69.2

A

1005-9490(2016)02-0285-06

EEACC:1290B10.3969/j.issn.1005-9490.2016.02.010

2015-08-27修改日期:2015-09-25