一种SPI全双工通信方法讨论

2016-10-13王霞

王 霞

一种SPI全双工通信方法讨论

王 霞

深圳市中兴微电子技术有限公司,江苏 南京 210012

使用SPI全双工通信方法,可以有效提高SPI的读写速率,为双处理器连接的项目提供一种高速可靠的总线接口方式。

SPI;全双工;双处理器;通信

引言

SPI总线是一种通用的同步串行外设接口,它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI传输为主从模式,需要Master提供时钟,Slave被动接收或发送。若Slave主动发送数据到Master,需要通知Master以提供时钟发起数据传输过程[1]。

本文描述SPI的全双工通信方式以及数据包格式。

1 系统方案

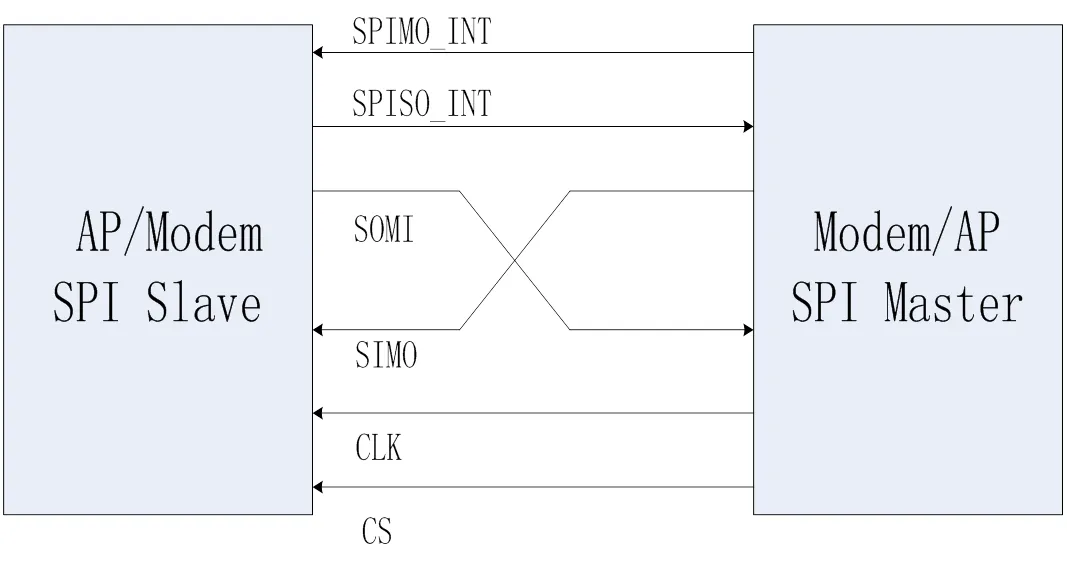

方案采用双线通知模式,SPIMO_INT和SPISO_INT两根通知线。当Master发起数据传输时,通过SPIMO_INT通知Slave。

当Slave发起数据传输时,通过SPISO_INT通知Matser,而后Master发起数据传输。这里Master采用SPIMO_INT输出至Slave,原因为可使Slave不需要对数据包解析,通过检测SPIMO_INT变化来结束传输过程。同时,也可以使Slave在传输出错时,能够识别出下一次传输的起始。Slave采用SPISO_INT输出至Master,主要作用为以此来唤起Master发起数据传输过程。

图1 SPI连接图

2 全双工模式

在Master和Slave发送数据包不等长条件下,Master需要解析Slave发送的数据包头,判断传输过程结束。使用如下方法:

Master传输完一包数据后,若没有超过MAX_TRANS_SIZE,则查看是否有待发数据。若有待发数据,则继续下一包发送。若没有待发数据,则解析从Slave接收数据的包头,查看是否从Slave接收完毕。若接收完毕,则结束传输。若Slave还有待发数据,则Master再增补一段零传输,直到Slave的待发数据发送完毕为止。最后,结束当前传输,将SPIMO_INT拉低。状态流程转换如图 2描述,其中Master是否发起再次传输,可根据调试情况变动,但以累计发送量不超过MAX_TRANS_SIZE为基准。

图2 Master发起全双工流程

2.1 连续包处理

Master:发送完一包数据时,若不超MAX_TRANS_SIZE,可继续进行发送。按照连续包格式发送[2]。

Slave:发送完一包数据时,若不超MAX_TRANS_SIZE,可继续进行发送。若产生FIFO溢出时,放弃传输。由于Slave传输受到Master控制,若使用连续包发送,中间可能会有FIFO溢出的可能,也需要增加判别手段。因此,方案中Slave不使用连续发送方式。

3 数据包格式

由于SPI需要传输变长数据,会存在无效数据,因此,需要规划一种数据包格式,将无效数据过滤掉。当Master和Slave间进行传输时,以此数据包作为单位,对接收数据进行解析。数据的包头信息,用于解析随后传输的数据。

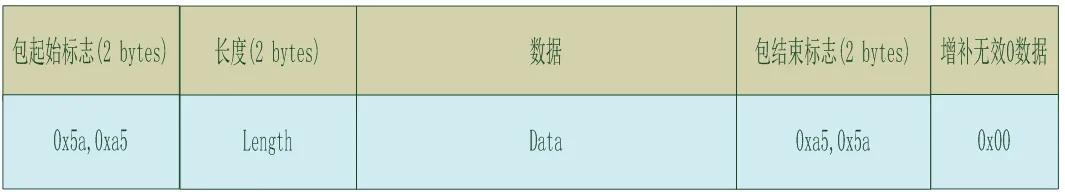

3.1 单数据包

单数据包格式如图3描述:

图3单数据包格式

数据发送方需要按照最小MIN_TRANS_SIZE来发送数据包,不足时需要增补无效的0x00数据。在发送数据时,数据长度以MIN_TRANS_SIZE对齐,不足时补0x00数据。软件在配置SPI FIFO触发门限时,可以配置MIN_TRANS_SIZE。最大传输数据包长度为MAX_TRANS_SIZE,其长度为以上包格式中所有字段的长度和。

1)包起始标志:标示数据包的起始。

2)包长度:数据包数据区的长度,单位byte。

3)数据:数据区,需要传输的数据。

4)包结束标志:标示数据包的结束,可用此标志来判断数据包的合法性。尤其,当Slave FIFO下溢出时,Master用此标志可以确定数据包是否正常传输完毕,以判断数据的正确性[3]。

3.2 连续数据包

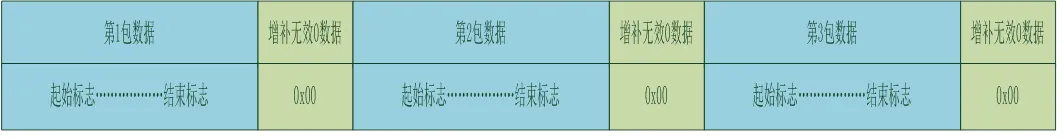

连续数据包格式如图4描述:

图4连续数据包格式

连续包是在一次数据传输过程中完成,接收方需要能够解析数据包。一包数据长度对齐至MIN_TRANS_SIZE,其起始标志作为一包数据的开始,用结束标志判断数据的合法性。解析时,能够过滤掉增补的无效0数据。

方案中,只允许Master使用连续数据包格式进行发送。Slave进行解析时,可参考DMA实际传输长度为解析的最大基准长度。

[1]陈杨,胡伟圣,马陆.应用于Wi-Fi卫星通信系统的验证平台实现[J].信息技术,2016(6):21-26.

[2]魏小景.异步串行通信(UART)在DSP系统中的研究实现[J].科学与财富,2015(2):142.

[3]翟瑞永,张文栋,周兆英,等.SPI串行DataFlash在MEMS姿态测量系统中的应用[J].电子技术应用,2013,39(8):37-39.

A method of SPI full duplex communication

Wang Xia

Shenzhen Zhongxing Microelectronics Technology Co., Ltd., Jiangsu 210012

SPI full duplex communication method can effectively improve the read and write rate of SPI, providing a high-speed and reliable bus interface for the dual processor connected projects.

SPI; full duplex; dual processor; communication

TP368.12

A

1009-6434(2016)12-0053-02