基于FPGA的FIR数字滤波器设计与仿真

2016-10-11杨峰

杨 峰

(四川文理学院国有资产管理处,四川达州635000)

基于FPGA的FIR数字滤波器设计与仿真

杨峰

(四川文理学院国有资产管理处,四川达州635000)

针对微弱信号数字相关检测系统的应用问题,设计了基于FPGA的FIR数字滤波器.通过对不同结构的FIR滤波器的特性进行分析比较,结合运算处理速度和资源消耗等因素,确定采用优化的分布式算法来设计数字滤波器.最后对设计的FIR低通数字滤波器进行了功能仿真,仿真结果显示:设计的FIR低通数字滤波器能够有效滤除带外噪声,能够满足数字信号相关检测系统的应用要求.

数字滤波器;MATLAB;FPGA; 分布式算法

根据数字信号相关检测的原理可知,输入被测信号与参考信号在进行相乘运算之后,再通过数字低通滤波,就可以得到反映被测信号幅值信息的直流信号.[1-2]可见,数字滤波器是数字相关检测中的核心单元.

数字滤波器按照其单位脉冲响应h(k)的长短,可以分为无限长脉冲响应(Infinite Impulse Response, IIR)滤波器和有限长脉冲响应(Finite Impulse Response, FIR)滤波器两种类型.[3-4]FIR数字滤波器比IIR滤波器具有更好的相位线性响应,[5]而且它还具有性能稳定、设计灵活和幅度可调等优点,所以非常适合应用于数字相关检测系统中.

传统的FIR数字滤波器设计方法通常是采用DSP处理器来实现.由于DSP内部是顺序执行结构,这就使得它的运算处理速度受到限制,不适合应用在处理速度要求很高的场合.而FPGA是并行处理结构,它具有运行速度快、开发周期短、可移植性好等优点.本文介绍了基于FPGA的FIR数字滤波器的设计.

1 FIR数字滤波器的基本原理

数字滤波器是一个离散系统,所处理的对象是用序列表示的离散信号或者数字信号.[6]系统函数表达式为:

(1)

从上式可以得出表示输入输出关系的常系数线性差分方程为:

(2)

由上式可以看出:数字滤波器的本质是把输入序列经过一定的运算之后变换成一个新的输出序列.大多数普通的数字滤波器是线性时不变(Linear time-invariant, LTI)滤波器.对于FIR系统来说,其系统函数只有零点(Z=0的极点除外),因此,可以将(2)式化为:

(3)

对于抽头数为N的FIR滤波器的数学表达式为:

(4)

其系统函数为:

(5)

上式中的h(n)为第n级抽头系数,x(n-k)为延时n个抽头的输入信号.可以用方框图来表示FIR滤波器,图1为FIR直接形式的方框图.

图1 FIR滤波器的方框图

2 FIR数字滤波器设计

2.1FIR滤波器的MATLAB设计

FDATool是MATLAB软件中专用于滤波器设计和分析的工具.本文采用Hamming窗函数设计64阶低通滤波器,截止频率为200Hz,图2为设计的滤波器的幅频和相频特性.

图2 滤波器的幅频相频特性

FDATool计算出的滤波器系数为浮点数.用FPGA处理浮点数据非常浪费资源,所以,需要将浮点数形式的滤波器系数量化为整数型.滤波器系数的量化位数越多,滤波器精度就越高.综合考虑频率精度、资源消耗和查找表的输出端口数量等因素,本设计中采用16位对系数进行量化.

2.2基于FPGA的FIR滤波器设计

用FPGA设计FIR数字滤波器时,实现结构有串行算法结构、并行算法结构和分布式算法结构等.串行结构的优点是结构简单、占用资源少,缺点是处理速度慢,适合用于对处理速度要求不高的场合;并行结构相对要比串行结构复杂,若采用流水线结构,[6]能够提高信号的处理速度,缺点是这种结构资源消耗较大.

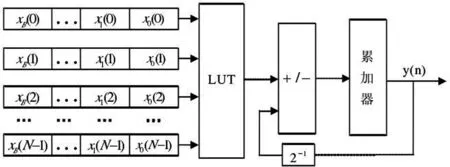

分布式算法结构的核心是ROM查找表(LUT),它将固定系数的乘累加运算转换成查找表操作.[7-8]对于FIR数字滤波器来说,从查找表出来的数据只需执行简单的加法运算,从而可以大大地提高数据的运算处理速度.图3为分布式算法FIR数字滤波器最简单的实现结构.

图3 分布式FIR滤波器的实现结构

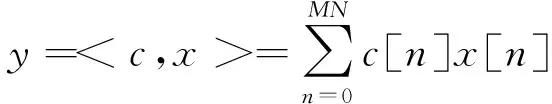

在用上述方法实现分布式算法FIR滤波器时,随着滤波器系数数量的增多,查表的规模会呈指数规律增加.为了减小资源消耗,可以先采用部分表计算,然后再将查表结果相加.设长度为M*N的内积如下式:

(6)

可以将上式中的乘积和分割成M个独立的N阶并行查找表,如下式所示:

(7)

由上面推导可知,若采用部分表运算设计一个8N个系数的FIR数字滤波器,需要7个辅助加法器,而原本需要一个28N×B单元的查找表减少到只需要8个2N×B单元查找表.而且,当数据的分组数量越多时,所需的查找表单元数就越少,也就是单个查找表的规模就越小.但是,随着分组数的增多,需要的辅助加法器数量也随之增多.

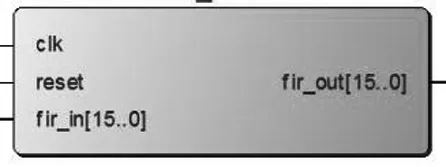

为了不影响运算速度,在用FPGA实现FIR滤波器时,我们采用流水线结构编写Verilog HDL代码.本文采用分布式算法实现64阶数字滤波器,将64输入的查找表分为8个并行的8输入查找表.图4为设计的FIR数字滤波器的RTL视图.

图4 FIR滤波器的RTL视图

3 仿真及结果分析

Verilog HDL代码编写编译完成后,为了验证设计的正确性,使用ModelSim软件对设计的FIR数字低通滤波器进行仿真.仿真的输入信号由DDS频率合成器提供,分别是频率为100Hz和2.5KHz的正弦信号.图5为FIR滤波器的仿真RTL视图.

图5 仿真RTL视图

图6中上面的波形为DDS提供的频率为100Hz和2.5KHz的正弦输入信号,下面的波形为输入信号经过FIR低通滤波器之后的输出信号.由仿真结果可见,FIR的输出信号与输入信号有延时,频率为100Hz的正弦信号完整地保留了下来,而频率为2.5KHz的信号被滤除掉.仿真结果说明了设计的FIR数字低通滤波器能够滤除带外噪声.

图6 FIR低通滤波器仿真结果

4 结论

通过介绍基于FPGA的FIR数字滤波器设计,对不同结构的FIR滤波器进行分析比较,综合考虑到运算处理速度和资源消耗等因素,确定采用优化的分布式算法设计数字滤波器.最后对设计的FIR数字滤波器进行了仿真,仿真结果验证了设计的正确性.

[1] 刘俊,张斌珍.微弱信号检测技术[M]. 北京: 电子工业出版社,2005:51-123.

[2] 赵俊杰,郝育闻,郭璐璐,等.数字锁相放大器的实现研究[J]. 现代电子技术,2012(3):191-195.

[3] Uwe Meyer-Baese.数字信号处理的FPGA实现:第2版[M]. 刘凌,译. 北京: 清华大学出版社,2006:66-119.

[4] 田耘.无线通信FPGA设计[M].北京:电子工业出版社,2007:141-201.

[5] 王秀敏,汪毓铎,张洋,等. 通信系统中FIR数字滤波器的设计研究[J].通信技术,2009(9):3-6.

[6] Vinay K. Ingle,John G. Proakis. 数字信号处理[M]. 刘树棠,译. 陕西:西安交通大学出版社,2013:57-62.

[7] Ali Al-Haj.ConfigurableMultirateFilterbanks[J]. American Journal of Applied Sciences, 2008(7):788-797.

[8] Amita Nandal, T.Vigneswarn,AshwaniK.Rana,etal.AnEfficient256-TapParallelFIRDigitalFilterImplementationUsingDistributedArithmeticArchitecture[J]. Procedia Computer Science, 2015(54): 605-611.

[责任编辑范藻]

The Design and Simulation of FIR Digital Filter

YANG Feng

(National Asset Management Office of Sichuan University of Arts and Sciences, Dazhou Sichuan 653000,China)

FIR digital filter based on FPGA is designed for the application of the weak signal digital correlation detection system. The design adopts the optimized distributed algorithm after comparing the characteristics of different structure of FIR filter and considering such factors as the comprehensive processing speed and resource consumption. Finally, the functional simulation is carried out for the designed FIR low-pass digital filter. Simulation results show that the FIR low-pass digital filter can effectively filter out noise outside of the passband, and it is satisfied with application requirement of the weak signal digital correlation detection system.

Digital filter; MATLAB; FPGA; Distributed Algorithm

2016-01-20

四川文理学院2014年度青年启动项目“GMR生物传感器专用数字锁相检测电路设计”(2014Z006Q)

杨峰(1986— ),男,四川通江人.硕士,主要从事仪器科学与技术研究.

TN911

A

1674-5248(2016)05-0033-03