1.2MV·A混合钳位五电平变流模块的结构布局优化和叠层母排设计

2016-10-11董玉斐罗皓泽杨贺雅何原明李武华何湘宁

董玉斐 罗皓泽 杨贺雅 何原明 李武华 何湘宁

(浙江大学电气工程学院 杭州 310027)

1.2MV·A混合钳位五电平变流模块的结构布局优化和叠层母排设计

董玉斐 罗皓泽 杨贺雅 何原明 李武华 何湘宁

(浙江大学电气工程学院 杭州 310027)

多电平技术是高压大功率变流器的主要解决方案之一,由于电容电压平衡及母排设计等技术问题的限制,三电平以上的二极管钳位型NPC多电平系统在工业中应用较少。为了促进具有电容电压自平衡能力的混合钳位五电平拓扑的大功率工业应用,针对混合钳位五电平电路三相1.2MV·A应用要求,进行了单相变流模块的结构布局和叠层母排设计。首先研究了该拓扑冲击电流产生的根本原因及抑制方法,提出冲击电流抑制对于结构布局的要求;其次,结合冲击电流抑制及NPC四电平电路对称性特点,对混合钳位五电平拓扑大功率应用的结构布局方式进行了工程设计;最后,在该布局方式下结合NPC四电平拓扑的换流特点,通过Ansoft Q3D软件进行了叠层母排的连接设计。最终研制出单相400kW变流模块,测试结果表明其符合设计要求。

大功率变流模块 混合钳位五电平 结构设计 叠层母排

0 引言

多电平技术是高压大功率变流器的最主要解决方案之一[1-4]。其不仅解决了变流器输出电压高与功率半导体器件耐压低之间的矛盾,并且提高了变流器的等效开关频率,降低了输出电压THD,减小了输出滤波器的成本及体积;相对于同等电压等级下的两电平变流器,多电平变流器的dv/dt大大减小,可以有效地防止电机转子绕组绝缘击穿,改善了装置的电磁干扰特性。

二极管钳位多电平和级联型多电平是目前中压传动领域应用最为广泛的两类多电平拓扑。因为电容电压平衡问题,二极管钳位型应用多为三电平拓扑,输出电压等级一般为 4.16kV及以下[5,6]。而级联型多电平电路需要多个独立的直流电源,增加了系统体积及复杂度,并限制了其在背靠背系统中的应用[7]。文献[8]提出的混合钳位五电平拓扑解决了二极管钳位多电平电路的电容电压平衡问题,提高了电压输出等级,便于四象限运行。文献[9-11]分别对该混合钳位五电平的调制方式、整流应用及冲击电流抑制方法进行了研究。该拓扑在小功率样机实现效果良好,但若推广到大功率应用则面临诸多挑战。因为对混合钳位五电平拓扑的结构布局和母排设计而言,其不仅要减小电路中的杂散电感及解决高频电流电容组内的分布不均问题[12],而且要兼顾该拓扑的冲击电流抑制。高频电流分布不均、冲击电流以及杂散电感导致的电压过冲均严重威胁变流器的安全稳定运行[13]。鉴于本拓扑为多电平电路,参与换流过程的功率器件数目较多,结构布局对于母排设计结果更有重要影响,因此如何优化变流模块结构布局和母排设计,同时确保冲击电流的有效抑制是该拓扑在大功率应用中的核心技术。

本文从混合钳位五电平电路冲击电流产生的机制入手,分析了不同结构布局下电感元件对于变流器性能的影响,确定一种便于冲击电流抑制及母排设计的结构布局方式。进而根据该结构布局的特点,重点对其中的 NPC四电平拓扑的叠层母排进行了优化设计。最终研制出单相400kV·A混合钳位五电平变流模块,且实验表明设计结果良好。

1 混合钳位五电平工作原理分析及变流模块参数设计

1.1混合钳位五电平拓扑的工作原理

图1为混合钳位五电平单相拓扑。与传统二极管钳位五电平拓扑相比,靠近母线电容Cd1~Cd4的6个钳位二极管由钳位开关管 Sc1~Sc6代替,在相邻的两个钳位开关管Sc1和Sc2、Sc3和Sc4、Sc5和Sc6两端并联钳位电容 Cc1~Cc3,以实现电压钳位及电容电压自平衡。图中 Sa1~Sa8为主开关管,用以实现期望的电压输出。

电容电压自平衡功能是通过钳位开关管 Sc1~Sc6和钳位电容 Cc1~Cc3实现的。根据文献[7]中的开关规则,Sa1导通时,Sc2、Sc4和Sc6同时导通,则钳位电容Cc1~Cc3分别与母线电容Cd1~Cd3并联,故有 UCd1=UCc1、UCd2=UCc2及 UCd3=UCc3;当 Sa1关断时,Sc1、Sc3和Sc5同时导通,此时钳位电容Cc1~Cc3分别与母线电容Cd2~Cd4并联,因此UCd2=UCc1、UCd3=UCc2及UCd4=UCc3, 由 此 可 得UCd1= UCd2=UCd3=UCd4。因此对于该拓扑只要保证每个开关周期内 Sa1开关一次即可实现直流母线侧电容的电压平衡,电压自平衡原理如图2所示。

图1 混合钳位五电平单相拓扑Fig.1 Hybrid clamped 5-level topology (one phase)

图2 电压自平衡原理示意图Fig.2 Self-balance mechanism of DC voltage

1.2变流模块的参数设计

对于三相混合钳位五电平而言,除直流母线电容三相共用之外,每一相桥臂其他元器件均为各相独立且易于模块化设计。因此三相1.2MV⋅A混合钳位五电平变流模块的关键在于单相400kV⋅A变流模块的设计,该单相变流模块的参数见表1。

表1 单相变流模块的相关参数Tab.1 Parameters of one phase converter module

2 结构布局对变流器性能的影响分析

2.1冲击电流产生原因

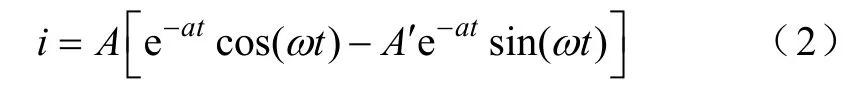

混合钳位五电平拓扑的电容电压平衡通过母线电容与钳位电容并联实现。虽然理论上通过电容并联必然可以实现电压平衡,但两个电压不相等的电容并联必然产生电流冲击,并且输出功率越大冲击电流越大。因此对于大功率应用而言,冲击电流的产生原因及影响必须进行分析。图3表示任意一个开关状态中一对并联电容的等效电路,为了方便理解,以Cd1与Cc1的并联情况为例进行分析。其中功率器件等效为理想元件,Lr与Rr为并联电路中等效的电感与电阻,v1、v2、v3和 v4分别代表母线电容电压、电阻电压、电感电压和钳位电容电压,i为电路中的冲击电流,则根据基尔霍夫电压、电流定律得

图3 并联电容等效电路Fig.3 Equivalent circuit of parallel capacitors

该电路模态初始时刻各元件的状态为求解微分方程的初始条件,则求解微分方程可得

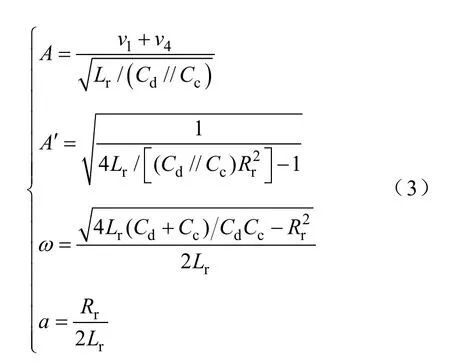

式中,参数A、A′、a和ω 分别为

高频大幅值的冲击电流不仅易导致钳位 IGBT模块的过电压和过电流,而且易引起电容组的发热不均、等效容值降低等问题,降低变流模块的可靠性。因此400kV·A变流模块的结构布局设计必须能够对冲击电流进行抑制,并且最大程度减小冲击电流对变流模块的影响。

2.2结构布局对变流模块性能的影响分析

根据上节的分析,为了减小本拓扑电压平衡过程中引起的冲击电流,需在该电路拓扑中引入较大的电感。然而对于电力电子电路而言,应该尽量减小换流回路中的杂散电感,以降低功率器件的关断电压过冲。

图4为加入缓冲电感的混合钳位五电平电路,其中+2、+1、0、-1、-2代表五个电平输出,每个电平幅值为 Vdc,Ls1代表加在钳位电容 Cc1~Cc3与钳位IGBT Sc1~Sc6之间的4个缓冲电感,s1L′代表加在母线电容Cd1~Cd4与钳位IGBT之间的3个缓冲电感。为了限制冲击电流,缓冲电感可以只加在Ls1位置或只加在s1L′位置或 Ls1及s1L′均加入缓冲电感。当变流器向外输出电流电平由+2向+1跳变时,换流回路如图中点划线框所示,不论缓冲电感处于Ls1还是s1L′所示位置,其均处于换流回路中,换流电流导致电感上产生感应电压ΔV=Lsdi/dt,因此Sa1的关断电压为 Vdc+ΔV。从而引起 Sa1过电压,故该种结构布局方式不适合实际的大功率应用。

图4 加入缓冲电感的原始布局换流示意图Fig.4 Commutation mechanism after utilizing buffer inductance in the original lay out

通过上述的讨论可知,缓冲电感处于换流回路中是引起部分器件产生过电压,变流模块可靠性降低的根本原因。通过调整功率器件的位置,结合缓冲电感的合理布局可以实现缓冲电感不在换流回路中的目标,如图5所示。新的结构布局把图4中所示的Sa1与Sa8移至钳位IGBT侧,缓冲电感在钳位IGBT与钳位电容之间。在该结构布局下,该拓扑可等效为电容电压自平衡电路和 NPC四电平电路的组合。NPC四电平电路负责电平输出产生,其器件动作规律与传统四电平相同。而电容电压自平衡电路负责电容电压自平衡,其桥臂钳位 IGBT任意相邻的两个互补工作。根据文献[11]可知,该拓扑在任意两个相邻模态转换过程中只有一对互补的开关器件动作,存在电容电压自平衡电路内的器件互补动作NPC四电平电路状态不变,或者NPC四电平内器件互补动作电容电压自平衡电路状态不变两种情况。因此每一次模态转换对应的换流回路只包含在电容电压自平衡电路内部或 NPC四电平电路内部,其各自的换流回路不包含缓冲电感Ls1~Ls4,因此换流回路中杂散电感引起的电压过冲只取决于电容电压自平衡电路与 NPC四电平电路的母排设计情况,而与缓冲电感 Ls1~Ls4的大小无关。综上所述,图5所示的结构布局方便加入缓冲电感进行冲击电流抑制,同时缓冲电感不会引起元器件的电压过冲,适合大功率应用。

图5 适合大功率应用的结构布局Fig.5 Layout designed for high power application

2.3高频电流的工程抑制方法

对于混合钳位五电平而言,高频电流包括换流过程产生的电流和冲击电流两部分。高频电流不仅易造成功率器件过压而且易造成电容组发热不均,降低电容的寿命,另外大的冲击电流容易造成功率器件过电流损坏。对于高频电流造成的电容组发热不均,首先对于电容之间的连接采用母排设计,减小电容之间寄生电感,减小高频电流在电容组之间的不均衡程度。其次在电容组靠近功率器件一侧加装吸收电容,减小流经电容组的高频电流总量,如图5所示。为了抑制冲击电流,缓冲元件采用纯电感抑制。为了减小电感体积及其EMI干扰,缓冲电感采用铁心电感。

3 叠层母排工程化设计

叠层母排设计可以有效地减小回路的杂散电感,是大功率变流模块设计的关键。对于混合钳位五电平变流模块而言,母排设计包括电容电压自平衡电路母排设计和 NPC四电平电路母排设计两部分。电容电压自平衡电路的换流回路与两电平类似,其结构布局及母排设计可参照两电平母排设计[14]。下面重点介绍NPC四电平的叠层母排设计。

3.1NPC四电平电路的换流特性分析

由文献[15]可知:对于NPC四电平而言,其电路模态共有四种。图6中+2~−1代表NPC输出的四个电平,每种电平对应一个电路模态,①~⑩代表功率器件之间的连接铜排,定义图中变流器向外输出电流的方向为电流正方向。对NPC电路而言,同一个电路模态,其输出电流方向正负不同时,电流通过的路径不同。例如图6中虚线所示为电路模态为0电平时两种电流输出路径。据此可知NPC四电平共有6个不同的换流回路,12种不同的换流模态。每种换流模态所对应的器件动作情况及高频电流所流经的换流回路见表2。

图6 NPC四电平拓扑Fig.6 NPC 4-level topology

表2 NPC四电平的换流特性Tab.2 Commutation characteristics of NPC 4-level

(续)

3.2NPC四电平功率器件的布局设计

根据表2中各换流回路流经的功率器件及铜排,并对照图6可知换流回路Ⅰ与换流回路Ⅵ关于铜排⑦对称,换流回路Ⅱ与换流回路Ⅴ及换流回路Ⅲ与换流回路Ⅳ亦关于铜排⑦对称。进一步观察可以发现功率器件Sa1与Sa6、Sa2与Sa5及Sa3与Sa4也关于铜排⑦所在的轴线对称,因此四电平拓扑进行布局设计时功率半导体器件按照电路连线⑦的对称形式摆放。对称的器件布局有利于简化多电平的母排设计,便于母排走线,最终NPC四电平的器件布局如图7所示。

图7 NPC四电平的结构布局Fig.7 Placement of power devices in NPC 4-level

3.3叠层母排的连接设计

连接设计与母排能否良好叠层直接相关,而通过母排设计使每个换流回路均实现良好叠层是有效减小其杂散电感的关键[16]。对于两电平拓扑,器件少母排连线简单,两层铜排即可实现拓扑的连接以及各换流回路的有效叠层。多电平拓扑器件较多,铜排走线复杂,很难仅以两层铜排实现所有回路连接的同时保证各换流回路均有效叠层。故多电平一般采用多层母排连接[17,18],本拓扑采用四层母排连接。由表2可知,换流回路Ⅱ~Ⅴ均包含铜排⑦,因此对于Ⅱ~Ⅴ四个回路而言,电路连线⑦可作为公共的母线铜排,即对于以上4个换流回路均可以通过将铜排⑦单独作为一层,将换流回路内除⑦外的其他铜排置于其他层,来实现换流回路的良好叠层。故连线⑦的铜排基本覆盖整个变流模块,且位于相对中间位置的第三层,如图8b所示。对于铜排①⑥、②⑤、③④其分别关于铜排⑦轴线中心对称,因此其布局如图8d和图8a所示,与铜排⑦处于不同层,并关于铜排⑦轴线中心对称。铜排⑧⑨⑩在上述铜排连接方式确定的前提下,根据器件的布局情况,连接情况如图8a、图8c和图8d所示。

图8 NPC四电平叠层母排三维结构Fig.8 Four-level NPC lamination structure

最终NPC四电平模块的设计结果如图9所示,混合钳位五电平变流模块设计结果如图10所示。

图9 NPC四电平样机Fig.9 Prototype of NPC 4-level

图10 混合钳位五电平样机Fig.10 Prototype of hybrid clamped 5-level

4 仿真及实验结果

因为NPC四电平功率器件多、换流路径复杂。因此首先通过对变流器的双脉冲测试[19]验证其结构及母排设计的性能。

变流器的双脉冲测试实验中每个母线电容的电压为400V,负载电感为1.5mH,负载电流为100A。功率器件Sa3的关断电压、电流波形如图11所示,其关断电压过冲为Vov=180V,对应的电流下降时间为T=250ns,则Sa3关断所在的电流回路Ⅲ寄生电感Lr计算式为

根据式(4)及NPC四电平模块中其他功率器件的关断电压波形,可以计算得到NPC其他换流回路的寄生电感,见表3。由表3可知:除Ⅵ回路测试值偏大之外,其他回路的仿真与实验结果基本一致,但测试值均大于仿真值。其原因在于测得的回路杂散电感包括:母排的杂散电感、IGBT及二极管模块内的电感及连接处的电感三部分。在通过仿真计算回路总电感时,母排电感由Ansoft软件仿真得到,功率模块内的电感参考器件手册,连接处电感取为经验值。因该母排安装点较多且缺少安装经验,故连接处的实际电感偏大,而且测量值相对计算值偏大,Ⅵ回路误差偏大主要因为安装接触面太小。虽然如此测得的回路电感值仍然满足本NPC四电平变流模块设计中母排的技术指标。

图11 Sa3的关断电压、电流波形Fig.11 Turn-off current and voltage waveforms of Sa3

表3 NPC四电平回路杂散电感实验与仿真对比Tab.3 Comparison between experiment and simulation

本样机在母线电压为 2 000V的情况下进行了电抗负载实验。其输出电压、电流波形如图12所示,输出电流峰值为100A。该工况下各个功率器件的最高电压过冲在 200V以内,由此可见缓冲电感的引入未造成变流器内部器件电压过冲的增加。

图12 电感负载电压、电流输出波形Fig.12 Output waveforms of inductance load

5 结论

本文针对混合钳位五电平拓扑 1.2MV·A大功率应用场合,进行了单相变流模块的结构布局优化及叠层母排设计。该拓扑无需复杂控制算法即可实现电容电压任意负载情况下自平衡。本文首先研究了该拓扑大功率应用中冲击电流问题产生的原因及抑制方法,其次结合便于冲击电流抑制及母排设计的原则进行了拓扑结构布局的工程优化设计,最后以四电平电路为例进行了多器件、复杂换流回路的多电平拓扑叠层母排设计,研制出一台单相 400kV·A混合钳位五电平变流模块。最终通过双脉冲测试及电感性负载测试验证了设计结果。

[1] 王琛琛, 李永东. 多电平变换器拓扑关系及新型拓扑[J]. 电工技术学报, 2011, 26(1): 92-99. Wang Chenchen, Li Yongdong. Multilevel converter topologies and two novel topologies[J]. Transactions of China Electrotechnical Society, 2011, 26(1): 92-99.

[2] ABB. [OL]. www.abb.com.

[3] 兰志明, 李崇坚, 李耀华, 等. 基于IGCT的大功率三电平双 PWM 变流器的研制[J]. 电工技术学报, 2011, 26(增1): 36-40. Lan Zhiming, Li Chongjian, Li Yaohua, et al. Development of IGCT-based large power three-level dual-PWM converter[J]. Transactions of China Electrotechnical Society, 2011, 26(S1): 36-40.

[4] 高东辉, 杜少武, 张长征. 改进型混合级联多电平有源电力滤波器的研究[J]. 电力系统保护与控制, 2014, 42(1): 40-46. Gao Donghui, Du Shaowu, Zhang Changzheng. Research on an improved hybrid cascade multilevel active power filter[J]. Power System Protection and Control, 2014, 42(1): 40-46.

[5] SIEMENS. [OL]. www.siemens.com.

[6] 王兆宇, 艾芊. 三电平逆变器空间矢量调制及中点电压控制[J]. 电力系统保护与控制, 2011, 39(20): 131-136. Wang Zhaoyu, Ai Qian. Space vector modulation for three-level inverter and neutral point potentialcontrol[J]. Power System Protection and Control, 2011, 39(20): 131-136.

[7] Kouro S, Malinowski M, Gopakumar K, et al. Recent advances and industrial applications of multilevel converters[J]. IEEE Transactions on Industrial Electronics, 2010, 57(8): 2553-2580.

[8] Chen Alian, He Xiangning. Research on hybridclamped multilevel-inverter topologies[J]. IEEE Transactions on Industrial Electronics, 2006, 53(6): 1898-1907.

[9] Zhao Jing, He Xiangning, Zhao Rongxiang. A novel PWM control method for hybrid-clamped multilevel inverters[J]. IEEE Transactions on Industrial Electronics, 2010, 57(7): 2365-2373.

[10] 尹凯, 马铭遥, 何原明, 等. 三相混合钳位五电平PWM 整流器的研究[J]. 中国电机工程学报, 2012, 32(12): 59-66. Yin Kai, Ma Mingyao, He Yuanming, et al. Research on three-phase hybrid-clamped five-level PWM rectifier[J]. Proceedings of the CSEE, 2012, 32(12): 59-66.

[11] 谭成, 何原明, 赵菁, 等. 一种减小混合箝位多电平逆变器母线电容冲击电流的 PWM 控制方法[J].电力自动化设备, 2013, 33(2): 62-67. Tan Cheng, He Yuanming, Zhao Jing, et al. PWM control to reduce surge current of DC-bus capacitor for hybrid-clamped multilevel inverter[J]. Electric Power Automation Equipment, 2013, 33(2): 62-67.

[12] 易荣, 赵争鸣, 袁立强. 高压大容量变换器中母排的优化设计[J]. 电工技术学报, 2008, 23(8): 94-100. Yi Rong, Zhao Zhengming, Yuan Liqiang. Busbar optimization design for high power converters[J]. Transactions of China Electrotechnical Society, 2008, 23(8): 94-100.

[13] Beukes H J, Enslin J H R, Spee R. Busbar design considerations for high power IGBT converters[C]// 28th Annual IEEE Power Electronics Specialists Conference, St. Louis, MO, 1997: 847-853.

[14] Caponet M C, Profumo F, De Doncker R W, et al. Low stray inductance bus bar design and construction for good EMC performance in power electronic circuits[J]. IEEE Transactions on Power Electronics, 2002, 17(2): 225-231.

[15] Yuan Xiaoming, Barbi I. Fundamentals of a new diode clamping multilevel inverter[J]. IEEE Transactions on Power Electronics, 2000, 15(4): 711-718.

[16] Guichon J M, Aime J, Schanen J L, et al. Busbar design: how to spare nanohenries[C]//2006 IEEE 41st Industry Applications Annual Meeting, 2006, Tampa, FL, 2006: 1865-1869.

[17] 汪鋆, 杨兵建, 徐枝新, 等. 750kVA高功率密度二极管箝位型三电平通用逆变模块的低感叠层母线排设计[J]. 中国电机工程学报, 2010, 30(18): 47-54. Wang Jun, Yang Bingjian, Xu Zhixin, et al. Configuration of low inductive laminated bus bar in 750kVA NPC three-level universal converter module of high power density[J]. Proceedings of the CSEE, 2010, 30(18): 47-54.

[18] Nakayama Y, Oi T, Toya K, et al. Power conversion device and fabricating method for the same: US 7881086 B2[P]. 2011-02-01. http://www.google.de/ patents/US7881086

[19] Yuan Liqiang, Zhao Zhengming, Eltawil M, et al. Performance evaluation of switch devices equipped in high-power three-level inverters[J]. IEEE Transactions on Industrial Electronics, 2007, 54(6): 2993-3000.

Engineering Design for Structure and Bus Bar of 1.2MV·A Hybrid Clamped Five-Level Converter Module

Dong Yufei Luo Haoze Yang Heya He Yuanming Li Wuhua He Xiangning

(College of Electrical Engineering Zhejiang University Hangzhou 310027 China)

Multilevel is a key technology to high power converters. Limited by the technical problems such as DC voltage unbalance and bus bar design, only the NPC three-level is widely used in industry for neutral point clamped multilevel topology. The hybrid clamped five-level is a novel topology in which DC voltage can be self-balanced. To promote this topology’s application, engineering design for structure and bus bar of a 1.2MV·A converter module is discussed in this paper. The mechanism and limitation methods of the surge current in this topology are first studied. Then the structure and layout design are carried out following the principle that surge current is easy to restrain and bus bar is easy to design. Finally the laminated bus bar is presented and simulated through Ansoft Q3D, and the 400 kW one phase prototype is completed. Consequently, the experimental results have verified the structure and bus bar.

High power converter module, hybrid clamped 5-level, structure design, bus bar

TM46

董玉斐 男,1990年生,博士研究生,研究方向为多电平技术及其应用。

E-mail: dyf_school@zju.edu.cn(通信作者)

罗皓泽 男,1986年生,博士研究生,研究方向为大功率 IGBT测试及失效分析。

E-mail: luohaoze@163.com

国家重点基础研究发展计划(973计划)项目子课题(2014CB-247400)和国家自然科学基金(51490682)资助项目。

2014-04-22 改稿日期 2015-07-06