基于FPGA的DDR2缓存控制器在无线链路图像跟踪系统中的应用

2016-09-23景彦哲

袁 鑫,卢 磊,景彦哲

(北京航天控制仪器研究所,北京100039)

基于FPGA的DDR2缓存控制器在无线链路图像跟踪系统中的应用

袁 鑫,卢 磊,景彦哲

(北京航天控制仪器研究所,北京100039)

图像跟踪系统是机载光电吊舱的重要组成部分,其对目标捕捉的成功率直接决定了机载光电吊舱的性能。而作用于机载光电吊舱与地面站之间的无线链路系统,有着不可消除的的延时特性,这极大地降低了目标捕捉成功率。本文设计了一种基于FPGA的DDR2缓存控制器,通过缓存控制器可以轻松实现高清视频图像的快速存储和调用,从而实现图像跟踪算法对无线链路延时的补偿。该缓存控制器成功应用于某型机载光电吊舱图像跟踪系统,有效消除了无线链路延时的影响,提高了图像跟踪系统对目标捕捉的成功率。

机载光电吊舱;FPGA;图像缓存跟踪系统;DDR2 SDRAM

0 引言

图像跟踪系统是机载光电吊舱的重要组成部分,其目标捕捉、目标识别跟踪、跟踪速度、跟踪精度等指标直接决定了机载光电吊舱的性能。而目标捕捉的成功率是图像跟踪系统发挥其性能的关键。作用于机载光电吊舱与地面站之间的无线链路系统,有着不可消除的延时特性,上行控制指令延时和下行图像延时将导致操作手很难捕捉到需要的目标,极大地降低了目标捕捉的成功率。在实际应用中,往往需要培训专业操作手,提前熟悉链路延时,并能够根据载机的飞行方向和速度,以及目标运动的方向和速度预估目标的位置进行捕捉,对操作手提出了很高的要求,增加了光电吊舱的使用难度,降低了用户体验。

本文设计了一种基于FPGA的DDR2缓存控制器,采用ALTERA公司的Cyclone IV系列FPGA对DDR2高速缓存模块数据的突击读取和写入,实现高清视频图像的快速存储和调用。从而实现图像跟踪算法对无线链路延时的补偿。该缓存控制器已经成功应用于某型机载光电吊舱图像跟踪系统,有效消除了无线链路延时的影响,提高了图像跟踪系统对目标捕捉的成功率。

1 图像缓存跟踪方案设计

地面站与机载光电吊舱之间的无线链路延时包括两部分:一是地面跟踪指令通过上行无线链路发送到机载光电吊舱产生的上行链路延时,以及实时画面从机载光电吊舱通过无线链路发送到地面站产生的下行链路延时。

其中,上行链路延时会导致机载光电吊舱收到控制指令时,处理的图像已不是地面站看到的图像;下行链路延时导致地面站看到的图像不是机载光电吊舱实时拍摄的图像。所以无线链路延时对吊舱系统影响的本质是影响了吊舱系统图像传输的实时性,进一步影响了地面站操作人员抓取跟踪目标的成功率。

图像缓存跟踪方案流程图如图1所示,由于上行链路延时和下行链路延时对图像跟踪算法的影响是叠加效应,因此将两种链路延时统一为上行链路延时方便分析。机载光电吊舱系统摄像机捕捉图像始终为实时图像,地面站显现图像为延时图像。

地面站操作人员对延时图像中的目标发出图像跟踪指令,图像跟踪指令通过无线链路到达机载吊舱系统。图像缓存跟踪器会根据链路延时在高速缓存模块中提取延时画面(高速缓存中第n帧),这样捕捉到的目标信息与地面站操作人员发出跟踪指令时捕捉到的目标信息一致。

为了让吊舱系统恢复到跟踪当前实时图像中的目标,需要图像跟踪系统短时间内按照时间顺序连续(第m次)提取高速缓存中的(第n-m帧)图像,直到提取到当前图像为止。此时图像跟踪系统实时跟踪当前图像中的目标。

图1 图像缓存跟踪方案流程图Fig.1 Flow chart of image cache tracking system

2 硬件系统设计

图像缓存跟踪电路是在原有图像跟踪电路的基础上设计完成的,总体框架图如图2所示。主要修改的模块包括 FPGA可编程门阵列模块、DDR2高速缓存模块、供电电源模块。

2.1FPGA模块

FPGA模块作为本系统的核心部分,主要完成图像数据中波门坐标数据的提取,对DDR2高速缓存模块的读写,与DSP模块数据交互和处理等功能。原有图像跟踪电路中采用的是ALTERA公司的CycloneIII系列中的EP3C120CF780I,这款芯片的速度等级参数为7,高速接口最快速率为300Mbit/s,与标准的DDR2芯片高速接口速率相比较低,因此重新选择ALTERA公司的CycloneIV系列中的EP4CE115F29C7N,该芯片具有以下特点:114480个逻辑单元(LE);3888Kbits嵌入式存储器;266个嵌入式18×18乘法器;4个通用PLL;20个全局时钟网络;8个用户I/O块;528个最大用户IO;接口速率等级为8,高速接口最快速率可达400Mbit/s。

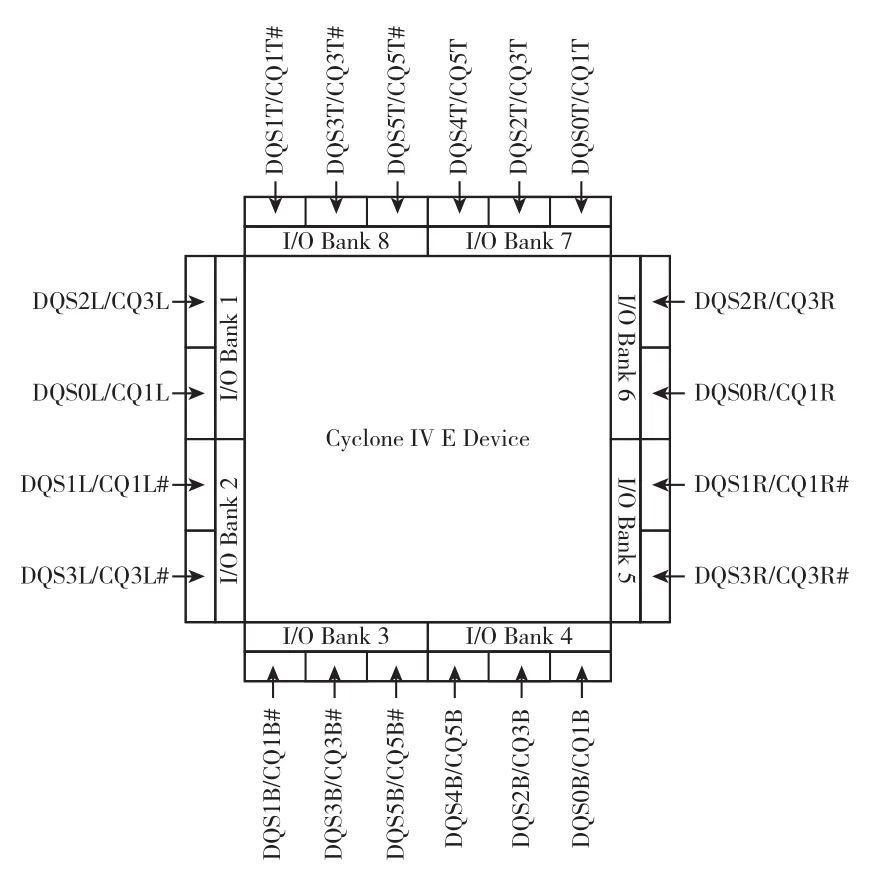

如图3所示,CycloneIV系统FPGA芯片内部分成8个bank,每个bank中都有专门的DQS数据线组来满足高频存储器的读写要求,此外芯片上还提供RUP和RDN管脚,只要连接相应的上拉、下拉电阻,就可以在初始化阶段配置,得到更加精确的OCT控制参数提高数据读写的准确率,以确保对DDR2高度缓存模块读写的准确性。

图2 总体框架图Fig.2 The overall framework

图3 CycloneIV FPGA芯片内部结构Fig.3 Chip internal structure of CycloneIV FPGA

2.2DDR2高速缓存模块

DDR2高速缓存模块主要负责对图像数据进行快速采集和调用,本系统中选用MICRO公司的MT47H64M16芯片。DDR2采用时钟上升沿和下降沿同时进行数据传输的基本模式,速度是普通存储器件的2倍,常用传输速度能达到667Mbit/s。MT47H64M16芯片框架结构在传统的地址总线、数据总线、命令数据总线结构基础上,增加外部ODT(ON-DIE TERMINATION)引脚,通过调整配置电阻值,来克服片内总线上的信号反射效应,抑制导线信号自扰;芯片内部采用OCD离线驱动调整,通过调整输出驱动的上拉/下拉电阻,使得充放电动作的电压误差减到最小,保证内部输出的稳定;另外芯片采用4bit预存技术,使得在同样时钟频率下,能达到4倍于普通DDR芯片的传输速度。

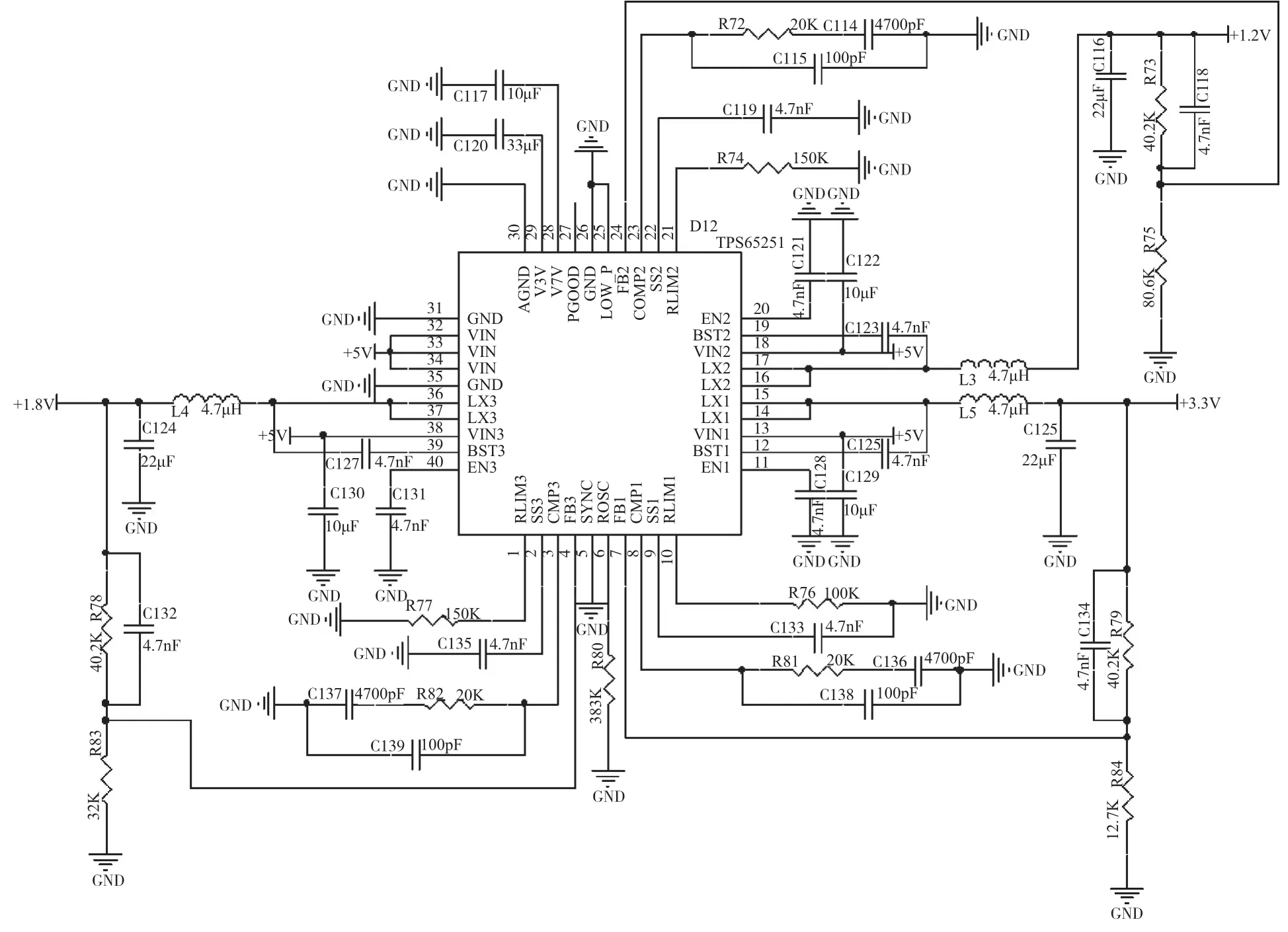

2.3供电电源模块设计

在整个外围电路设计中,电源模块设计是非常重要的,电源模块的稳定性直接影响着整个电路中各个模块工作有效性。本系统中选用TI公司的TPS65251开关电源模块,主要特点:宽输入电源电压范围(4.5V~18V);最大电流:3.5A(降压开关1),2.5A(降压开关2和3);可调开关频率为300KHz~2.2MHz(由外部电阻设置);可调电流限制(由外部电阻设置);具有简单补偿电路的电流模式控制;自动脉频调制(PFM)/脉宽调制(PWM)操作。

电路原理图如图4所示,本系统中电源采用+5V电源输入,通过外部电容电阻进行参数配置,使输出端口LX1输出+3.3V电源,为DSP数字处理器和FPGA可编程门阵列相应模块供电;输出端口LX2输出+1.2V电源,为DSP数字处理芯片的内核模块供电;输出端口LX3输出+1.8V电源,为DDR2缓存模块供电。

图4 TPS65251电源原理图Fig.4 Power principle diagram of TPS65251

由于DDR2高速缓存模块是通过比较数据总线和地址总线电平与DDR2_VERF参考电压端口来进行快速存储读写,因此DDR2_VERF供电电压的稳定性直接影响DDR2模块高速读写的误码率。本系统设计中采用TI公司DDR2专用芯片LP2997来实现DDR2_VERF的高精度稳压特性,原理图如图5所示,该芯片配置简单,只需要在VIN输入端和VREF输出端接2个滤波电容就可正常工作,电压稳定精度可以达到99.7%。

图5 LP2997电源原理图Fig.5 LP2997 power chip sheet

3 软件设计

3.1FPGA软件设计

(1)DDR2接口控制模块

ALTERA公司开发的QUARTUS软件中有着强大的IP核模块库,库中有IP核支持标准DDR2元器件的接口。通过ALTERA IP核可以方便地生成DDR2 SDRAM接口文件,DDR2匹配参数的设置如图6所示,其中重要的参数主要有:Memory burst length突发读写长度要根据参考时钟来计算,全频时钟Full-rate模式下选择8,半频时钟Halrate模式下选择4;ODT终止电阻大小的选择要根据PCB中实际走线阻抗来设置,通常在布PCB电路时要求数据总线高频阻抗保证在40Ω~60Ω。

(2)图像数据缓存模块

图像数据缓存模块:实现的主要功能是对每行图像有效数据进行缓存,保证DDR2高速读写存储数据时,数据总线的数据变化周期能与DDR2读写时钟周期一致。

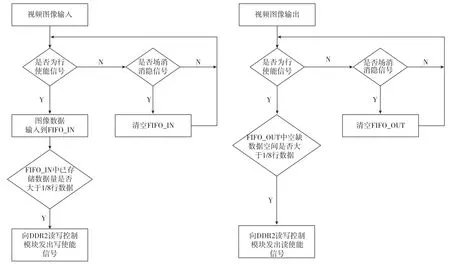

图像数据缓存模块流程图如图7所示,图像数据缓存模块在行使能有效的时间内,将图像输入数据按照像素时钟写入FIFO_IN模块(从FIFO_ OUT模块中读出)。在场消隐时间段内清空FIFO_ IN和FIFO_OUT空间数据,防止错误数据流入下一帧图像数据,降低图像质量。当FIFO_IN中存储的数据量大于1/8行数据时(FIFO_OUT中剩余存储空间大于1/8行数据时),向DDR2读写控制模块发送写使能信号(读使能信号)。

图6 DDR2匹配参数的设置表Fig.6 DDR2 parameter table

图7 图像数据缓存模块流程图Fig.7 Flow chart of image cache module

由于DDR2 SDRAM的读写速率远快于图像数据输入速率,这里对 FIFO按照单行长度读入,1/8行长度读出,这种分段流水操作可以减少数据等待延时,提高数据流通效率。

(3)DDR2读写控制模块

DDR2读写控制模块:实现的主要功能是对读写请求信号进行优先级管理,对读写操作的地址总线、数据总线和命令数据总线进行对应的赋值操作,保证DDR2 SDRAM的读写时序满足设计要求。

图8为DDR2读写控制模块的设计流程图,如图8所示在没有图像跟踪指令到达时,读写控制模块实时对图像数据缓存模块产生的读写请求信号进行应答,为了保证视频数据不会出现漏行、坏点等视频显示问题,在读写请求信号同时达到时优先应答写请求信号。

图8 DDR2读写控制模块流程图Fig.8 Flow char of DDR2 read-write control module

在进入读写状态后,先判断是否满足突发数据读写要求,如果满足应优先选择突发数据读写模式对DDR2 SDRAM模块进行读写操作。

在地面站图像跟踪指令到达时,停止应答图像数据缓存模块产生的读写请求信号,按照DSP数字信号处理芯片返回的无线链路延时时间,向DDR2 SDRAM中对应的延时图像数据地址发送读请求信号,快速调用延时图像数据。

在调用完延时图像数据后,按照时间顺序高帧频逐帧连续读出图像数据,短时间内将捕捉目标对应位置由延时图像切换到实时图像位置,以满足吊舱系统跟踪要求。

3.2DSP软件设计

DSP芯片的软件系统是在原有图像跟踪系统DSP软件的基础上重新设计完成,具体流程图如图9所示,在对芯片内部相应模块初始化完成后,会使能相应的外部中断向量,实时响应外部控制指令,并采集跟踪图像波门数据。

图9 DSP芯片软件系统流程图Fig.9 Flow chart of DSP software system

在跟踪指令到达后,DSP芯片会通过外部中断进行握手操作,实时计算无线链路延时时间,通过高速外部接口EMIFA发送给FPGA的读写控制模块,采集延时图像波门数据。

根据相应的图像跟踪算法,对图像波门数据中的捕捉目标进行实时捕捉,然后将脱靶量输出给机载光电吊舱伺服控制系统。

当退出跟踪指令到达或者跟踪算法判定目标跟踪丢失条件下,软件会退出跟踪状态,等待下一次跟踪指令的到达。

4 实验验证

利用机载光电吊舱系统进行如下实验:

1)在实验室环境下,采用动态目标模拟器模拟真实环境下运动的目标;

2)在上位机控制软件中加入延时模块,模拟链路延时;

3)关闭机载光电吊舱图像跟踪系统 DDR2 SDRAM图像高速缓存模块,进行动态目标捕捉;

4)打开机载光电吊舱图像跟踪系统 DDR2 SDRAM图像高速缓存模块,进行动态目标捕捉。

实验数据:

对实验步骤2和实验步骤3分别进行200次动态目标捕捉实验,如表1所示。通过对实验数据的数据分析可以看出,DDR2图像缓存控制器有利于提高图像跟踪系统的性能。

表1 实验数据Table 1 Experimental data

5 结论

本文设计了一种基于FPGA的DDR2缓存控制器,通过缓存控制器可以实现高清视频图像的快速存储和调用,从而实现图像跟踪算法对无线链路延时的补偿。该缓存控制器成功应用于某型机载光电吊舱图像跟踪系统,通过实验证明缓存控制器有效消除了无线链路延时对目标捕捉的影响,提高了图像跟踪系统对目标捕捉的成功率。

[1] 赵天云,王洪迅,郭雷,等.DDR2 SDRAM控制器的设计与实现[J].微电子学与计算机,2005,22(3):203-207. ZHAOTian-yun,WANGHong-xun,GUOLei,et al.DDR2 SDRAM controller design and implementation [J].Journal of Microelectronics and Computer,2005,22 (3):203-207.

[2] Samir Palnitkar.Verilog HDL数字设计与综合[M].北京:电子工业出版社,2009. Samir Palnitkar.Verilog HDL digital design and synthesis [M].Beijing:Electronics Industry Press,2009.

[3] 刘冠男,欧明双,宋何娟.DDR2 SDRAM控制器的设计及FPGA验证[J].中国集成电路,2010,19(4):42-45. LIU Guan-nan,OU Ming-shuang,SONG He-juan.DDR2 SDRAM controller design and the FPGA verification[J]. China Integrated Circuit,2010,19(4):42-45.

[4] 徐家刚,张永伟,徐瑞荣 .基于 FPGA与 DDR2 SDRAM的高速ADC采样数据缓冲器设计[J].舰船电子对抗,2010,33(1):104-108. XU Jia-gang,ZHANG Yong-wei,XU Rui-rong.Based on FPGA and DDR2 SDRAM high-speed ADC sampling data buffer design[J].Ship Electronic Countermeasures,2010,33(1):104-108.

[5] 陈雨,陈科,安涛.高速图像处理系统中DDR2-SDRAM接口的设计[J].现代电子技术,2011,34(12):104-108. CHEN Yu,CHEN Ke,AN Tao.DDR2 SDRAM interface in high-speed image processing system design[J].Modern Electronic Technology,2011,34(12):104-108.

Based on FPGA DDR2 Cache Controller in the Application of the Wireless Link Image Tracking System

YUAN Xin,LU Lei,JING Yan-zhe

(Beijing Institute of Aerospace Control Devices,Beijing 100039)

Image tracking system is an important part of the airborne electro-optical pod,its success rate of target capture directly determine the performance of airborne electro-optical pod.And the wireless link between airborne electrooptical pod and ground station system can't eliminate the delay characteristics,which greatly reduces the success rate of target capture.In this paper,we design a DDR2 cache controller based on FPGA,by caching controller can easily implement hd video image storage and call quickly,so as to realize wireless link delay compensation of image tracking algorithm.The cache controller is successfully applied in a certain type of airborne electro-optical pod image tracking system,effectively eliminate the influence of the wireless link delay and improve the success rate of target capture in the image tracking system.

airborne electro-optical pod;FPGA;image cache tracking system;DDR2 SDRAM

U666.1

A

1674-5558(2016)03-01175

10.3969/j.issn.1674-5558.2016.04.011

2015-07-23

袁鑫,男,助理工程师,研究方向为光电稳定平台设计。