一种10 bit双通道流水线SAR ADC设计*

2016-09-16刘东海韦忠善广西职业技术学院计算机与电子信息工程系南宁530226

刘东海,韦忠善,邓 云(广西职业技术学院计算机与电子信息工程系,南宁530226)

一种10 bit双通道流水线SAR ADC设计*

刘东海,韦忠善*,邓云

(广西职业技术学院计算机与电子信息工程系,南宁530226)

为了提高模数转换器的采样频率并降低其功耗,提出一种10 bit双通道流水线逐次逼近型(SAR)模数转换器(ADC)。提出的ADC包括两个高速通道,每个通道都采用流水线SAR结构以便低功率和减小面积。考虑到芯片面积、运行速度以及电路复杂性,提出的处于第二阶段的SAR ADC由1 bit FLASH ADC和6 bitSAR ADC组成。提出的ADC由45 nm CMOS工艺制作而成,面积为0.16mm2。ADC的微分非线性和积分非线性分别小于0.36最低有效位(LSB)和0.67 LSB。当电源为1.1 V时,ADC的最大运行频率为260Msample/s。运行频率为230Msample/s和260Msample/s的ADC的功率消耗分别为13.9mW和17.8mW。

模数转换器(ADC);双通道;流水线;逐次逼近型(SAR)

近来,由于对数字电视和无线接收机等视频信号处理和通信系统的需求迅速增加,采样率为几百兆赫的低功率、小面积10 bit模数转换器(ADC)已经成为了十分重要的部件。对于这些高速的ADC,使用了FLASH sub-ADC的流水线结构普遍用于优化功率和面积[1-4]。

另一方面,得益于CMOS技术的发展,逐次逼近型(SAR)ADC得到了广泛应用,原因在于其功率效率高、面积小。在分辨率为10 bit的情况下,通过使用异步内部时钟、误差补偿、电容器切换等技术,传统SAR ADC的运行频率会增加至100MHz[5-6]。然而,由于串行信号处理,传统SAR ADC仍被限速。高速SAR ADC的采样周期短,忙闲度为10%~20%,这样可轻易获得充分的SAR转换(SC)时间。然而,驱动SAR ADC的可变增益放大器和模拟滤波器等缓冲器需要宽带运算放大器,这是模拟前端电路上耗电最多的部件,导致整体能耗较高。

为了将SAR ADC的效率和流水线ADC的高速运行融合起来,文献[7-8]介绍了流水线SAR结构。尽管,相较于传统的流水线ADC,此结构适合于小芯片面积以及低功率消耗,但在运行频率大于等于200MHz的情况下,使用只有一个通道的流水线SAR ADC性能较差。此外,用于高采样率的时间交错流水线SAR ADC需要校准技术用以消除通道偏移、通道间的增益误差以及电容器失配[9-10]。

因此,提出一种10 bit双通道流水线逐次逼近型(SAR)模数转换器(ADC)。为了获得高采样率,采用了双通道以及FLASH-SAR结构。运算放大器共享技术减少了功率消耗和面积。本文提出的自适应时钟技术简化了时钟产生器,并使用3个缓冲器结合抗尖峰脉冲电路,将通道失配以及参考干扰降至最低。当电源为1.1 V时、运行频率为230Msample/s以及输入为78 MHz时,ADC的信号-噪声及失真比(SNDR)为54.6 dB,无杂散动态范围为64.0 dB。

1 提出的双通道流水线SAR ADC结构

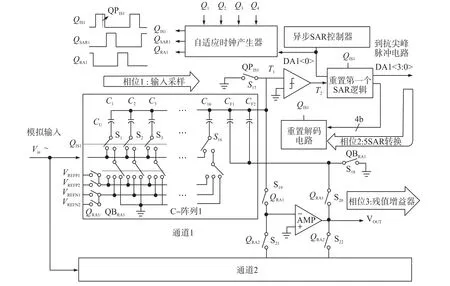

图1是本文提出的10 bit流水线ADC的方框图。此10 bit流水线ADC包括两个通道,每个通道都会循序地处理两个阶段的模拟信号。为了优化面积以及运行频率,基于异步判定的sub-ADC由4 bit SAR ADC和7 bit FLASH-SAR ADC实现[11-12]。为了获得高运行频率,FLASH-SAR结构适合于减少SC循环。为了进一步降低功率和减小面积,两个通道之间共享一个运算放大器。通用的剩余区块包括一个误差校正逻辑(ECL)、3个带有抗尖峰脉冲技术的基准直流缓冲器、一个电流产生器以及一个四相位时钟产生器。ECL通过第1阶段和第2阶段之间的1 bit重叠来纠正数字编码。为了减少通道失配以及保持所有运作模式下的基准精确度,采用了3个基准直流缓冲器。两个基准直流缓冲器用于第1阶段的两个4 bit SAR ADC以及运算放大器,剩余的基准直流缓冲器用于第2阶段的两个7 bitFLASH-SAR ADC。本文提出的抗尖峰脉冲技术可以减少由电容器切换产生的参考故障。设计的电流产生器带有一个电阻器以及两个N通道MOSFET(NMOS),适用于小面积,此电流产生器向比较器和运算放大器等模拟区块提供恒定电流。双通道FLASH-SAR结构需要四相位时钟产生器。

图1 本文提出的双通道流水线SAR ADC的结构

2 通道运行时序

图2是通道1的详细时序图,通道1以自适应时钟技术为基础有效分配内部时钟的周期。通道2的运作与通道1的运作一样,一个循环(1/fS)使时钟位移以获得ADC功能。每个阶段都在内部生成时钟的输入采样(IS)、SC、残值增益(RA)以及残值采样(RS)。

图2 本文提出的ADC的时序图(通道1)

第1阶段是由IS1、SC1和RA1的三相位进行操作,第2阶段是由RS2和SC2的二相位进行操作。首先,在IS1(N)期间,由第1阶段对模拟输入进行采样检查,并且在Q2的上升沿开启4 bit SC。RA1(N)和RS2(N)的内部时钟是为第1个和第2个SCs完全完成之后在Q3内自动传输高态而设计的。由于4 bitSAR ADC上的SC1(N)周期是由结构和电路参数固定的,放大时间根据输入时钟频率变化。为了确保RA1(N)和RS2(N)的操作,RA1(N)和RS2(N)的最小周期设计为Q4,从下一个Q1开始使用第二阶段内7 bitADC的SC2(N)。

本文提出的ADC的4 bit和7 bit SC的时间分别为3.2 ns和5.6 ns。在时钟频率低的情况下,第1阶段内IS1(N)和SC1(N)的周期总数比第2阶段内SC2(N-2)的周期更长,原因在于IS1(N)周期与Q1一样。然后,RA1(N)周期与Q3和Q4的总数一样,原因在于在Q2内结束了SC1(N)和SC2(N-2)的操作。另一方面,在时钟频率超过200 MHz的情况下,SC2(N-2)周期比IS1(N)和SC1(N)的总数更长,原因在于1 bit的平均判定时间约为0.8 ns。因此,RA1(N)周期减少至低于Q3和Q4的总数。考虑到非重叠时钟界线,RA1(N)周期约为4.0 ns~4.1 ns。本文提出的结构中ADC运行速度的瓶颈在于第2阶段。为了解决此问题,本文提出的ADC在第2阶段采用了FLASH-SAR结构。FLASH ADC在RA1(N)结束时判定了1 bit,并且SAR ADC在SC2(N)期间判定了6 bit。因此,本文提出的ADC实现了高采样率,采样率超过200MHz。

3 流水线SAR ADC的实现

3.1第一阶段设计

图3是第1阶段的方框图。

图3 基于4 bit SAR结构的第1阶段

第1阶段的通道1包括带有16个装置电容器的C-阵列1、两个反馈电容器、一个比较器、一个SAR逻辑、一个SAR控制器、一个自适应时钟产生器、一个解码电路以及一个共享的运算放大器。第1阶段的功能分为IS、用于4 bit判定的SC以及RA。通常,流水线 ADC需要采样保持放大器(SHA)以减少使用FLASH型的sub-ADC与倍增的数模转换器(MDAC)之间的采样失配。在本文提出的ADC中,不需要前端SHA,原因在于C-阵列1常用于sub-ADC和MDAC功能。考虑到电容器失配和kT/C噪声,C-阵列1的装置电容和总采样电容分别为100 fF和1.6 pF。与装置电容器底板连接的基准开关由解码电路控制。此外,运算放大器共享技术应用于两个通道之间以降低功率和减少面积。残值运算放大器使用了两级结构,两级结构包括了互补折叠共源共栅运算放大器和互补输入对运算放大器,前者实现高dc增益,后者实现获得高跨导以及宽输出摆幅。基于开关电容器型的共模反馈(CMFB)由两个相反的时钟相位分开。分开的CMFB具有传统CMFB一半的电容。

SC的比较器由前置放大器和锁存器组成。由于分辨率低,可几乎忽略比较器的热噪声。SAR控制器生成了用于SAR ADC迭代操作的异步时钟。由自适应时钟产生器制成QIS、QSAR和QRA的内部时钟,时钟产生器带有四相位时钟和LSB位—判定信号DA1<0>。

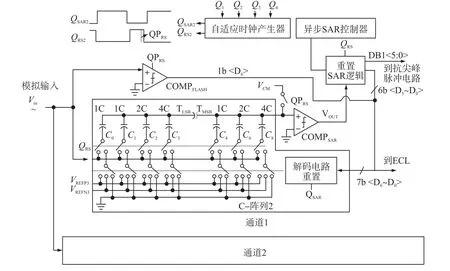

3.2第2阶段设计

图4是包括7 bit FLASH-SAR ADC的第2阶段,用于减少SC时间。最高有效位(MSB)由1 bit FLASH ADC确定,并且剩余的LSB由6 bit SAR ADC判定。通常,由于FLASHADC包括2N-1比较器,1 bit FLASH ADC仅需要一个比较器,可以检测差分输入的零交叉。因此,不需要任何额外电路。通过使用基于VCM切换方案的分裂电容器结构启用了SC的C-阵列2,用于减少电容器的数量[6]。包括分裂电容器在内的电容器总数为16,且装置电容为55 fF。分裂电容器比装置电容器大,原因在于TLSB节点的寄生电容。

图4 基于7 bit FLASH-SAR结构的第2阶段

第2阶段的操作总结如下。在QPRS结束时,1 bit FLASH ADC的比较器判定了D6的MSB,且将MSB编码传递至6 bit SC中C-阵列2的解码电路。然后,将电容器C6的底板连接至VREFP3或VREFN3,并且将剩余的电容器C0~C5连接至QSAR上升沿的VCM。SAR ADC的比较器从D5到D0循序判定。因此,7 bit FLASH-SAR ADC的转换时间与传统6 bit SAR ADC的转换时间一样。

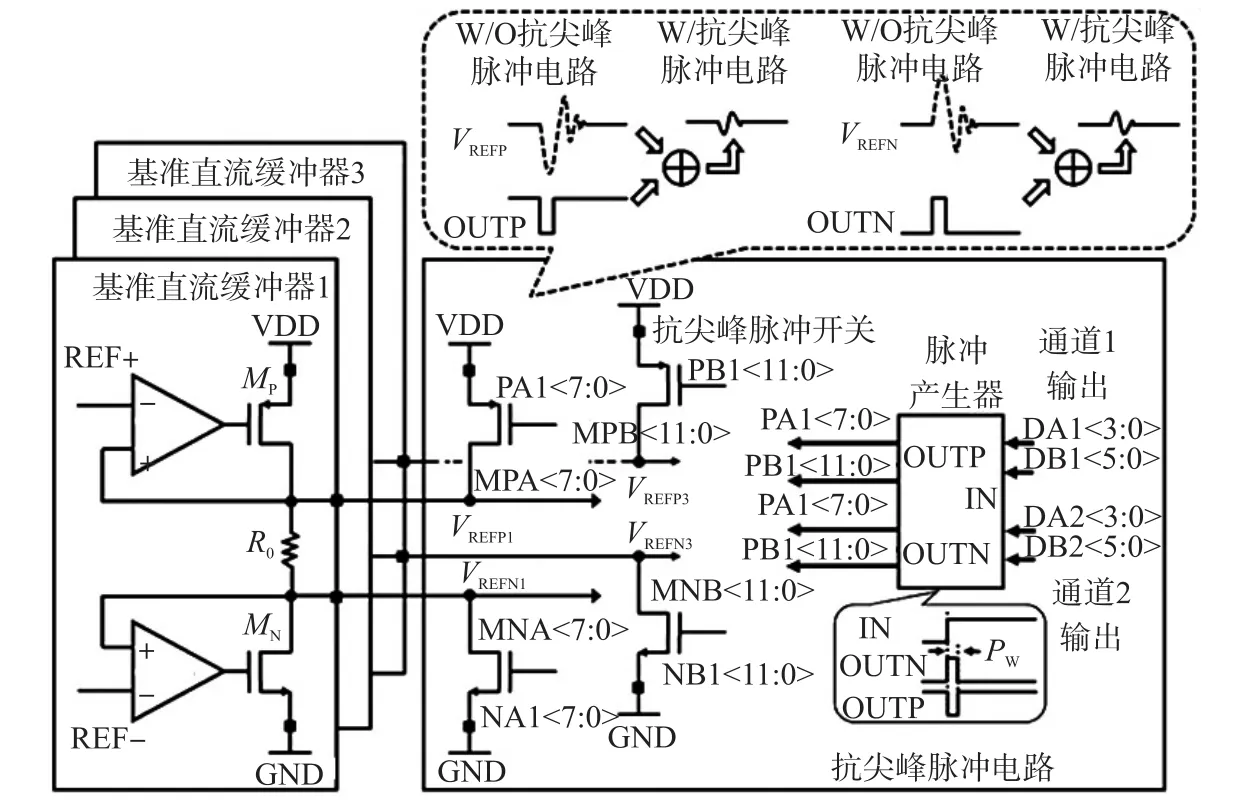

3.3提出的3个基准直流缓冲器方案

图5 带有抗尖峰脉冲技术的基准直流缓冲器

图5是3个带有抗尖峰脉冲技术的基准直流缓冲器。在本文提出的ADC中,基准直流缓冲器必须驱动两个4 bitSARADC、两个7 bitFLASH-SARADC以及带有MDAC功能的共享残值运算放大器。尤其是,带有7 bit精确度的SAR ADC的基准电压固定低于0.8 ns。为了满足沉降条件,本文提出的ADC采用了脉冲产生器,以及基于MPA、MPB、MNA和MNB抗尖峰脉冲开关的抗尖峰脉冲技术。当开启与电容器底板连接的基准开关时,基准电压瞬间会产生较大峰值,并且下一次固定为要求的电压水平。为了稳定短时间内的基准电压,传统的基准直流缓冲器会散逸流经R0的较大静态电流。另一方面,带有抗尖峰脉冲技术的基准直流缓冲器可以通过使用了抗尖峰脉冲开关的动态电流控制减少静态电流[13]。由于DA1~2<3:0>和DB1~2<5:0>的位判定信号以及数码输出编码同时由SARADC生成。带有固定脉冲宽度的PA1<7:0>、PB1<11:0>、NA1<7:0>和NB1<11:0>的控制信号仅由脉冲产生器生成。因此,开启NMOS 和P通道MOSFET(PMOS)开关以便向VREFP和VREFN提供大量电荷。将抗尖峰脉冲开关与VDD或GND连接,原因在于基准电压的较大峰值出现在共模电压的方向。每个开关的大小由脉冲宽度以及与基准电压连接的装置电容器的数量判定。

尽管抗尖峰脉冲技术提高了基准电压的沉降,但是难以通过使用一个基准直流缓冲器启用双通道流水线SAR ADC。在通道1的RA周期内,由通道2 SAR ADC生成的基准电压故障干扰了通道1运算放大器的输出,如图6所示。为了解决基准电压的干扰问题,一个方法是每个通道都使用一个基准直流缓冲器[10]。然而,此方法会造成增益失配,原因在于两个通道的基准电压存在差异。如图6所示,本文提出的参考方案是通过3个基准直流缓冲器来减少通道失配和干扰。在两个4 bitSC期间使用了基准直流缓冲器1,在第1阶段的RA期间内使用了基准直流缓冲器2。最后,在第2阶段的两个7 bit FLASH-SAR转换期间使用了基准直流缓冲器3。在这种情况下,可以消除通道失配,并且不会出现参考干扰,原因在于基准直流缓冲器由ADC功能共享并分开。

图6 提出的ADC的3个基准直流缓冲器方案

4 实验结果

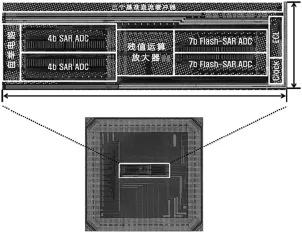

提出的双通道流水线SAR ADC由45 nm CMOS工艺制作而成,如图7所示。本文提出的ADC的模具有效面积为0.16mm2(0.705mm×0.225mm),带有三个基准直流缓冲器。为了减少通道失配,将模拟区块相邻放置。

图7 模具照片

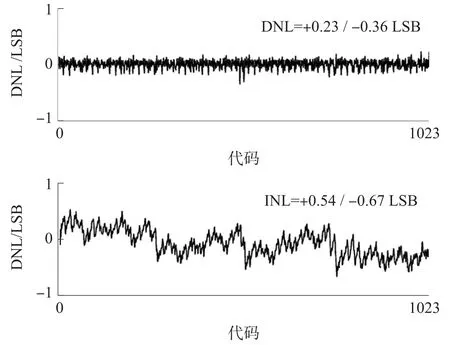

图8是10 bit精确度情况下的测量微分非线性(DNL)和积分非线性(INL)。DNL和INL分别为+0.23/-0.36 LSB和+0.54/-0.67 LSB。

图8 测量的DNL和INL

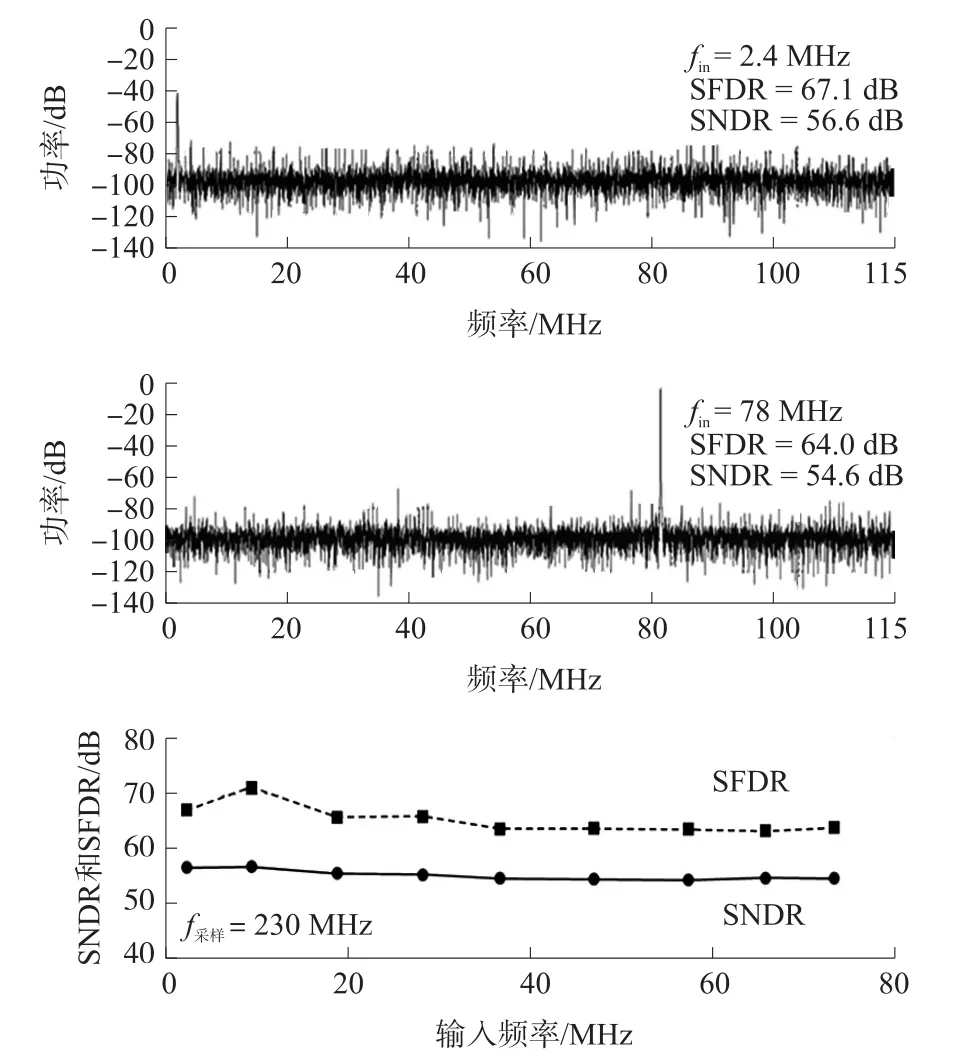

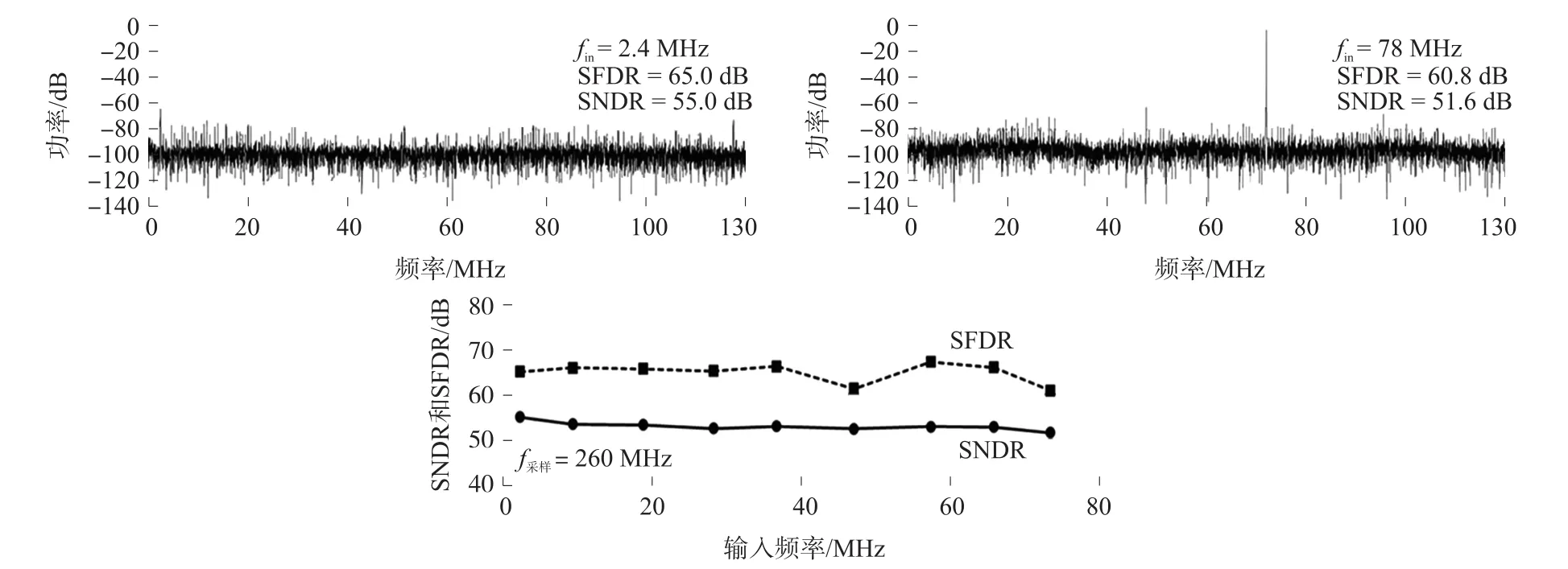

图9是测量的快速傅里叶变换(FFT)图以及当电源为1.1 V时ADC的动态特性,显示了无杂散动态范围(SFDR)和SNDR。在输入频率为2.4MHz的情况下,SNDR为56.6 dB;在输入频率为78MHz的情况下,SNDR保持在54.6 dB以上。在电源电压测试的结果中,当电源为1.2 V时,本文提出的ADC能够达到260Msample/s,如图10所示。在输入频率为78MHz的情况下,SNDR为51.6 dB,并且有效位数(ENOB)超过8.8 bits。

本文提出的ADC的运行速度提升,原因在于SAR ADC中的比较器和逻辑延迟减少。表1总结了ADC的功率消耗和品质因数(FOM)。当电源为1.1 V时,ADC散逸了大约13.9mW。模拟电源为10.6mW,包括来自3个基准直流缓冲器的6.0mW,并且数字电源为3.3mW。当电源为1.2 V时,ADC散逸了17.8mW,其中包括模拟电源的13.0mW和数字电源的4.8mW。本文提出的ADC的FOM定义为功率/(2×fin×2ENOB),当运行频率为230Msample/s 和260 Msample/s且输入为78 MHz时,其分别为203 fJ/转换步骤和367 fJ/转换步骤。

图9 测量的FFT图以及当电源为1.1 V时本文提出的ADC的动态特性

图10 测量的FFT图以及当电源为1.2 V时本文提出的ADC的动态特性

表1 性能总结以及比较

4 结论

本文提出一种10 bit双通道流水线逐次逼近型SAR ADC。为了提高采样率,使用了自适应定时技术和带有两个通道的FLASH-SAR结构。本文提出的参考方案带有3个基准直流缓冲器,使用此方案消除了通道失配。实验测试的ADC由45 nm CMOS制作而成,面积为0.16mm2,当电源为1.1 V且运行频率为230 Msample/s时,提出的ADC散逸了13.9mW。当电源为1.2 V时,ADC的运行频率增加至260Msample/s。

[1] Lee SC,Jeon Y D,Kwon JK,et al.A 10-bit 205-MS/s 1.0-mm2 90-nm CMOS Pipeline ADC for Flat Panel Display Applications [J].IEEE Journal of Solid-State Circuits,2008,42(12):2688-2695.

[2] 林俪,任俊彦,叶凡.A 1.4-V 25-mW 600-MS/s 6-bit Folding and Interpolating ADC in 0.13-μm CMOS[J].半导体学报,2010,31(2):70-75.

[3] Huang G Y,Chang SJ,Liu CC,et al.10-bit 30-MS/s SAR ADC Using a Switchback Switching Method[J].IEEE Transactions on Very Large Scale Integration Systems,2013,21(3):584-588.

[4] Harpe P,Cantatore E,Van Roermund A.A 10b/12b 40 kS/s SAR ADCW ith Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step[J].IEEE Journal of Solid-State Circuits,2013,48(12):3011-3018.

[5] HuW,Liu Y T,Nguyen T,etal.An 8-BitSingle-Ended Ultra-Low-Power SARADCwith a NovelDACSwitchingMethod and a Counter-Based Digital Control Circuitry[J].IEEE Transactions on Circuits&Systems IRegular Papers,2013,60(7):1726-1739.

[6] 郑敏,何明华,杨尊先.一种用于14 bit SAR ADC的数字自校准算法[J].电子技术应用,2011(1):49-51,54.

[7] Shafti A,YavariM.A Zero-Crossing Based 10-bit100MS/s Pipeline ADC with Controlled Current in 9002nm CMOS[J].Analog Integrated Circuits&SignalProcessing,2014,80(1):141-151.

[8] Verbruggen B,IriguchiM,Craninckx J.A 1.7 mW 11b 250 MS/s 2-Times Interleaved Fully Dynamic Pipelined SAR ADC in 40 nm Digital CMOS[J].IEEE Journal of Solid-State Circuits,2012,47 (12):2880-2887.

[9] 张少真,李哲英.应用于SAR ADC中逐次逼近寄存器的设计[J].北京联合大学学报(自然科学版),2011(2):15-19.

[10]彭新芒,杨银堂,朱樟明.一种采用0.5μm CMOS工艺的多通道SAR ADC[J].微电子学,2007(2):217-220.

[11]李现坤,张瑛,郭宇锋,等.一种10 bit1MS/s SAR ADC的设计实现[J].计算机技术与发展,2014(8):210-214.

[12]胡黎斌,李文石.低功耗-高速-高精度SAR ADC的FoM函数研究[J].电子器件,2011,34(2):341-345.

[13]戴强,薛颜,杨霄垒,等.一种对失调和电容失配误差进行补偿的流水线ADC子级电路[J].电子器件,2014,37(5):812-815.

刘东海(1979-),男,广西兴安县人,研究生,讲师,主要从事电子技术、电气自动化技术教学与研究,liudonghai001@ 126.com;

韦忠善(1972-),男,广西横县人,硕士,副教授,主要从事电子技术、计算机仿真技术教学与研究;

邓云(1983-),男,广西全州县人,硕士,讲师,主要从事应用电子技术专业研究与教学。

Design of a DualChannel10 bit Pipelined SAR ADC*

LIU Donghai,WEI Zhongshan*,DENG Yun

(Department of Computerand Electronic Information Engineering,Guangxi Vocationaland TechnicalCollege,Nanning 530226,China)

In order to improve the sampling frequency and reduce the power consumption ofa digital converter,a 10 bitdual channel pipelined successive approximation(SAR)/digital converter(ADC)is proposed.The proposed ADC consists of two high speed channels,each channel is pipelined SAR structure for low power and reduced area.Taking into account the chip area,operating speed and circuit complexity,the proposed second stage ADC SAR consists of 1 FLASH ADC bit and 6 SAR ADC bit.The proposed ADC ismade of 45 CMOS nm process,the area is 0.16mm2.The differential nonlinearity and integral nonlinearity of ADC are less than 0.36minimum effective bits (LSB)and 0.67 LSB.When the power is 1.1 ADC,themaximum operating frequency of Msample/s is 260 V.The operating frequency of230Msample/sand 260 ADC ofMsample/s power consumptionwere 13.9mW and 17.8mW.

analog to digital converter(ADC);dual channel;pipeline;successive approximation register(SAR)

TN941.1

A

1005-9490(2016)04-0922-07

项目来源:广西教育厅高校科研项目(YB2014486);广西职业技术学院科研项目(141205)

2015-08-08修改日期:2015-09-09

EEACC:1265H;1290B10.3969/j.issn.1005-9490.2016.04.033