一种基于标准CMOS工艺实现的锁相环电路

2016-09-14鲍进华吕荫学曾传滨毕津顺罗家俊

鲍进华,吕荫学,李 博,曾传滨,毕津顺,罗家俊

(1.中国科学院 微电子研究所,北京 100029;2.中国科学院 硅器件技术重点实验室,北京 100029)

一种基于标准CMOS工艺实现的锁相环电路

鲍进华1,2,吕荫学1,2,李 博1,2,曾传滨1,2,毕津顺1,2,罗家俊1,2

(1.中国科学院 微电子研究所,北京 100029;2.中国科学院 硅器件技术重点实验室,北京 100029)

基于3.3 V 0.35 μm TSMC 2P4M CMOS工艺,设计并实现了一款高速锁相环电路。该电路的压控振荡器(VCO)采用环形结构,由电压-电流转换电路和差分延时环路组成,保证频率范围的同时也兼顾面积和相位噪声,版图面积只有0.03 mm2。测试结果显示,VCO输出频率范围为387.2~851.2 MHz。锁相环分频比为32,当输入信号为15 MHz时,VCO输出信号频率为480 MHz,其8分频输出信号在频偏1 MHz处的相位噪声为-118 dBc/Hz,时间间隔误差(Time Interval Error,TIE)抖动的均方根值为25.27 ps。

锁相环;压控振荡器;相位噪声;抖动

作为一种间接频率合成方法,锁相环应用非常广泛,包括存储器、微处理器、硬盘驱动电路、射频和无线收发器等领域[1-3]。集成电路的飞速发展使锁相环电路能够以较低的成本集成在芯片内部。片上集成锁相环可以根据一个低频率的输入信号产生一个同相位的高频信号,使高频信号仅集中于芯片内部,避免了芯片外部需要使用高频信号而产生的相互干扰[3]。然而,一般集成锁相环的实现依赖于片上的电感和电容,但电感和电容均属无源器件,需要占据较大面积,且工作在1GHz以下时,电感的品质因数低[4],因此性价比不高。鉴于此,本文将设计一种基于标准CMOS工艺实现的锁相环电路,该电路的压控振荡器由电压-电流转换电路和差分延时环路组成,既能保证频率范围,又能兼顾面积和相位噪声。

1 锁相环电路原理与电路设计

电荷泵型锁相环具有捕捉范围宽、捕捉时间短、最终稳态相位差为零和线性范围大等优点,成为了应用最为广泛的数模混合锁相环电路之一[5]。常见电荷泵型锁相环的结构如图1所示,基本组成模块包括鉴频鉴相器 (Phase Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、环路滤波器(Loop Filter,LPF)、压控振荡器(Voltage Controlled Oscillator,VCO)和分频器(Divider,DIV)。工作过程如下:PFD根据参考信号(REF)和反馈信号(FB)的频率和相位差值,控制输出信号UP或DN的使能,令使能时间与相位差值成正比;根据UP 或DN的使能时间,CP打开相应的充电或放电开关;LPF的作用是将CP的电流转换成电压,并滤除高频和杂波分量,产生一个较稳定的直流控制电压(Vc),以控制VCO的输出频率;VCO的输出信号经过DIV分频后产生FB,返回PFD的输入端,完成循环过程。整个系统属于负反馈系统,在其锁定范围内自动调节,最终使得FB与REF的相位差为0,控制电压Vc保持不变,VCO输出稳定的频率。

1.1VCO电路实现

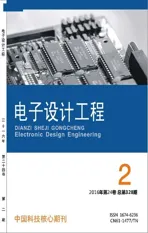

VCO是锁相环的核心模块,决定了其工作频率范围。文中设计的VCO如图2(a)所示,包括电压-电流转换电路[6]和由4级差分延迟单元组成的环形结构。

电压到电流的转换是通过M0、M1、R1和R2实现的。通过在输入管的源极添加负反馈电阻R1,极大地提高了转换的线性度。当Vc小于M0阈值电压时,R2保证转换电路的最小电流输出,决定VCO输出的最低频率。电流的输出利用共源共栅(M4、M5)和增益自举结构(M6)的电流镜,以达到增加输出电阻、保持电流恒定的目的。此外,锁相环中的控制电压具有一定的噪声[7],电压-电流转换电路能提供一个隔离作用,从而在一定程度上改善了VCO的相位噪声。

延迟单元采用差分负载实现,如图2(b)所示,能够抑制电源和衬底噪声,同时得到输出互补的差分信号。出于功耗和速度考虑,采用4级延迟单元。整个振荡器的输出频率由电流对延迟单元寄生电容的充放电时间来决定,通过调整电流镜的尺寸或延迟单元的尺寸能够实现对频率范围的调节,设计自由度大。对于设计好的振荡器,由于寄生电容变化不大,输出频率和电流成正比,电流则与控制电压成近似线性关系,因此能够实现控制电压对频率的线性调节。

图1 电荷泵型锁相环结构图Fig.1 Block diagram of Charge Pump PLL

图2 环形VCO电路原理图Fig.2 Schematic of proposed ring VCO

1.2分频器电路实现

分频器由5级D触发器级联而成,分频比固定为32。D触发器采用真单相时钟(True Single Phase Clock)结构实现[7],具有时钟负载小、工作速度快和功耗低等优点。但TSPC结构触发器是动态电路,需仔细设计器件宽长比才能保证功能的正确实现。

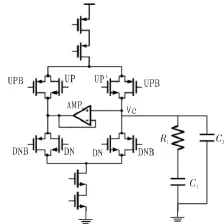

1.3PFD电路实现

PFD电路如图3所示,用于状态存储的触发器由两级RS锁存器构成。该触发器只检测输入信号的上升沿,对输入占空比并不敏感。PFD电路除了输出UP和DN外,还输出它们的互补信号UPB和DNB,传输门处于常开状态,用于匹配反相器的延时,使UP与UPB信号的延时尽可能相同。若REF和FB的时间差小于CP开关的开启时间,则由于电荷泵未能打开会导致锁相环环路无法响应此差值,形成所谓的“死区效应”。死区效应的消除是通过Buffer来实现的,Buffer由偶数级反相器组成,其延时大于电荷泵的开启电压,因此在任何时候PFD输出的脉宽都将大于电荷泵的延迟,从而避免死区效应。

图3 PFD原理图Fig.3 Schematic of PFD

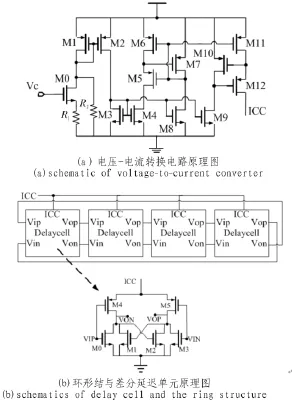

1.4CP与LPF电路实现

CP的功能是根据PFD的输出决定对LPF的充放电,进而改变控制电压。对CP的要求有两点:一是充放电电流的匹配,以减小锁定状态下CP对环路注入的噪声;二是恒流区尽可能宽,即在尽可能大的控制电压(Vc)变化范围内,电流镜都能在饱和区工作,保证输出电流的精度。CP电路如图4所示,电荷泵的电流由共源共栅电流镜提供,可增加输出阻抗,同时提高电流镜电流的精度,减小充放电电流的失配。采用互补CMOS开关管结构,同一时刻总是由同频同相的UP/DN 与UPB/DNB来控制开关管的导通,解决PMOS/NMOS开启时间不匹配带来的问题。电荷泵中的放大器用于复制控制电压,使左右电路对称,从而消除了CP电路的电荷共享效应。

LPF电路通常由无源器件实现,对整数型锁相环而言,其分频器产生的噪声较小,二阶滤波就已足够。LPF电路由图4中的R1、C1和C2组成,具体数值需综合考虑系统带宽、相位裕度和相位噪声等因素。由于在芯片内部集成无源器件需要较大的面积,文中将LPF安放在PCB板上,既节省芯片面积,也方便根据测试结果调整器件参数。

2 实验结果

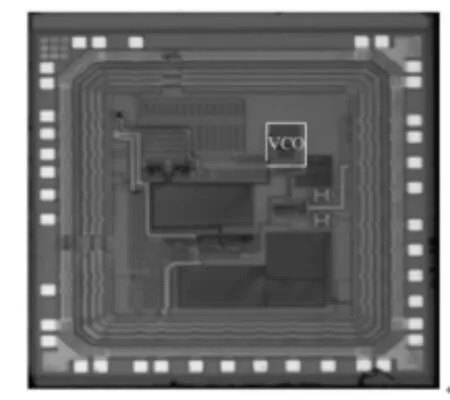

文中设计的锁相环是基于0.35 μm TSMC 2P4M CMOS工艺实现[9],芯片照片如图5所示,核心模块VCO电路面积只有0.03 mm2。

图4 CP和LPF电路原理图Fig.4 Schematic of CP and LPF

图5 锁相环芯片照片Fig.5 A micrograph of designed PLL

电路的工作电压为3.3 V,测试结果显示,PLL输出频率在48.4~106.4 MHz,由此推算VCO输出频率范围为387.2~851.2 MHz,输入参考信号频率范围为12.2~26.6 MHz。

当输入为15 MHz时,锁相环的锁定过程如图6(a)所示,锁定时间小于10 μs。输入信号和输出信号波形如图6(b)所示。由于锁相环的输入信号和输出信号通过不同的路径输入示波器内部,因此其边沿并没有完全对齐,但输出信号的频率则是输入信号的4倍,实现了倍频。

输出信号的相位噪声在1 MHz频偏处约为-118dBc/Hz,考虑到分频器对相位噪声的影响[10],实际VCO输出端相位噪声在-100 dBc/Hz左右。输出信号的时间间隔误差(Time Interval Error,TIE)抖动的均方根值为25.27 ps。

图6 输入25 MHz时Fig.6 Tested when input is 25 MHz

VCO是PLL的核心模块,对PLL的相位噪声起决定作用。与已有的研究成果相比,在输出频率相差不大的情况下,本文设计的VCO输出的相位噪声明显更优。

表1 VCO相位噪声对比Tab.1 Comparison of phase noise with other VCOs

3 结 论

文中设计了一种基于标准CMOS工艺实现的高速锁相环电路,电路中VCO利用电压-电路转换电路和差分延迟单元实现,保证频率范围的同时也兼顾面积和相位噪声[11]。VCO面积只有0.04 mm2,频率范围为387.2~851.2 MHz。在输入15 MHz方波时,锁相环输出为60 MHz时,其时间间隔误差(Time Interval Error,TIE)抖动的均方根值为25.27 ps。本文设计的锁相环电路具有工作频率范围大和调节方便的优点,可适用于时钟频率低于1 GHz的场合。

[1]Behzad Razavi.The Role of PLLs in Future Wireline Transmitters[J].IEEE Transactions on Circuits and Systems,2009,56(8):1786-1793.

[2]姚婧婧,赵红东,毛键,等.锁相环中压控振荡器的分析与设计[J].电子设计工程,2011,19(19):177-180.

[3]吕荫学,刘梦新,罗家俊,等.一种高性能鉴频鉴相器的设计[J].半导体技术,2013,37(7):538-543.

[4]杨力,蒋春敏,荆友枫.一种基于0.35 μm CMOS工艺的1.2 GHz锁相环[J].微电子学,2009,39(4):496-498.

[5]谢连波,桑红石,方海涛,等.低功耗CMOS差分环形压控振荡器设计[J].微电子学与计算机,2013,30(5):104-107.

[6]吕荫学,刘梦新,罗家俊,等.一种1 GHz多频带压控振荡器的设计[J].微电子学与计算机,2013,30(2):1-5.

[7]王文理,张霞.基于FPGA的全数字锁相环的设计[J].电子设计工程,2009(1):39-40.

[8]Yuan J,Svensson C.New Single-Clock Latches and Flipflops with improved speed and power savings[J].IEEE Journal of Solid-state Circuits,1997,32(1):62-69.

[9]陈剑,杨银堂.CMOS图像传感器研究[J].电子科技,2007 (9):17-21.

[10]蔡志明,陈莹梅,李智群,等.GPS射频接收芯片中低功耗压控振荡器的设计[J].微电子学,2009,39(6):790-792.

[11]张海明.频率源的相位噪声特性分析 [J].无线电通信技术,1999(1):25-27.

Implementation of a PLL based on standard CMOS process

BAO Jin-hua1,2,LV Yin-xue1,2,LI Bo1,2,ZENG Chuan-bin1,2,BI Jin-shun1,2,LUO Jia-jun1,2

(1.Institute of Microelectronics,Chinese Academy of Sciences,Beijing 100029,China;2.Key Laborator of Silicon Devioe Technology,Chinese Acaokmy of Science,Beijing 100029,China)

A novel PLL based on standard CMOS process was designed and fabricated.The PLL utilizes a novel ring voltage controlled oscillator(VCO)consisting of a voltage-to-current convert circuit and four stages of delay cell.Measured output frequency of the VCO is 387.2~851.2 MHz.With a 15 MHz input signal,the PLL outputs a 60 MHz signal,of which phase noise is around-118dBc/Hz@1 MHz offset and rms jitter of TIE(Time Interval Error,TIE)is 25.27ps.

PLL;VCO;phase noise;jitter

TN432

A

1674-6236(2016)02-0090-03

2015-03-26稿件编号:201503383

国家自然科学基金项目(11179003,61176095)

鲍进华(1989—),男,河南信阳人,硕士研究生。研究方向:高可靠性锁相环电路设计。