飞思卡尔S12X系列单片机协处理器的应用

2016-09-13吴成加安徽安凯汽车股份有限公司合肥230051

吴成加,徐 川(安徽安凯汽车股份有限公司,合肥 230051)

飞思卡尔S12X系列单片机协处理器的应用

吴成加,徐川

(安徽安凯汽车股份有限公司,合肥230051)

介绍飞思卡尔16位微处理器S12X(E)系列单片机协处理器(XGATE)的基本特性、中断及优先级设置、代码在RAM中运行、信号量的互锁,以及利用其实现CAN信息中断接收的应用实例,从而减轻CPU的负担以增强汽车电子软件系统的数据吞吐能力。

飞思卡尔单片机;协处理器;XGATE;S12X系列

与S12系列微处理器相比,Freescale公司推出的S12X(E)系列16位微处理器的性能有全面的提升。HCS12X系列单片机是HCS12系列的增强型产品,基于S12 CPU内核,增加了172条指令,可以执行32位运算,总线频率最高可达50 MHz,并且改进了中断处理能力[1]。以汽车电子产品开发应用中广泛使用的MC9S12X EQ512为例,该处理器集成了中断控制器,具有丰富的寻址方式。有7个中断优先级,并且内核支持优先级的调度,最多可以有120个中断源。其最大特点是增加了一个并行处理的外围协处理器XGATE模块,下面主要介绍其基本特性及具体应用。

1 XGATE的基本特性

XGATE是一个独立于主处理器(CPU12X)的可编程RISC内核,可作为一个高效的DMA控制器使用,能够自主地实现外设与RAM之间的高速数据传输,或在数据传送的过程中进行灵活的数据处理,同时将处理的结果放在XGATE和主核共享RAM区变量中,以实现CPU12X和XGATE之间共享数据。它还可以作为一个单独的算法单元完成某些运算,如通信协议的处理等[2]。

XGATE的16位的精简指令集内核,拥有8个16位通用寄存器R0~R7,1个程序计数器PC,1个4位的条件码寄存器CCR,其中R0恒为0,可用于对变量的快速清零或置位。R1为数据指针寄存器,R7为堆栈指针寄存器。XGATE响应中断时,硬件将中断向量表中对应通道的1个16位字装载到R1(通常用做数据指针),将栈指针装载到R7。

XGATE共有72条独立的指令,指令时钟最高可达100 MHz,其大部分指令是对通用寄存器的操作,为单周期指令。访问存储器的指令为双周期指令。跳转指令视条件而定可能为1或2个周期指令。XGATE有一些特殊的比特提取及插入的单周期指令,特别适用于串行通信协议使用。

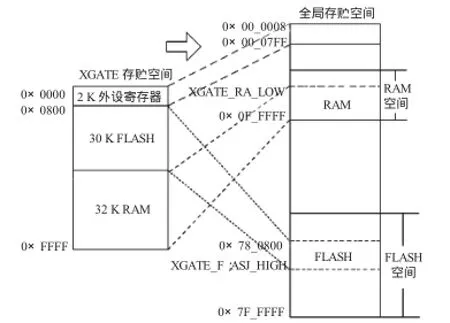

如图1所示,XGATE最多可以访问处理器内部的64 KB空间。这64 KB空间包括2 KB片上外设寄存器、30 KB的FLASH空间(最低地址0x780800向上延伸的30 KB FLASH空间)、最大 32 KB的片内 RAM (0x0F8000~0xFFFFF)。片内的EEPROM空间或片外资源XGATE无法访问。XGATE的访问内存空间完全包含在HCS12X主处理器CPU12X的访问空间之内。地址仲裁的规则是,HCS12X主处理器的优先级总是高于XGATE。在实际的代码运行过程中,HCS12X主处理器CPU12X的代码在FLASH中运行,若XGATE的代码也在FLASH中运行,有可能会导致总线冲突。此外,XGATE的运行速度较HCS12X主处理器CPU12X要高,XGATE的总线频率是HCS12X主处理器CPU12X的两倍[1]。

图1 XGATE存储空间地址映射

XGATE的代码执行是由中断事件驱动的,通过产生中断来触发XGATE运行。当没有中断时,XGATE不执行任何指令,也没有功耗。XGATE的代码就相当于是一组中断服务程序,没有主程序或空闲时的循环程序。XGATE的中断服务程序也称线程。

主处理器CPU12X与XGATE之间常用的通信方式是共享资源。由于这两个内核都可以独立异步地访问内存及片上外设,这就会产生数据完整性问题。为了保证共享数据的完整性,XGATE集成了8个硬件互斥信号量(Semaphore)。用户可以通过硬件信号量来同步两个内核对共享数据的访问。信号量有3种状态:释放、主处理器CPU12X锁定和XGATE锁定。每个内核在访问共享资源前,应当首先锁定相应的信号量;在访问结束后应当释放相应的信号量[3-5]。

2 XGATE的应用

设计人员在新建项目工程文件时(如车身电子控制单元、数字组合仪表、发动机电控单元等),可以在XGATE Setup选项中选择 Multi Core(HCS12X and XGATE)项,即可在工程文件中,使用XGATE功能模块,反之,当选择Single Core(HCS12X)项时,则不使用XGATE功能模块,由于HCS12X和XGATE的指令集不同,CodeWarrior用两个编译器分别对 CPU12X和XGATE的代码进行编译,编译的代码要分别放在.c和.cxgate的文件中,需要XGATE执行或调用的所有代码都必须要放在工程文件中的xgate.cxgate文件中。

2.1XGATE的中断及优先级设置

MC9S12XEQ512中包括预留的中断一共有120个中断位,对中断优先级寄存器的分配,系统采用分组设置的方法,将120个中断分为15个组,每组8个中断。设置中断时,先将需要的组别设置到相应的寄存器,再设置8个中断优先级寄存器的某一个,即可完成中断的设置。中断的优先级共划分为七个中断优先级,每一个中断源都有一个可以设置的级别,同一优先级的中断同时触发时,高地址(中断号较小)的中断先响应。分组的规则是这样的:中断地址位7到位4相同的中断为一组,比如MC9SXEQ512.h中,Vcan0tx、Vcan0rx、Vcan0err、Vcan0wkup、Vflash、Vflashfd、Vspi2、Vspi1为不同的中断向量,其地址定义分别为0xFFB0U、0xFFB2U、0xFFB4U、0xFFB6U、0xFFB8U、0xFFBAU、0xFFBCU、0xFFBEU。

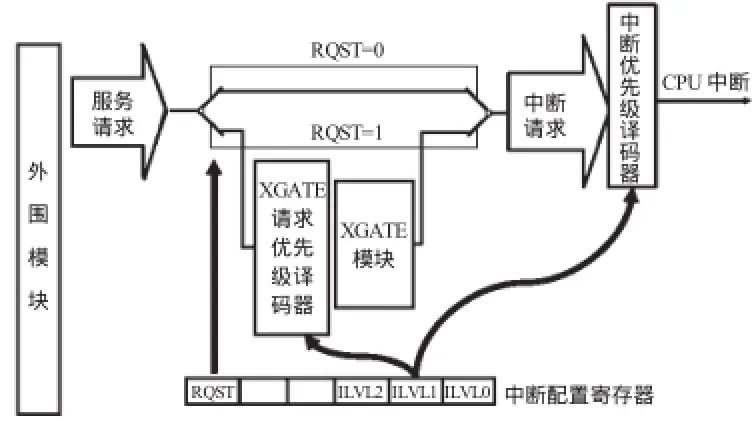

这些中断的位7到位4都为B,它们就被分成了一组。中断向量表从1~F正好15个组。用来设置组别的寄存器可通过INT_CFADDR寄存器来进行设置,如图2示。

图2 中断组配置地址寄存器

需要设置某个组别的中断时,只要写入最后8位地址就行了,比如设置Vcan0rx的中断优先级,就写入0xB2即可。HCS12X的中断既可以运行在内核CPU12X中,也可以运行于XGATE中,中断的选择可以通过INT_CFDATA0-7的RQST位来进行选择,当RQST置为1时,选择中断服务程序在XGATE中运行,反之则选择中断服务程序在HCS12X处理器中运行,如图3所示[6]。

图3 XGATE的中断配置及中断响应示意图

设置好组别之后,需要对中断优先级和中断寄存器进行设置,INT_CFDATA0-7的[2:0]位为该中断的优先级选择位,中断优先级为0~7。向INT_CFDATAx低地址中写入0~7就能设置相应的中断优先级。

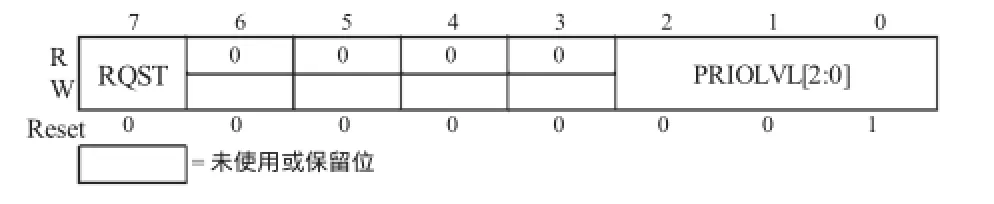

图4所示的是某一组中断寄存器INT_CFDATA0~INT_CFDATA7,一共有8个,每个都代表中断组中的一个中断。中断寄存器的设置规则是,该中断地址的低4位除以2,比如设置Vcan0rx的中断向量为0xB2,它的低4位为2,除以2后为1,那么我们就需要对INT_CFDATA1进行设置,假如Vcan0rx的中断优先级设为1,我们向INT_CFDATA1的[2:0]位写入1即可。

图4 中断请求配置及优先级选择

2.2XGATE的中断代码的运行

如果CPU12X、XGATE运行的代码都放在FLASH中,两者都访问总线时,就有可能造成总线冲突。CPU12X访问片内RAM时只占用总线带宽的一半,为了降低总线冲突的概率,同时增加系统的运行效率,设计人员经常会将XGATE的代码放在RAM中运行,这样在每个CPU12X的RAM访问周期中,总能让出一个XGATE的RAM访问周期。要实现上述功能,设计人员需要对XGATE的代码重定位,即将中断代码从XGATE_CODE_FLASH段重新定义到XGATE_CODE _RAM段。

XGATE在FLASH中的地址映射在工程文件的Prm文件中,XGATE在FLASH中的空间映射如下。其中XGATE存储空间的 2 KB外设寄存器(0x00000~0x007FF)直接对应FLASH全局地址的0xE08000~0xE087FF;30 KB的FLASH空间共划分为两块,低地址14 KB存储空间PAGE_E0映射到FLASH全局空间的0xE08800~ 0xE0BFFF、高地址 16 KB存储空间PAGE_E1映射到 FLASH全局空间的 0xE18000~0xE1BFFF位置。

PAGE_E0_0=READ_ONLYDATA_FAR IBCC_FAR 0xE08000 TO 0xE087FF;//不映射到XGATE;PAGE_ E0=READ_ONLY DATA_FAR IBCC_FAR 0xE08800 TO 0xE0BFFF ALIGN 2[1:1];//PAGE_E0空间映射,PAGE_ E1=READ_ONLY DATA_FAR IBCC_FAR 0xE18000 TO 0xE1BFFF ALIGN2[1:1];//PAGE_E1空间映射。

XGATE在RAM中的空间映射如下,在该工程中,处理器RAM最大空间为32 KB,XGATE对其中24 KB RAM空间进行映射,XGATE存储空间中的地址范围为0x8000~0xFFFF;在Prm文件中将RAM划分为6块,每个RAM块为4 KB,映射到RAM空间中对应的地址分别 为 0xF81100~0xF81FFF、0xF91000~0xF91 FFF、0xFA1000~0xFA1FFF、0xFB1000~0xFB1FFF、0xFC1000 ~0xFC1FFF、0xFD1000~0xFD1FFF。

在系统中XGATE代码默认是指向PAGE_E0、PAGE_E1位置,即XGATE_CODE_FLASH段,只需要将其重新定义到RAM_F8、RAM_F9、RAM_FA、RAM_FB位置,XGATE_CODE_RAM即可实现CODE_SEG段代码在RAM中运行。图5中显示了同一段代码分别在FLASH(左侧)中和RAM(右侧)中运行的地址映象。当XGATE_CODE在FLASH中运行时,仿真停止后它的指令指向地址为0xE08xxxFLASH空间;而在RAM中运行时,仿真停止后它的指令指向地址空间为0xF81xxx的RAM空间。

图5 XGATE CODE在FLASH和RAM中运行汇编代码

2.3XGATE的信号量互锁

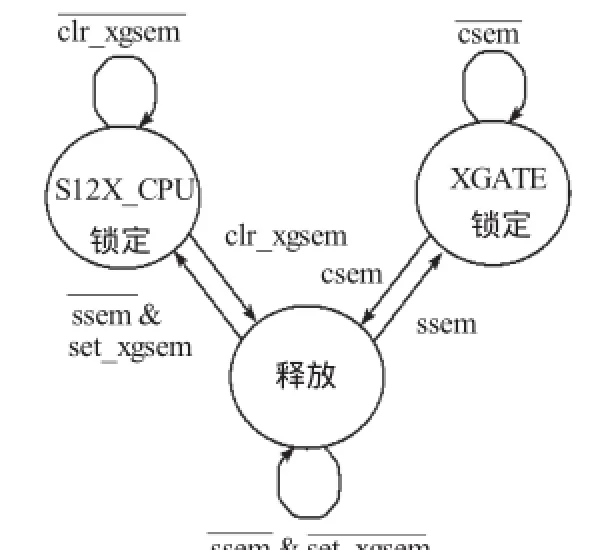

CPU12X与XGATE之间通信方式是通过资源共享实现数据交互。由于两个内核都可以随时独立访问内存和片上外设,这样就会产生数据的完整性问题。为了保证数据的完整性,XGATE集成了8个硬件互斥信号量(Semaphore)。系统可以通过硬件信号量同步两个内核对共享数据的访问。信号量有3种状态,即释放、CUP12X锁定、XGATE锁定。每一个内核在访问共享数据之前,首先对相应的信号量进行锁定,在访问结束后释放该信号量。信号量在三种状态之间进行转换,如图6所示,XGATE通过ssem加上一个3 bit立即数来锁定或释放某个信号量,CPU12X通过信号量寄存器XGSEMG来锁定或释放某个信号量[7]。

图6 信号量状态转换

2.4XGATE的应用实例

假如要通过XGATE对汽车总线上的CAN信息(如电流、温度、压力、扭矩、速度等信息)进行接收,并将接收到的数据放入到CPU12X和XGATE共享的RAM变量中,可以在RAM共享区中定义一组变量。该组变量在运行过程中,两个内核都可以访问它。

然后对XGATE及中断进行配置。在初始化XGATE模块中,开通了两个中断源,其中一个PIT0中断处理函数位于CPU12X的代码中,中断优先级设为2,CAN0接收中断运行在XGATE中,中断优先级为1。

static void SetupXGATE(void)

{//初始化块和XGATE向量设置XGVBR寄存器的起始地址

XGVBR=(unsigned int)(void*__far)(XGATE_VectorTable-XGATE_VECTOR_OFFSET);

ROUTE_INTERRUPT(PIT0_VEC,0x02);//运行在CPU12X内核中

ROUTE_INTERRUPT(CAN0RX_VEC,0x81);//运行在XGATE内核中

XGMCTL=0xFBC1;//使能XGATE模块和中断

}

最后要初始化XGATE中断向量表以指向函数。XGATE向量表是完全独立于CPU的向量表,有两个项,分别服务于每一个向量。第一个项是指向中断函数的指针,如CAN0中断的服务函数CAN0RX_XSR();第二个项是当发生中断时将被传递的参数值,如下所示:

const XGATE_TableEntryXGATE_VectorTable[]={

{ErrorHandler,0x09},//通道9-保留

……

{CAN0RX_XSR,0x59},//通道59-CAN0接收中断

……

{ErrorHandler,0x79},//通道79-IRQ中断};

3 结束语

实践证明,XGATE通过一些特殊的比特提取及插入的单周期指令,特别适用于串行通信协议使用。协处理器可以独立异步地访问内存及片上外设,在系统应用中可减轻主处理器CPU12X的负担,以增加系统的数据吞吐能力;访问RAM方面XGATE也有其自己的优势,在单片机及嵌入式系统开发中,展现出其独特的优势。

[1]飞思卡尔9S12X系列双核中的协处理器XGATE使用方法[DB/OL].电子工程世界,2012.[2016-01-15].http://download. eeworld.com.cn/detail/Timson/1504.

[2]张阳.单片机原理及嵌入式系统开发[M].北京:电子工业出版社,2011.9.

[3]张阳,吴晔,滕勤.MC9S12XS单片机原理及嵌入式系统开发[M].北京:电子工业出版社,2011.9.

[4]王威.HCS12微控制器原理及应用[M]北京:北京航空航天大学出版社,2007.

[5]邵贝贝.单片机嵌入式应用的在线开发方法[M].北京:清华大学出版社,2004.10.

[6]Freescale Company.MC9S12XEP100 Reference Manual CoversMC9S12XE Family[DB/OL].[2016-01-15].http://cache.free scale.com/files/microcontrollers/doc/data_sheet/MC9S12XEP100 RMV1.

[7]Freescale Company.How to Configure and Use the XGATE on S12X Devices[DB/OL].[2016-01-15].http://cache.nxp.com/files /microcontrollers/doc/app_note/AN2685.pdf?fsrch=1&sr=2&pageNum=1.

修改稿日期:2016-02-01

Application of Freescale S12X Series Microcomputer Coprocessor

Wu Chengjia,Xu Chuan

(Anhui Ankai Automobile Co.,Ltd,Hefei 230051,China)

The authors introduce the basic characteristics,interrupt and prioritysetting,code operation in RAMand signal interlockingofthe Freescale 16-bit microprocessor series S12X(E)single chip processor(XGATE).Theyalso present the application instance ofusingcoprocessor implementation CAN information interrupt receivingin order to reduce the burden ofCPUand enhance the data throughput ofthe vehicle electronic software system.

Freescale micro-computer;coprocessor;XGATE;S12Xseries

U463.6

B

1006-3331(2016)04-0055-04

吴成加(1971-),男,工程师;研究方向:新能源汽车电驱动及控制系统核心零部件关键技术研究。