基于FPGA的双CF卡数据采集系统设计

2016-09-12夏光辉秦建军王大成

夏光辉,秦建军,王大成

(1.91550部队93分队,辽宁 大连 116023;2.哈尔滨工程大学 水声技术国防科技重点实验室,黑龙江 哈尔滨 150001)

基于FPGA的双CF卡数据采集系统设计

夏光辉1,秦建军2,王大成2

(1.91550部队93分队,辽宁 大连 116023;2.哈尔滨工程大学 水声技术国防科技重点实验室,黑龙江 哈尔滨 150001)

在FPGA内部建立以Nios II软核为核心的片上控制系统,在保留FPGA并行处理优势的前提下,增强设计的灵活性;利用双CF卡做为存储介质,系统始终保证一张卡处于被写状态,另一张卡处于可读或可取下状态,实现对数据的不间断存储;通过移植广泛使用的FAT32文件系统,解决CF卡内数据的高效管理问题;采用USB2.0接口将CF卡中的数据上传给计算机。实测结果表明,系统可以长时间稳定工作于黑匣子记录模式。该设计方案在需要不间断记录数据的应用中广泛适用。

FPGA;Nios II;CF卡;FAT32;USB

随着信息技术的发展,对数据采集存储系统的需求越来越多。如何实时、连续地采集和存储数据已成为备受关注的问题[1-2]。随着超大规模集成电路制造工艺的不断提高,以FPGA为代表的可编程逻辑器件为数据采集系统设计提供了全新的思路[3-4]。本文正是利用FPGA器件并行处理能力强、功能可裁剪等优势[5-6],结合CF卡工作稳定、访问速度快的特点[7],提出了一套可运行在乒乓模式下的双CF卡数据采集存储系统实现方案。该方案特别适用于需要不间断记录数据的应用场合。

1 系统硬件设计

参见图1,系统由A/D模块、控制模块、存储模块和USB接口模块4个功能模块构成。

A/D以12bit二进制补码形式输出数据给FPGA;FPGA首先利用内建的FIFO对数据进行缓存,再通过可编程片上系统[8-9](SOPC)的CF控制模块将缓存后的数据写入CF卡,实现数据存储;当一个CF卡数据存满后,总线开关在FPGA的控制下实现在两个CF卡间的切换。与FPGA相连接的CF卡处于写状态;与USB接口芯片相连接的CF卡处于可读状态。在可读状态下的CF卡可以直接取下,进行更换。

图1 系统结构图Fig.1 System block diagram

CF卡与FPGA的连接如图2所示。

2 系统软件设计

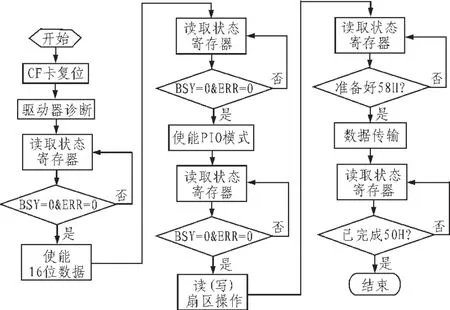

图3给出了系统的工作流程。系统上电后,FPGA首先完成程序自举引导和初始化操作,之后开始数据采集,每当数据缓冲完成,则将数据写入CF卡。数据存储功能的实现是FPGA程序的最主要部分,它不仅涉及SOPC的配置、CF4.0协议的实现,还包括FAT32文件系统的建立和管理[10]。图4给出了CF卡在PIO模式下的数据传输流程图。

图2 CF卡与FPGA连接电路图Fig.2 Connection schematic of CF card and FPGA

图3 系统整体工作流程图Fig.3 Overall system flow chart

图4 PIO模式传输实现流程图Fig.4 PIO mode transmission flow chart

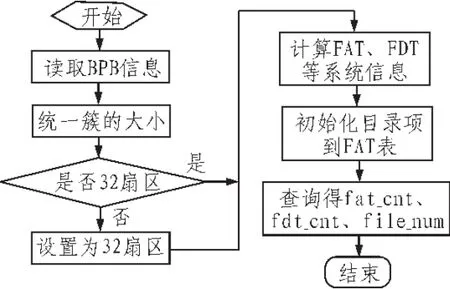

在完成CF卡扇区读写控制的基础上,实现数据按照FAT32文件格式存储要经过以下五个步骤:文件系统初始化、新建文件操作、修改目录项操作、申请空闲簇操作和添加文件内容操作。图5~7给出了其中几个关键操作的流程图。

程序首先读取CF卡的启动扇区,获得参数信息,并由此计算出FAT表的起始扇区、系统总扇区数和总簇数,再修改2~10号簇的FAT表项将其分配给根目录并构成簇链,然后通过查询FDT和FAT表获得当前目录项在根目录区的位置(fdt_cnt)和文件数(file_num)信息、以及最后分配的簇在FAT中的位置(fat_cnt)。

图5 文件系统初始化Fig.5 File system initialization

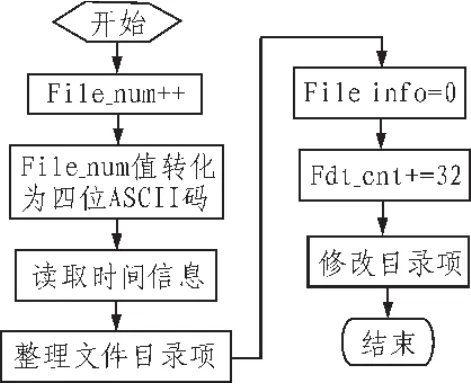

图6 新建文件Fig.6 Create new file

图7 添加文件内容Fig.7 Add the contents of the file

系统采用短文件名的方式存储目录项信息,以32个字节为单位进行目录文件所占簇的分配。通过新建文件操作时获得的根目录区位置,计算出新建文件目录项在根目录中的簇地址、扇区地址和偏移地址信息;再判断簇地址是否超出根目录分配的簇地址,如果超出则说明没有空间记录新建文件目录项信息;根据之前得到的簇地址和扇区地址读取新建目录项所在扇区,修改新建目录项信息并写入该扇区,最终完成目录项建立操作。

为了提高CF卡写卡的速度,减少申请空闲簇的频率,所以在每次申请空闲簇时连续申请50个新簇(最大可申请簇数127个),对应大小为50×16 kB=800 kB,这样只要申请10次就能完成一个文件数据的写入工作;然后判断申请新簇后的根目录区位置有没有超出系统总簇数,若超出说明没有足够的空间存储数据,需要切换CF卡;如果没有超出则由根目录区位置计算出新FAT表项所在FAT表中的簇地址、扇区地址和偏移地址信息;读取根目录区位置所在扇区,判断所申请的50个新簇是否都在一个扇区,如果不在同一个扇区,则需要修改剩余簇号在上一扇区FAT表中的表项信息。

每次申请空闲簇的最后一簇时都写入结束标记,所以要判断是否是新建文件。如果不是新建文件,则要修改上一次申请空闲簇时,对应最后一簇的结束标记信息,使文件构成一个完整的簇链。将50或51个簇对应FAT表的表项信息修改完成后,写入FAT表中完成空闲簇申请操作。

新建文件的目录项默认没有给新文件分配起始簇号,所以对于新文件在添加内容时,要记下首簇号并修改文件目录项中对应首簇地址。空闲簇申请完成后,修改文件目录项中文件的大小,将更新后的文件目录项信息写入文件所在根目录扇区中,最后根据申请的50个空闲簇号获得每个簇地址所在的首扇区地址,循环写入数据。

经过上述5个步骤,就可以在CF卡内建立FAT32文件系统,实现数据写入。

3 系统功能测试与结果分析

3.1 采集功能测试

FPGA产生A/D采样转换和使能信号,同时打开异步FIFO的写数据使能信号,将模数转换后的数据连续地送入异步FIFO中进行缓存。程序不断检测当前写入FIFO的数据总量,如果写入数据深度达到16kB则使能读数据中断信号。SOPC检测到上述中断信号后产生读数据时钟,在每个时钟下降沿读取异步FIFO中的数据,当FIFO被读空时,禁止读使能信号。由于读时钟是写时钟的N倍(N远大于1),所以对异步FIFO的访问没有用到写满或读空标志位。

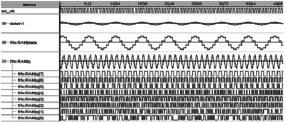

在Signal Tap II[11]中观测FIFO中的数据波形,如图8所示。其中ad_clk为A/D采样频率(1 MHz);datain1是A/D转换后采集到的12bit二进制补码;FIFO:RAM|q是经过异步FIFO缓冲后读取的数据。FIFO缓冲区的建立,为数据的连续不间断存储创造了条件。由图可知:在datain1的每一个周期内都有10个采样点,满足10倍采样率的设计要求。与输入测试信号比较,采集获得的信号正确。

图8 FIFO中的数据Fig.8 Data in the FIFO

3.2 存储功能测试

数据存储介质采用两张闪迪(San Disk)公司推出的CF卡,其容量分别为4 GB、8 GB,均支持PIO和UDMA模式。

1)FPGA写CF卡速度测试

为了测试到FPGA最大的写卡速度,数据由FPGA内部产生,保证测试结果不受数据源速度的影响。另外CF卡的操作模式为PIO模式2,它的理论最大写入速度为8.33 MB/s。

在FPGA对CF卡进行读写操作的时钟频率为100 MHz,数据传输位数为16 bit,写入单个文件大小为15.625 MB情况下,通过测量连续写入200个相同文件大小的总字节数和消耗的总时间,计算出FPGA平均写卡速度。由于采用手工测试,故存在测量误差,但误差能够控制在5 kB/s以内。

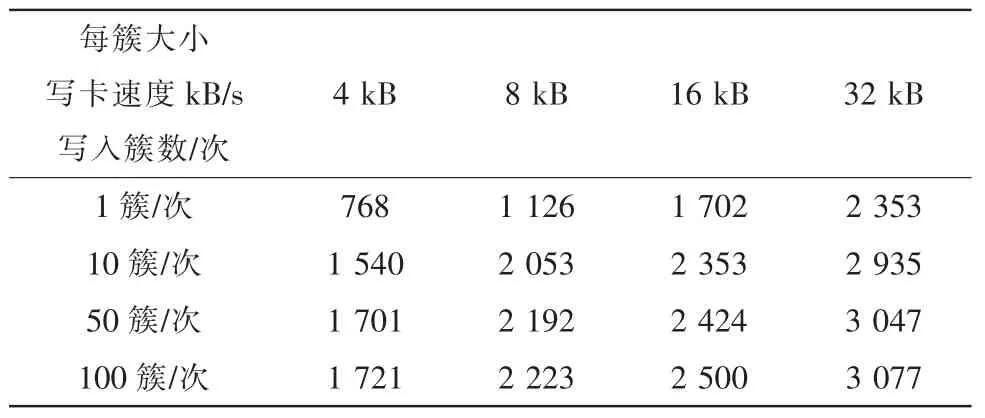

表1 FPGA写卡速度测试结果Tab.1 FPGA write speed test results

由测量结果可知:①簇的尺寸越大,其写入速度越快(FAT32文件系统中每簇最大只能为32 kB);②在簇尺寸相同的情况下,每次写入簇数越多,写卡速度越快,但并构成线形关系,当簇数多到一定量时,单一增加簇数对数据写入速度的提升不明显。

2)USB接口读写CF卡速度测试

通过计算机,选用USB传输速度测试软件ATTO Disk Benchmark测试系统读卡模块。设定传输文件大小从0.5 kB 到8 192 kB,总长度为256 MB。测试结果如图9所示,其中实线为读卡速度曲线,虚线为写卡速度曲线。在文件大于64 kB时,读写卡速度均超过15 MB/s,接近读卡模块选用的AU6371芯片[12]提供的最优性能。

图9 USB接口读写速度测试结果Fig.9 USB interface to read and write speed test results

4 结 论

本文给出了一种基于FPGA的数据采集系统设计方案。方案中FPGA通过内建的Nios II软核实现对两片CF卡的FAT32格式文件管理。依该方案实现的硬件系统经测试,能够实现预期的数据采集和存储功能,且工作稳定。

[1]董超群,董芳,等.海洋水文气象综合数据采集器的研制[J].电子设计工程,2012,20(3):7-9.

[2]杨进,文玉梅.采用复合磁电换能器的宽带振动能量采集器[J].仪器仪表学报,2012,33(12):2863-2868.

[3]石繁荣,黄玉清.基于FPGA的主从式高速数据采集与传输系统[J].电子技术应用,2011,37(5):82-85.

[4]储成君,任勇峰.基于FPGA的多通道信号采集电路设计[J].科学技术与工程,2013(13):5692-5701.

[5]杨海钢,孙嘉斌.电子与信息学报.FPGA器件设计技术发展综述[J].2010,82(8):714-728.

[6]许芳,席毅.基于FPGA/Nios-Ⅱ的矩阵运算硬件加速器设计[J].电子测量与仪器学报,2011,25(4):377-382.

[7]刘旺,王启.一种大容量并行采集系统实现方法[J].测控技术,2010,29(10):38-41.

[8]吴建平,叶玉堂.基于SOPC高速图像实时处理技术研究与实现[J].光电工程,2011,38(8):124-128.

[9]孟芳,于立佳.基于NiosII的SOPC系统设计分析[J].无线电通信技术,2012,38(1):73-76.

[10]夏昀.基于FAT32文件系统的安全存储方案[J].信息技术,2013(5):97-101.

[11]张帅,王典洪.基于Nios II软核的双网卡路由选择[J].现代电子技术,2005(14):34-40.

[12]AU6371-JDL USB2.0 Single LUN Multiple Flash Card Reader Controller Technical Reference Manual[Z].Alcor Micro,Corporation,2007.

Design of dual CF card data acquisition system based on FPGA

XIA Guang-hui1,QIN Jian-jun2,WANG Da-cheng2

(1.Unit No.93,Troop 91550,Dalian 116023,China;2.National Laboratory of Underwater Acoustic Technology,Harbin Engineering University,Harbin 150001,China)

In order to enhance design flexibility while retaining the advantages of FPGA parallel processing,an internal control system is established on the FPGA by using the NiosII soft-core.Two CF cards as the storage medium are used to achieve continuous data storage that is always ensure that a card is being written state,another card is readable or removable state;FAT32 file system is widely used by transplant to solve the problem of data management efficiently in CF card.Data in CF card can is uploaded to the computer by USB2.0 interface.The actual test results show that the system can run stability in a long time in the black box recording mode.The design is widely available in many applications that continuous recording data is required.

FPGA;Nios II;CF card;FAT32;USB

TN911.7

A

1674-6236(2016)04-0019-03

2015-02-06 稿件编号:201502062

夏光辉(1977—),男,湖南益阳人,工程师。研究方向:水下测量技术。