基于ARM的双冗余微小型无人机飞行控制系统的设计

2016-09-08雷金奎原丹丹李海生

雷金奎,原丹丹,李海生

(1.西北工业大学 第365所,陕西 西安 710065;2.西北工业大学 电子信息学院,陕西 西安 710072)

基于ARM的双冗余微小型无人机飞行控制系统的设计

雷金奎1,原丹丹2,李海生2

(1.西北工业大学 第365所,陕西 西安 710065;2.西北工业大学 电子信息学院,陕西 西安710072)

为了提高微小型无人机飞行控制系统的可靠性和安全性,开发了一种基于ARM的双冗余飞行控制系统,完成了以处理器为核心的功能模块级双冗余设计,并详细介绍了系统的软硬件设计。通过建立可靠性模型对系统可靠性进行了定量分析,结果表明,该系统的可靠性得到了提高。

ARM;无人机;双冗余;飞行控制系统

无人机是一种有动力、可控制、能携带多种任务设备、执行多种任务,并可重复使用的无人驾驶航空飞行器[1]。与传统的载人飞机相比,它具有体积小、造价低、使用方便、反应快速、机动灵活、对任务环境要求低、生存能力强等优点,鉴于其独有的优势,无人机的应用范围已拓宽到军事、科研和民用三大领域[2]。

近年来,随着各种航空和电子技术的发展,使无人机在性能上得到突飞猛进的发展。随着无人机飞行功能的日益增多,任务要求越来越复杂,使飞行控制系统变的越来越复杂,从而出现故障频率也越来越高。飞行控制系统一旦发生故障,那么极有可能发生坠机事件,造成很大损失。因此设计具备高容错能力和高可靠性的余度飞行控制系统已成为必然的趋势。

ARM处理器具有功耗低、体积小、性能高,价格低,接口资源丰富,控制能力强等优点,选用ARM处理器进行开发,技术积累性较强,生命周期长,设计重用度高,不易被淘汰。因此本文提出一种基于ARM的双冗余无人机飞行控制系统的设计,实现故障诊断、故障隔离以及故障时的动态重构,提高了无人机飞控系统的可靠性和安全性。

1 系统工作原理

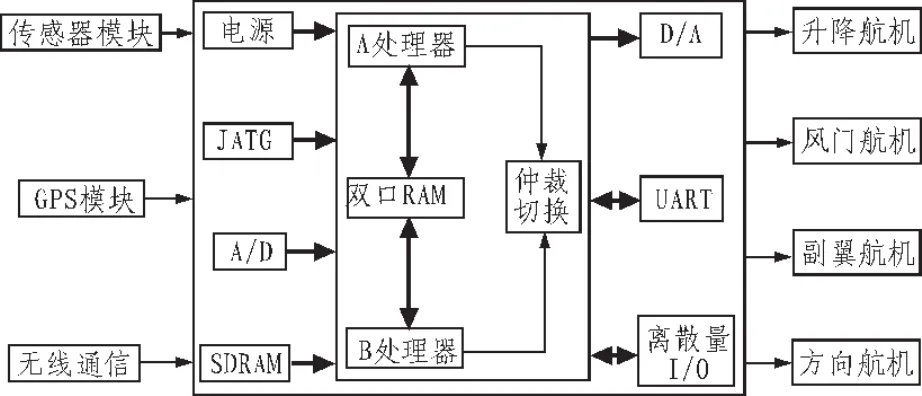

双冗余飞行控制系统主要完成的功能有:1)对传感器采集来的信号进行调理、转换后一分为二分别送入A处理器(主机)和B处理器(副机);2)A、B处理器分别对采集来的数据进行分析,完成控制律解算;3)仲裁切换电路根据主机和副机的状态标志确定输出主机(或副机)解算出的姿态角等控制量,保证无人机的平稳飞行。双冗余飞控平台的总体设计框图如图1所示。

图1 双冗余飞行控制系统的总体设计框图Fig.1 Structure diagram of dual redundant flight control system

双冗余飞行控制系统采用SAMSUNG公司的ARM9处理器S3C2440作为A、B处理器,主频可达400 MHz,外扩64MB的SDRAM作为内存。8路12位的A/D、D/A模块完成模拟量与数字量的转换,7路串口通信可完成RS232、RS422、RS485不同标准的任务设备与处理器之间的通信,30路离散量I/O可设置输入输出。

2 系统硬件设计

2.1A/D转换

ARM芯片需要数字信号的输入,传感器输出的模拟信号经滤波后,必须经过A/D转换才能作为输入。S3C2440自带8 路A/D通道,分辨率为10位,不能达到所要求指标,需要外接A/D模块。A/D转换的芯片选取ADC128S052芯片,具有8 路A/D通道,分辨率为12位。ADC128S052通过SPI总线与S3C2440连接,SPIMOSI为S3C2440的数据输出,SPIMISO为S3C2440的数据输入,SPICLK为时钟信号,nSS0为使能信号,由S3C2440控制。

2.2D/A转换

经过S3C2440进行解算后,需要一个D/A转换电路输出模拟量来控制执行机构。为确保输出信号不失真,D/A芯片与A/D芯片的分辨率应保持一致,均为12位,输出电平信号的范围为0~3.3 V。D/A转换芯片选用TI公司的DAC7678,它具有8路D/A通道,分辨率为12位。DAC7678与S3C2440通过I2C总线连接。

2.3双处理器通信设计

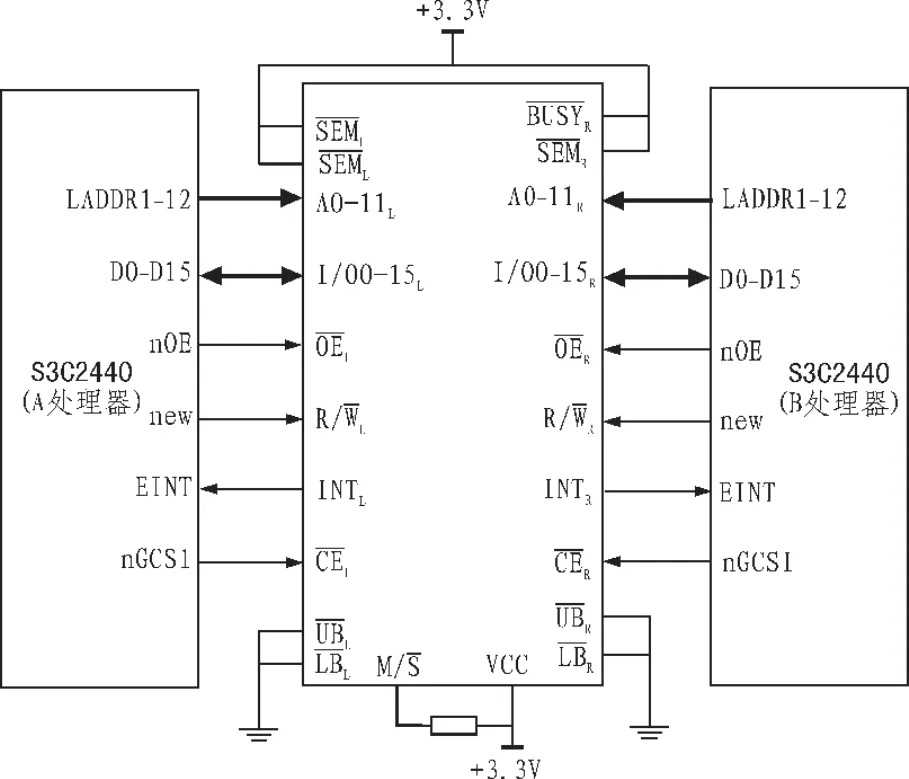

常见的双处理器之间的通信方式有3种:1)通过总线方法实现双处理器之间的通信;2)利用双端口RAM实现双处理器之间的通信;3)利用共享内存的方法双处理器之间的通信。经过综合考虑,本文采用双端口RAM实现双处理器之间的通信。双端口RAM是一种高速的并行传输芯片,具有两套I/O口和竞争裁决电路,可以同时联接两个处理器,这样通过双口RAM可以实现双处理器之间通信[3]。

双冗余飞行控制系统,采用双端口RAM芯片IDT70V24作为A、B处理器的共享存储器,实现双处理器间的通信。双处理器与IDT70V24的接口电路如图2所示。

图2 双口RAM IDT70V24与处理器的接口电路Fig.2 Interface circuit of dual port RAM IDT70V24 with the processors

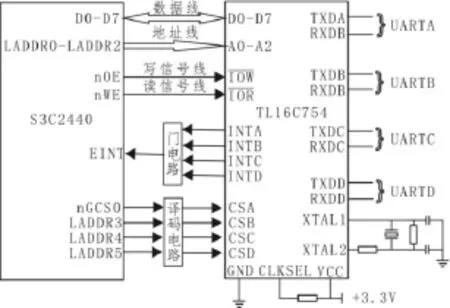

2.4串行通信接口扩展

飞行控制系统在进行地面实验时,串行设备用于和地检设备进行通信;工作过程中,用于和串行接口的机载传感器通信以采集各种信号,也用于和地面传输遥控/遥测数据,主要串行通信方式有 RS232、RS422和RS485。所以,飞控计算机需要具备多串口通信能力。而S3C2440只有3个串口,不能满足设计需求,因此选用并-串转换器件TL16C754芯片进行串口扩展。TL16C754是TI公司生产的4通道异步收发器集成芯片,数据传输率最高可达3 Mbps。TL16C754与处理器的连接如图 3所示,S3C2440的 3条地址线 (LADDR0-LADRR2)、8位数据线 (D0-D7)、以及读写信号线分别与TL16C754的选择片内寄存器的3条地址线、8位数据线(D0-D7)和读写信号线连接;TL16C754的4个串行通道的片选信号(CSA、CSB、CSC、CSD)由译码器产生,对片选信号进行控制;四通道的中断信号(INTA、INTB、INTC、INTD)经门电路后与S3C2440的一个外部中断连接。

图3 TL16C754的接口电路Fig.3 Interface circuit of TLC16C754 with the processor

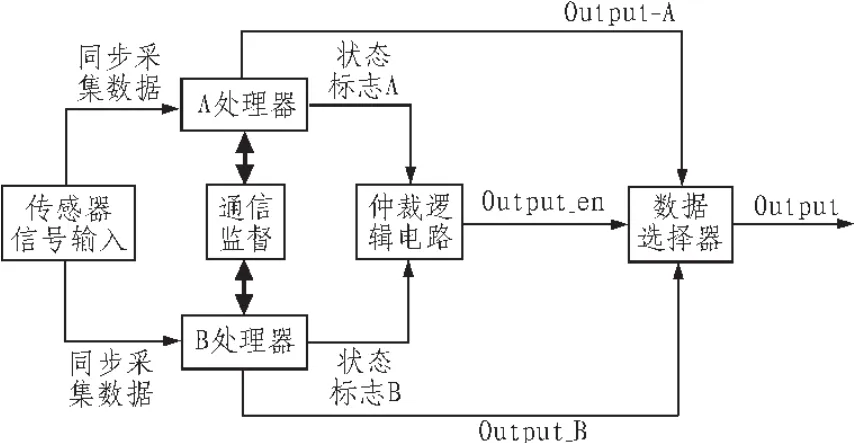

2.5仲裁切换电路设计

双冗余飞行控制系统体积小、重量轻、成本低、电磁兼容性好,这些优点使得这种结构成为微小型无人机的首选方案。双冗余飞行控制系统采用故障诊断等方式通过仲裁切换电路实现故障时的系统动态重构[4],完成故障隔离确保无人机的平稳飞行。双冗余飞控计算机仲裁切换原理框图如图4所示。

图4 系统仲裁切换原理图Fig.4 Arbitration circuit principle diagram of the system

双冗余飞行控制系统主要由输入通道、主飞控计算机(A处理器)、副飞控计算机(B处理器)和仲裁切换电路四部分组成。该系统中,两台处理器同步接收输入信息,通过双口RAM相互通信,定时进行互检来校验处理结果,当数据不一致时说明可能存在故障,则主机和副机分别进行故障诊断和故障定位,最终确定故障飞控计算机并将其隔离。

仲裁信号判断的依据由3个方面组成:看门狗信号、双机比较监控信号和机内自检测信号。

看门狗信号:由于无人机在飞行过程中不希望发生复位现象,导致系统重新初始化,丢失系统相应信息,出现时间上的控制盲区[5],因此,当看门狗定时器超时时不产生复位信号,而是产生中断使看门狗信号标志位输出0,从而表明系统运行过程中发生异常。

双机比较监控信号:双冗余系统中主、副飞控计算机分别对传感器采集信息进行处理并将控制律解算的结果通过双口RAM进行比较,在误差允许范围内,如果两者结果相同,双机比较监控信号标志位置1,否则置0。

机内自检测信号:本系统为功能模块级双冗余系统,除了处理器模块,外围接口电路均为二者共用,因此只需对处理器模块进行自检测。采用基于指令执行的功能性测试对处理器模块进行自检测,即对给定已知测试指令,指令能被正确执行得到正确结果,说明处理器模块正常,否则处理器模块有故障。

故障裁决机构同时接收两个处理器的输出信号,如果A处理器没有故障,无论B处理器有无故障,则默认 A处理器具有系统输出权;如果故障裁决机构检测到A处理器出现故障且B处理器无故障,则裁决B处理器具有系统输出权;若A、B两台处理器均有故障,则整个飞控计算机将不能正常工作,输出钝化值。

3 软件设计

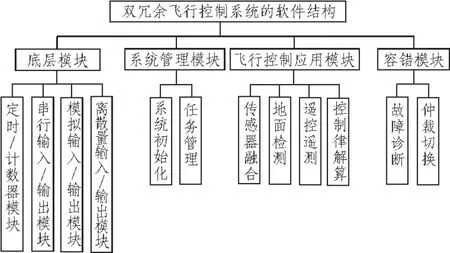

普通单机飞行控制系统的软件设计主要包括3大类:底层模块、系统管理模块和飞行控制应用模块。底层模块包括定时/计数器模块、串行输入/输出模块、离散输入/输出模块和模拟输入/输出模块。系统管理模块包括系统初始化和任务管理。飞行控制应用模块包括传感器融合、地面检测、遥控遥测和控制律解算。

与单机飞行控制系统相比,双冗余飞行控制系统的软件设计,在原有底层模块、系统管理模块和飞行控制应用模块的基础上增添了容错模块,包括故障诊断和仲裁切换。双冗余飞行控制系统的软件结构如图5所示。

4 可靠性分析

可靠性评估技术分为定性与定量两种,其中定量评估技术较直观,可提供数量概念,有实验法和分析法两种方法[6-9]。实验法不仅需要很长的时间以取得大量的实验结果,而且还需要经济上的大力支持。因此,基于现有条件,本文利用可靠性模型对系统的可靠性进行定量分析。本系统与单机飞行控制系统的区别在于多了一个并联的处理器模块和串联仲裁切换电路模块,属于混合系统,可简化为图6所示结构。

图5 双冗余飞行控制系统的软件结构图Fig.5 Software structure diagram of the dual redundant flight control system

图6 串并联混合系统结构Fig.6 Series-parallel hybrid system structure

元器件失效是飞行控制系统硬件故障的主要来源,它将导致各功能模块失效,从而导致整个系统不可靠。故障分布认为是指数分布的,系统中第i单元的可靠度函数为

式中:λ表示系统单元的失效率(单位1/h);t为该单元的工作时间(单位为h)。

根据GJBZ 299C-2006《电子设备可靠性预计手册》中相关元器件的失效率计算模型,计算得到处理器模块的工作失效率为λ1=0.000 027,仲裁切换电路模块的工作失效率为λ2= 0.000 004。

串联系统的可靠度计算公式为

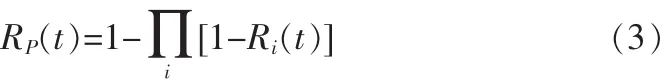

并联系统的可靠度计算公式为

单机飞控系统的可靠度为

双冗余飞控系统的可靠度为

系统的平均无故障时间 (Mean Time To Failure,简称MTTF)是系统发生第一次故障的期望时间,可以通过概率密度函数计算得到

将式(4)和(5)分别代入式(6)后,可得单机和双冗余系统的MTTF分别为

其中,概率密度函数

系统的平均无故障时间TAB>TA,由此可见,所设计的双冗余飞控系统的可靠性得到了极大提高。

5 结 论

本文从工程实际应用需求出发,根据现有资源采用处理器功能模块级双余度技术设计了一种基于ARM的的双冗余无人机飞行控制系统。该设计方案应用故障诊断、仲裁切换和系统重构技术,把硬件冗余和软件容错技术融合到无人机飞行控制系统中,经可靠性定量分析表明,所设计的双冗余飞行控制系统的可靠性确实得到了提高。

[1]Paul G.Fashlstrom,Thomas J.Gleason.无人机系统导论[M].北京:电子工业出版社,2003:1-10.

[2]杨小兵.基于双ARM的飞控计算机核心系统的研究与设计[D].南京:南京航空航天大学,2012.

[3]杨国先,陶霞,王子菡,等.基于双CPU的切换及控制系统的设计[J].微计算机信息(嵌入式与SOC),2006,22(10-2): 268-269.

[4]Zolghadri A,Henry D,Cieslak J,et al.Fault Diagnosis and Fault-TolerantControlandGuidanceforAerospace Vehicles.Springer London[M],2014:119-149.

[5]张小林.小型飞行器机载计算机的余度设计技术[J].西北工业大学学报,2001,19(2):274-278.

[6]王迪爽,肖前贵,杨柳庆.无人机双余度MPC5554飞控计算机[J].电光与控制,2013,20(9):79-83.

[7]韩晨,曹兴冈,陈帅.一种双余度飞控计算机自动测试系统的软硬件设计[J].现代电子技术,2014(22):56-59.

[8]王梅,姬进.双余度信号容错处理与故障注入方法[J].电子科技,2013(6):40-41.63.

[9]王红玲,田广来,赵文庆,等.某型飞机刹车控制系统双余度供电电源失效机理分析及改进[J].电子设计工程,2014 (19):89-92.

Dual redundant flight control system design for small UAV based on ARM

LEI Jin-kui1,YUAN Dan-dan2,LI Hai-sheng2

(1.Research Institute of 365,Northwestern Polytechnical University,Xi’an 710065,China;2.College of Electronic and Information,Northwestern Polytechnical University,Xi’an 710072,China)

In order to improve the reliability and security of the small UAV flight control system,a dual redundant flight control system based on ARM microprocessor is developed,the double redundancy design of the processor at functional module level is completed,and the hardware and software design are introduced in detail.The system reliability has been analyzed quantitatively by establishing the reliability model,and the results have proved that the reliability of the system is exactly improved.

ARM;unmanned aerial vehicle(UAV);dual redundant;flight control system

TN99

A

1674-6236(2016)01-0162-03

2015-06-01稿件编号:201506004

国家863-705基金资助项目(2010AA1071)

雷金奎(1965—),男,陕西合阳人,硕士,研究员。研究方向:多传感器信息融合、计算机应用和飞控系统设计与仿真。