基于FPGA的深度报文检测系统设计

2016-09-08李康士李玉峰董永吉

李康士,李玉峰,董永吉

基于FPGA的深度报文检测系统设计

李康士,李玉峰,董永吉

(国家数字交换系统工程技术研究中心 河南 郑州450002)

针对当前采用正则表达式匹配的深度报文检测系统匹配效率低下,难以满足高速网络线速处理的问题,本文提出了一种基于现场可编程门阵列(Field Programmable Gate Array,FPGA)的深度报文检测系统。该系统采用模块化架构,充分利用FPGA并行处理的特点,通过流水线设计来提升深度报文检测系统的处理速率。

现场可编程门阵列;深度报文检测;正则表达式;流水线设计

近几年来,互联网高速发展,给人们带来便利的同时也带来了日益严重的各类网络安全问题。比如网络信息复杂化、攻击手段多样化等。传统的方式一般是对包头进行扫描,进而做出判断,但是这样的方式却无法发现隐藏在数据包载荷中的不合法内容,对于针对应用层展开的攻击是无能为力。因此,基于深度包检测(Deep Packet Inspection,DPI)的入侵检测系统应运而生。深度报文检测技术主要包括精确字符串匹配和正则表达式匹配。字符串匹配[1]的技术已经相当成熟,但是,最近病毒、垃圾信息等所采用的隐蔽手段层出不穷,仅仅依靠字符串匹配很难确定它们的特征。而正则表达式匹配[2-3]以其灵活、高效的表达能力受到越来越广泛的应用,逐渐成为实现深度报文检测的核心技术。NIDS中的Snort[4]和Bro[5]等规则集都支持正则表达式匹配。但是,在当今网络带宽与入侵规则集规模均日益增长的大背景之下,传统软件实现正则表达式匹配,对网络数据流的线速检测变得越加困难。

为了解决告诉网络链路与匹配速度之间的矛盾,本文设计了一种FPGA的深度报文检测系统,该系统采用模块化设计架构,充分利用FPGA并行处理的特点,通过流水化设计提升深度报文检测系统的处理速率。最后通过VHDL编写各个功能模块,对其进行代码调试、功能仿真、综合、布局布线后,再采用ChipScope进行板级分析和验证,最后下载到FPGA开发板上来实现各模块功能。

1 相关研究

目前,国际上的研究热点已经转向专用硬件实现深度报文检测系统。文献[6-7]是采用GPU的正则表达式匹配引擎来加速深度报文检测中的模式匹配过程,该引擎基于确定型有限自动机(Deterministic Finite Automaton,DFA)模型,在匹配时每一个GPU线程处理一个报文,通过大量的并行线程来提高引擎的吞吐量。文献[8-9]采用三态内容寻址存储器(Ternary Content Addressable Memory,TCAM)来实现深度报文检测,匹配引擎是在DFA模型的基础上进行压缩存储改进,提高相应的存储效率。文献[10]在IBM的一款网络处理器(Network Processor,NP)上设计并实现了B-FSM算法并提出了改进策略,内存缩减达到95%,吞吐率为20Gbps~40Gbps。文献[11-15]采用FPGA实现深度报文检测系统,匹配引擎为正则表达式匹配,研究的重点为DFA压缩算法和存储效率,在压缩效率和吞吐率方面都取得了良好的效果。以上深度报文检测系统都在硬件平台上同时完成了数据处理和正则表达式匹配,由于硬件资源有限导致数据处理速率和匹配效率低下。本文在以上硬件实现深度报文检测系统的研究基础上,从硬件结构出发,提出一种基于FPGA实现的深度报文检测系统,正则表达式匹配模块采用商业级专用芯片,充分利用FPGA并行流水线的优势,提高数据处理速率和匹配效率。

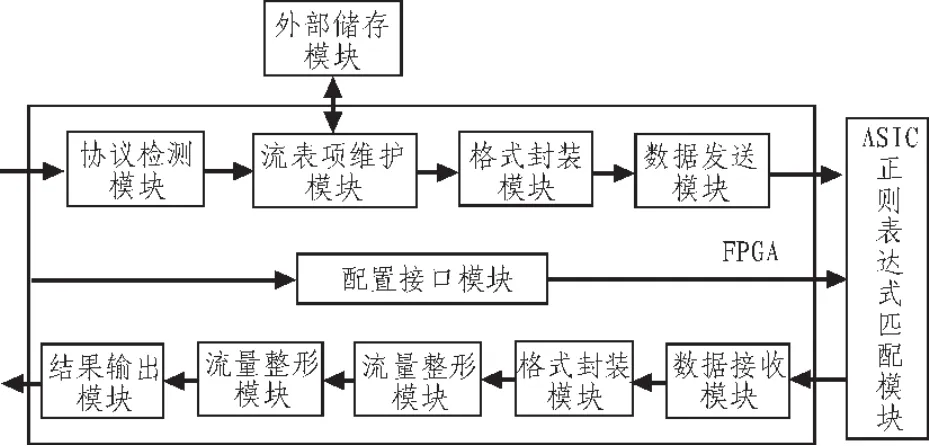

2 总体设计

该系统总体设计方案如图1所示,FPGA采用Xilinx公司的Virtex6系列芯片来实现,用VHDL语言来完成协议检测、表项维护、格式封装和解封装等功能。其中FPGA设计是本系统的重点和难点,本文采用模块化设计将内部逻辑划分为9个功能模块,依次为:协议检测模块、流表项维护模块、格式封装模块、数据发送模块、数据接收模块、格式解封装模块、流量整形模块、结果输出模块和配置接口模块。正则表达式匹配模块采用NetLogic Microsystems公司的 NLS1008芯片;外部储存器模块实现较简单,可以采用多种现有存储器来实现,如DDRII SDRAM、DDRIII SDRAM、SRAM等。

图1 系统模块图

3 模块功能介绍

1)配置接口模块

该模块的主要功能是实现对正则表达式匹配模块内用户自定义的规则表项的维护。首先,由用户自定义配置匹配规则表项;然后,将配置好的规则表项送入配置接口模块;其次,根据用户自定义的匹配规则表项对对配置接口模块中的规则表项进行生成、更新或删除操作;最后,将维护之后的匹配规则表项送至正则表达式匹配模块。

2)协议检测模块

该模块主要用于对原始报文的协议进行分析检测原始报文的有效性。如果原始报文有效则记录包长,根据帧格式要求将对小于64字节的报文进行字节填充,并提取原始报文的五元组协议信息,最后将五元组信息及数据流传递给流表项维护模块;如果原始报文是无效的则直接丢弃。协议检测模块只对报文提出相关信息,并不影响原始报文在设备中的正常转发处理,提出的信息送至后续模块继续进行处理。

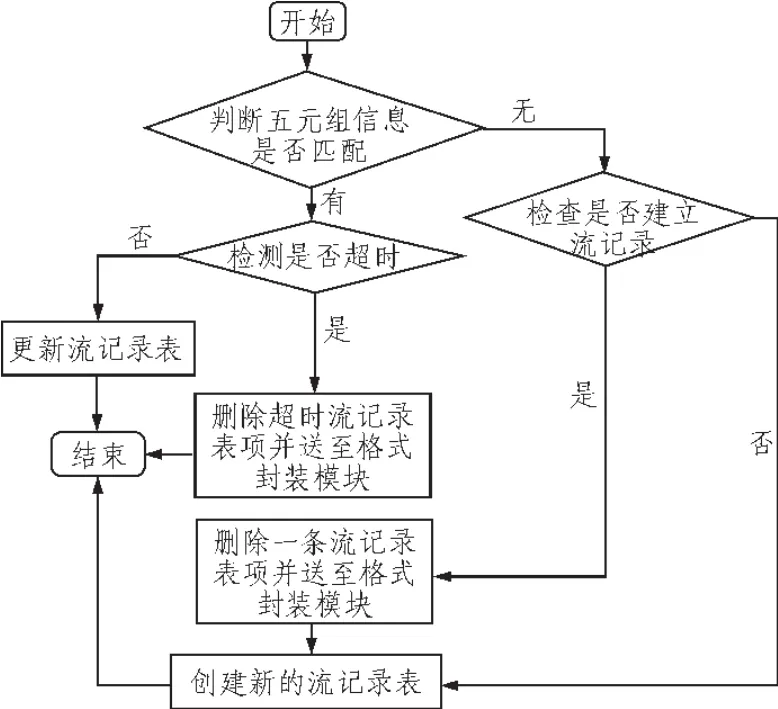

3)流表项维护模块

流表项维护模块负责对各类表项进行记录上报判定,及时释放超时表项的空间以容纳新表项。根据由数据流五元组信息得到的地址,从存储器中读出表项,再将该数据流的五元组与该表项中存储的五元组信息进行比较,根据比较结果对存储器中的表项进行更新或超时删除等操作。表项维护处理流程如图2所示,其主要步骤如下:

步骤1:对原始报文的五元组信息流进行分析查找,判断从协议检测模块输出的流记录中的五元组信息是否与表项空间中的表项地址上的五元组匹配,如果是执行步骤3,如果无则执行步骤2;

步骤2:检查表项空间中的表项地址上是否都已经建立了流记录表(表项空间是否已经被占满),如果是,执行步骤6,否则执行步骤7;

步骤3:通过从流单元表中的提取的时间戳判断需要匹配的流记录表是否已经超时,如果是,执行步骤4,否则执行步骤5;

步骤4:删除超时的流记录信息,生成24字节的流状态索引,并将该条流信息送至格式封装模块进行封装;

步骤5:对流记录表中的包长,包个数及时间戳等信息进行更新;

步骤6:删除表项记录空间中的一条流记录表项,生成24字节的流状态索引,并将删除的该流记录表信息送至格式封装模块封装输出;

步骤7:在表项空间中未被占用的地址上为新流创建流记录表。

图2 流表项维护处理流程图

4)格式封装模块

该模块主要功能是根据流表项信息和正则表达式模块对格式头的要求构造格式头,然后对原始报文进行格式头转换和封装。封装之后的报文格式如图3所示,主要包括:用户自定义源MAC,用户自定义目的MAC,以太网类型,CMD,开始,结束,载荷偏移量,填充长度,用户自定义区域,流状态索引,组元地址,保留字段,二层帧。

图3 封装格式

5)数据发送模块和数据接受模块

数据发送模块主要功能是通过10G高速I/O接口将格式封装后的数据传给正则表达式模块。数据接收模块主要功能是通过10G高速I/O接口接收经过正则表达式匹配返回的数据。10G高速I/O接口采用Xilinx公司提供的10GMACXAUI软核来实现。正则表达式模块返回的的数据格式如图4所示,主要包括:用户自定义源MAC,用户自定义目的MAC,以太网类型,结果,错误指示,结果统计,用户自定义区域,保留字段,结果钳位,基本偏移量,保留字段,偏移分量,规则地址,优先级,完成,结束,对应组号,二层帧。

6)格式解封装模块

该模块主要功能从接收到的数据中解析出原始二层帧和匹配结果。首先,将数据接收模块返回的数据存入预处理缓存即先入先出队列(First in First out,FIFO);然后,将数据从FIFO中读出,并从数据中解析出匹配结果和原始二层帧;最后,将匹配结果和原始二层帧分别存入不同FIFO。

7)流量整形模块和结果输出模块

流控整形模块主要功能是根据用户配置的阀值对数据流进行整形,使不平稳的数据流趋于平稳。由于现实网络中的流量不可能是一直平稳的,总会有突发流量的存在,这就需要用户根据自己配置的阈值对数据流进行流量整形使数据趋于平稳,便于用户进行其他操作。

结果输出模块主要作用将原始查表报文和匹配结果交付给用户,由用户根据匹配查找结果,对报文进行自定义操作。

4 板级测试

本文主要所述系统的开发工具为Xilinx ISE14.7,功能仿真工具为Modelsim10.2。使用VHDL编写各个功能模块,然后对其进行代码调试、功能仿真、综合、布局布线后,再采用ChipScope进行板级分析和验证,最后下载到FPGA芯片中来实现各模块功能。

5 结 论

该系统采用FPGA实现深度报文检测系统,完成了系统功能仿真和板级测试,达到了初步要求。但是,本系统在测试中采用的是人为构造数据而不是现实网络中的数据,与现实网络中的数据存在一定差异。在后续工作中,应该充分考虑实际情况,抓取现实安全威胁库中的正则规则集和网络中的数据包作为测试数据,来达到对工程实践更好的指导意义。

[1]AHO A VCORASICK M J.Efficient String Matching:An Aid To Bibliographic Search[C].Communications of the ACM,1975,18(6):333-340.

[2]姚远,刘鹏,单征,等.面向存储的正则表达式匹配算法综述[J].计算机应用,2009,29(12):3171-3173.

[3]Jeffrey E.F.Friedl.Mastering Regular Expressions[M].O Reilly Media,2006.

[4]SnortSystem[EB/OL].http://www.snort.org,2014.

[5]Bro Intrusion Detection System[EB/OL].http://www.bro-ids. org,2014.

[6]王磊,陈曙晖,苏金树,等.深度报文检测中基于GPU的正则表达式匹配引擎[J].计算机应用研究,2010,27(11):4324-4327.

[7]钱权,朱伟,车弘毅,等.改进的多模式串匹配算法及GPU并行化研究[J].中国科学院大学学报,2013,30(5):706-713.

[8]丁麟轩,黄昆,张大方,等.基于 TCAM的低能耗正则表达式匹配算法[J].通信学报,2014,35(8):162-169.

[9]彭坤杨,等.基于TCAM的高速可扩展的正则表达式匹配技术[D].合肥:中国科学技术大学,2013:18-40.

[10]Jan van Lunteren,Alexis Guanella.Hardware-Accelerated Regular ExpressionMatching at Multiple Tens of Gb/s[J]. 2012 Proceedings IEEE INFOCOM,2012:1737-1774.

[11]QiuTanga,Lei Jianga,Xin-xingLiua,Qiong Dai.A Real-time UpdatableFPGA-basedArchitectureforFastRegular ExpressionMatching[J].InformationTechnologyand Quantitative Management(ITQM 2014).Procedia Computer Science,2014(31):852-859

[12]Shuhui Chen,Rongxing Lu.A regular expression matching engine with hybrid memories[J].Computer Standards& Interfaces,2014(36):880-888.

[13]Yoichi Wakaba,Shinobu.A Flexible And Compact Regular Expression Matching Engine Using Partial Reconfiguration For FPGA[J].2013 16th Euromicro Conference on Digital System Design,2013:293-296.

[14]Yuan Wen,Xingsheng Tang,LihanJu,Tianzhou Chen. PeRex:A power efficient FPGA-based architecture for regular expression matching[C].2011 IEEE/ACM International Conference on Green Computing and Communications.2011:188-193.

[15]陈曙晖,徐成成,等.基于两级存储的正则表达式匹配技术[J].通信学报,2014,35(6):47-55.

Design of the deep packet inspection system based on FPGA

LI Kang-shi,LI Yu-feng,DONG Yong-ji

(National Digital Switching System Engineering Technological R&D Center Zhengzhou 450002,China)

The current deep packet inspection systems using regular expression matching faces the problems that it cannot meet the wire-speed processing of high-speed network,this paper presents a field-programmable gate array-based deep packet inspection system.The system adopts a modular architecture,take full advantage of parallel processing characteristics ofFPGA.Enhance the processing speed of deep packet inspection system through pipelined design.

field programmable gate array;deep packet inspection;regular expression;pipelined design

TN02

A

1674-6236(2016)09-0147-03

2015-12-11稿件编号:201512128

国家科技支撑计划项目(2014BAH30B01)

李康士(1991—),男,河南商丘人,硕士。研究方向:网络安全。