基于改进延迟锁相环的高速低抖动时钟电路的开发与设计

2016-09-08沈学锋

沈学锋

(1.中国石油大学(华东)胜利学院,山东 东营 257061;2.中国石油大学(华东)信息与控制工程学院,山东 东营 257061)

基于改进延迟锁相环的高速低抖动时钟电路的开发与设计

沈学锋1,2

(1.中国石油大学(华东)胜利学院,山东 东营257061;2.中国石油大学(华东)信息与控制工程学院,山东 东营257061)

文中针对传统时钟产生电路精度低且抖动大的问题,开发与设计了一种基于改进延迟锁相环的时钟电路。电路仿真结果表明,当输入时钟信号频率为20~150 MHz时,输出时钟信号占空比稳定在(50±0.15)%,时钟抖动在0.8 ps之内,不仅实现了精度的增大,且还具有低抖动的功能,满足了高速高精度 ADC转换器的时钟要求。

高速模数转换器;延迟锁相环;时钟电路;高精度低抖动

对于高速模/数转换器(ADC)转换器而言,采样频率与时钟频率相关。随着ADC转换器往高速度,高精度方向发展,采样时钟的稳定性变得更加重要[1-4]。传统的时钟电路采用普通锁相环(PLL)或由压控延迟线,用于相位调整控制信号生成的电荷泵以及检测输入信号相位差的鉴相器[5-6]组成的延迟锁相环来组成时钟电路。前者由于相位累积以及由压控振荡器(VCO)产生的噪声而精度较低,后者在对时钟频率精度调整时需要控制电荷泵的匹配,且调整过程中也会对上升沿和下降沿产生干扰,使时钟产生较大的抖动。

为了设计高速低抖动时钟电路,本文在对由一般延迟锁相环[7-9]所构成的时钟电路进行深入探究的基础上,针对其存在的不足,提出了一种新的时钟电路设计方法:首先是将传统延迟锁相环中的鉴相器替换为基于RS锁存器的鉴相器来进行相位检测,其利用输入信号经过延迟电路后与自身相与产生窄脉冲,然后窄脉冲经过延迟电路后与自身相与并取反得到一个宽脉冲信号,通过这一脉冲信号来追踪信号的相位差,并锁定时钟的上升沿和下降沿,消除了传统鉴相器由于逻辑元件以及反馈回路延迟导致的鉴相失真,且降低了电路设计难度。其次用连续时间积分器取代了原来的电荷泵,避免了由于电荷泵失配以及开关引起的误差,生产受工艺参数影响等导致的误差而使精度更高,满足高速高精度模数转换器的时钟要求。

1 高速低抖动时钟电路

1.1时钟抖动对高速模数转换器的影响

时钟产生抖动(jitter)会使发生抖动的时钟信号与未发生抖动的时钟信号在时域上存在偏差,从而使模数转换器的采样频率发生紊乱,最终导致模数转换器采样的不稳定性[10],使输出信号存在频谱毛刺,导致误码率上升,限制数据结构传输效率。随着输入时钟信号频率的不断增高,由时钟抖动而引起的噪声也逐渐从小频率下的可忽略噪声变换到在高频率下占主导地位而不可忽略,使信噪比(SNR)变小,降低了模数转换的精度。

1.2高速低抖动时钟电路系统结构

文中在传统延迟锁相环上改进的延迟锁相环基础上设计的时钟电路,其系统结构图如图1所示。其功能为对外部输入时钟信号,当其占空比不为50%时,对其占空比进行调整并稳定为50%。由图1可看到,该电路主要分为4个部分。1)是时钟缓冲放大器电路(Clock buffer),其主要功能是将小摆幅差分输入时钟信号转换为时钟方波;2)是时钟选择电路(Clock path select),其功能是对输入时钟信号的占空比进行判断,当占空比为50%时,不用调整,若不为50%时,调整为50%。3)是占空比调整电路(DCS),即对输入时钟信号进行调整;4)是非交叠时钟产生电路(Nonoverlapping clock),产生满足不同模数转换器的时钟信号。

图1 时钟电路系统结构图

其工作原理为:首先,外部输入时钟信号经过时钟缓冲放大器电路从小幅度差分信号转换为方波信号,然后时钟选择电路对外部时钟信号占空比进行判断,当占空比为50%时,时钟选择电平V0对时钟选择电路输出控制信号VEN使占空比调整电路不工作,同时闭合S1,输入时钟信号直接到达非交叠时钟产生电路,产生满足不同模数转换器的时钟信号。

当占空比不为50%时,时钟选择电平V0对时钟选择电路输出控制信号VEN使占空比调整电路开始工作,同时断开S1,输入时钟信号进入占空比调整电路,调整占空比。当输出信号VOUT占空比达到50%时,占空比调整电路环路锁定,输出控制信号Vg使S2闭合,输出信号进入非重叠时钟产生电路,产生满足不同模数转换器的时钟信号。

2 占空比调整电路

占空比调整电路是时钟电路中最核心的部分,其关系到整个时钟系统的速度及精度。如图1所示,占空比调解电路由基于RS锁存器的鉴相器,延迟电路,和基于积分器的占空比检测电路组成。其工作原理为:首先,外部输入信号从鉴相器输入,接着转变成跟相位差成正比例关系的时钟信号从鉴相器输出并形成延迟电路的控制电压。接着延迟电路在控制电压的控制下不断调节时钟信号的上升沿与下降沿的延时,直到输出时钟信号占空比为50%,此时RS锁存器锁定输出时钟信号。三者协调共存,形成一个动态平衡。

2.1基于RS锁存器的鉴相器

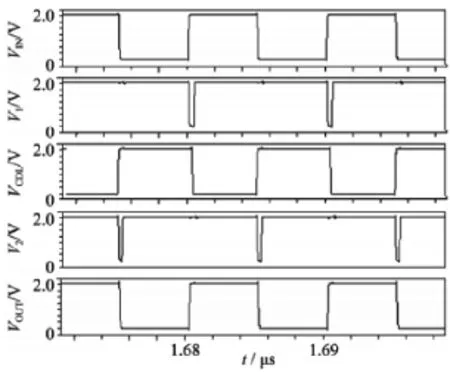

图2所示为基于RS锁存器的鉴相器,其中VIN为输入时钟,VCDL为调整信号。原输入信号进入鉴相器之后分成两个支路,其中一路经过延迟电路后与另一路信号相与取反得到一个窄脉冲信号V1,此时V1的下降沿与VIN的上升沿正好处在同一时间节点上,这可检测原信号的上升沿,并通过调整上升沿来调整信号的占空比,不仅有利于降低电路的复杂性,且有利于降低时钟的抖动。同时V1经过延迟电路后形成调整信号VCDL,VCDL经过延迟电路后与自身相与取反得到宽脉冲信号V2,此时V2下降沿与VCDL上升沿在时域上相对齐。最后,V1和V2通过RS锁存器得到了反映输入信号VIN与调整信号VCDL相位差的输出信号VOUT。电路的瞬态仿真结果,如图3所示。

图2 基于RS锁存器的鉴相器图

图3 鉴相器时序图

当V1和V2的延时为T/2时,鉴相器产生与VIN和VCDL相位差成线性比例的脉冲信号,信号占空比为50%。

2.2基于积分器的占空比检测电路

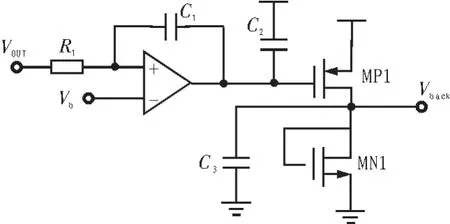

传统延迟锁相环通过电荷泵来消除相位失调。首先,这要求电荷泵的失配度较小。其次,电荷泵制造过程中也极易受工艺参数影响[11-13]。所以,文中采用基于联系积分器的占空比检测电路,其电路结构如图4所示。

图4 RC积分器占空比检测电路

其中Vb为参考电压,VOUT为鉴相器输出电压,Vback为检测电路的输出电压。MP1和MN1形成共源放大器,隔离和缓冲积分器输出信号。在此,为了使整个电路能稳定运行,在单周期内占空比50%时,Vback在一个周期内的净变化量必须为零,因此取Vb=(VSS+VDD)/2。

当信号一进入积分器,积分器并未立即工作,此时积分电容C2下极板为高电平,P型晶体管MP1处于截止状态,信号到输出节点之间的连接被断开,输出信号Vback为零。随后积分器开始对输入信号进行积分,当输入信号占空比不为50%时,积分器输出信号为三角波,其上升时间与下降时间不相同。积分器输出信号通过共源放大器形成控制信号,通过延迟电路调节电容的放电时间,控制延迟,不断调节两输入信号的延迟差,直到积分器输出信号占空比稳定在50%。

3 电路仿真

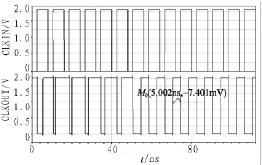

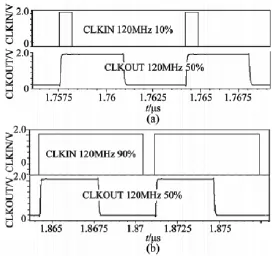

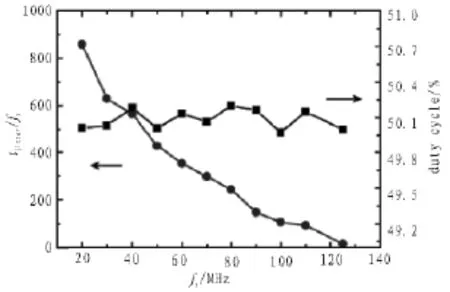

文中对所设计的时钟电路进行仿真,仿真结果如图5和6所示。由图5可看出,当输入时钟信号频率为80 MHz时,时钟电路在80 ns内就将输入时钟信号占空比调整为50%。图6(a)和(b)分别为输入时钟频率为120 MHz时,输入占空比分别为10%和90%时,调整为占空比等于50%的过程。图7为输出时钟信号的占空比和抖动随输入频率变化关系。文中在20~150 MHz之间取11个频率节点进行仿真实验,并记录下每次得到的输出时钟信号的占空比跟抖动。图中数据显示,输入时钟信号在20~150 MHz之间时,输出时钟信号占空比稳定在 (50±0.15)%以内,且随着输入时钟信号频率的增大,输出时钟信号抖动逐步减小,当频率高达120 MHz时,抖动接近为零,最大抖动也小于0.8 ps。与传统时钟电路相比,该时钟电路能调节的输入时钟信号占空比范围更大,锁定时间更短,且能够抑制时钟抖动,尤其是在高频时,其时钟信号抖动更接近为零。

图5 时钟稳定输出波形

图6 120 MHz,输入占空比为(a)10%和(b)90%调整结果

图7 输出时钟抖动和占空比随采样频率变化曲线

4 结束语

文中在传统延迟锁相环的基础上,针对传统时钟电路的不足,同时为了满足高速高精度ADC的要求,开发与设计了由改进延迟锁相环所组成的高速低抖动时钟电路,将原来延时锁相环中的鉴相器与电荷泵替换为基于RS锁存器的鉴相器以及连续积分器占空比检测电路。仿真结果表明,当输入时钟信号频率为80 MHz时,时钟电路在80ns内就将输入时钟信号占空比调整为50%,并在输入时钟信号频率为20~150 MHz时,输出时钟信号占空比稳定在(50±0.15)%,时钟抖动在0.8 ps之内,不仅实现了精度的增大,且还具有低抖动的功能,满足了高速高精度ADC转换器的时钟要求。

[1]FAN C W,WU J T.Jitter Measurement and Compensation for Analog-to-Digital Converter[J].IEEE Transactions on Instrumention and Measurement,2009,58(11):3874-3884.

[2]KE J W,HUANG SH Y,KWAI D M.A high-resolutionalldigital duty-cycle corrector with a new pulse-widthdetector[C].IEEEInternationalConferenceonElectronDevicesand Solid-State Circuits,Hong Kong,15-17,Dec.,2010:1-4.

[3]魏丰,王瑞清,王群,等.一种GPS校准的数字式高精度守时钟[J].仪器仪表学报,2011,32(4):921-926.

[4]GAO W,GAO D,BRASSE D,et al.Precise multiphaseclock generation using low-jitter delay-locked loop techniques for positron emission tomography imaging[J].IEEE Transactions on Instrumention and Measurement,2009,57(3):1063-1070.

[5]WANG R M,LIU CH Y,LU Y C.A Low jitterdLL-based pulse width control loop with wide duty cycleadjustment[C]. IEEE Asia Pacific Conference on Circuitsand Systems,Macao,2008:418-423.

[6]HAN S R,LIU S I.A single-path pulse width controlloop with a built-In delay-locked loop[J].IEEE Journalof Solid-State Circuit,2005,40(5):1130-1135.

[7]HUANG H Y,LIANG C M,CHIU W M.1%~99%inputduty 50%duty cycle corrector[C].IEEE InternationalSymposium on Circuits and Systems,Island of Kos,Greece,21-24May,2006:4175-4178.

[8]RYU K H,JUNG D H,JUNG S O.A DLL based clockgenerator for low-power mobile soCs[J].IEEE Transactions on Instrumention and Measurement,2010,56(3):1950-1956.

[9]史凯运,雷振亚,侯建强.锁相环产生具有高线性度三角调频信号的方法[J].电子科技,2015,28(2):147-149.

[10]常博皓,林永嘉.锁相环电源噪声激起的抖动灵敏度研究[J].电子科技,2014,27(2):62-65.

[11]徐鸣远,沈晓峰,朱璨,等.一种用于高速高精度A/D转换器的时钟稳定电路[J].微电子学,2010,40(5):310-312.

[12]吴义华,杨俊峰,邓美彩.几种利用ADC采样测量时钟抖动方法的比较[J].电子测量与仪器学报,2007,21(2):70-75.

[13]屈八一,周渭.高精度时间间隔测量仪的研制[J].仪器仪表学报,2009,30(7):1476-1480.

Development and design of high-speed and low-jitter clock circuit based on improved delayedPLL

SHEN Xue-feng1,2

(1.Shengli College China University of Petroleum,Dongying 257061,China;2.Information and Control Engineering,China University of Petroleum,Dongying 257061,China)

In this paper,a clock generating circuit based on the improved PLL clock circuit is developed and designedfor the low precision and high jitter of the traditional clock circuit.And the circuit simulation results show that when the input clock signal frequency is 20 MHz to 150 MHz,the output clock signal duty cycle stabilizer in(50±0.15)%,and clock jitter is under 0.8 ps.It not only achieve increased accuracy,but also has low shake function,to meet the high-speed high-precision ADC converter clock requirements.

High-speed ADC;delay locked loop;clock circuit;high-precision;low-jitter

TP

A

1674-6236(2016)09-0048-03

2015-12-23稿件编号:201512228

中央高校基本科研业务费专项资金资助(15CX02103A)

沈学锋(1973—),女,山东淄博人,硕士,讲师。研究方向:电力系统及其自动化。