基于国产FPGA的增量式光电编码器测速电路研究

2016-09-07马玲芝

马玲芝,李 鸿

(长沙理工大学 电气与信息工程学院,长沙 410114)

基于国产FPGA的增量式光电编码器测速电路研究

马玲芝,李鸿

(长沙理工大学 电气与信息工程学院,长沙410114)

利用增量式光电编码器测量电机转速对伺服控制有着至关重要的作用;针对于目前测速系统对频率、实时性等方面的要求,并结合国产FPGA(field-programmable gate array可编程逻辑器件)芯片的优势,提出利用嵌有ARM(acorn rISC machine)内核的国产FPGA芯片CME_M7作为硬件开发平台,并采用Verilog HDL(HDL: hardware description language硬件描述语言)语言编程的方法,设计了一种基于国产FPGA的增量式光电编码器测量电机转速的测速电路;经过实验验证,证明了所设计的测速电路精度高、测速范围宽、实时性好、抗干扰能力强。

国产FPGA;增量式光电编码器;转速;硬件描述语言

0 引言

在伺服运动控制系统中,一般都采用增量式光电编码器测量电机转速。随着增量式光电编码器技术的不断发展,采用增量式编码器测量电机转速的方法日新月异。现今各种伺服控制系统对速度精度、速度平稳性、时间延迟等性能指标要求不断提高,使得设计精度高、分辨率高、响应快的测速系统十分迫切。增量式光电编码器测速原理比较简单,现一般有以下几种常用的办法:M法、T法和M/T法。M法在高速区域测量效果好,低速测量区域效果差。与之相反,T法是低速区域测量效果好,高速区域测量效果差。M/T法则是结合了T法和M法的优点,测速范围宽,但是其检测时间过于固定,不够灵活[1]。在此基础之上,提出了变M/T法的测速方法,该法测量时间和所测光电脉冲个数均随转速的变化而变化,但测量时间一直等于整数个所测光电脉冲数。随着FPGA技术的不断更新,我国自主研发生产的FPGA在低端应用领域有着性价比高、自主性强等优势,因此使得利用硬件描述语言在国产FPGA上实现电机测速电路成为可能,所以本文采用国产FPGA+ARM的片上系统架构,通过改进的变M/T法,并用Verilog HDL语言进行片上编程,来实现在国产FPGA芯片上对电机转速进行测量的电路设计。

1 测速原理

利用增量式光电编码器对电机的转速进行测量,需要求得在时间t内所发生相应的光电脉冲个数n,通过编码器的刻线数N,就能计算出编码器的转速r(°/s),计算公式为式(1):

(1)

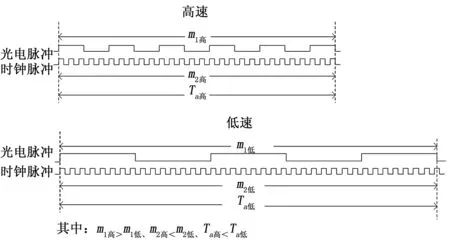

要想计算电机转速,必须得知道在一段具体的时间t内所发生的脉冲个数n。由于不同的转速r下,所发生的脉冲个数n在固定的时间t内是不一样的。当时间t太短,而转速r过慢,则在时间t内有可能不会发生脉冲,自然就测不出转速;如果将时间t拉长,虽然能测量更低的转速,但是会严重影响系统的响应程度。因此必须得依据转速的快慢,来自动调整时间t,使时间t在电机转速快时短,在电机转速慢时适当的长一些(由相对性可知,转速慢时,转速变化率小,响应时间适当加长并不会对系统的快速响应性产生太大的影响),这样既可以测量较宽范围的转速,也满足了系统的快速响应性,这就需要使用变M/T法,具体见图1所示的变M/T法,当中光电脉冲个数m1和时间Ta成反比例,这是因为高速时,在短时间内已经发生了足够的光电脉冲数来计算转速,而低速时,为了尽可能的缩短时间Ta,则尽量在能测得转速的情况下减少测量的脉冲数,整个测速过程中将光电编码器的A、B两相脉冲进行四倍频计数,这样在所能测的最慢转速情况下,可以将时间Ta缩短为原来的1/4,既能对电机进行低速状态的测量,也节约了时间,同时对编码器的A、B两相脉冲进行四倍频计数也提高了测速精度。

图1 变M/T法原理图

2 硬件构成

2.1国产FPGA

设计中采用的国产FPGA芯片是北京京微雅格公司的山系列芯片CME-M7,CME-M7集成了主流的ARM Cortex-M3内核和高性能FPGA,FPGA的运行频率最高可达200 MHz,它的逻辑单元高达12 K,ARM Cortex-M3内核最大频率可达300 MHz,此款芯片的处理器采用嵌入ARM硬核处理器的方式,与其他嵌软核处理器方式的FPGA芯片相比,可以节约大量的FPGA逻辑单元。该M7芯片的编程软件是Primace,Primace是京微雅格公司独立开发的一款专门针对于该公司FPGA芯片的编程软件,自主性强,编程语言可以使用较为易学易用的、简洁灵活的Verilog HDL语言,同时在芯片内部FPGA逻辑和ARM逻辑共享存储器的地址,这使得FPGA和ARM进行数据交流更为直接方便。

2.2测速系统硬件结构

整体测速电路的编程思路是在FPGA里面进行光电脉冲的采集、脉冲边沿计数和时间的提取、数据转换和运算,以及位置和转速等信息的存储,利用ARM内核调用所存储的转速等信息数据以供后续控制程序使用,具体的整体硬件构成如图2所示,电机带动增量编码器转动,增量编码器产生的光电脉冲被M7内部的增量编码器接口所采集,经过FPGA的内部逻辑计算,将增量式编码器的位置和转速等信息存入EMB (Embedded Memory Block嵌入式存储块)中,ARM内核通过对EMB进行读操作,将增量编码器的位置和转速读出以供使用,同时可将位置和转速通过串口在PC机打印出来进行观察。

图2 增量式编码器测速电路硬件结构图

3 程序算法

3.1FPGA程序模块介绍

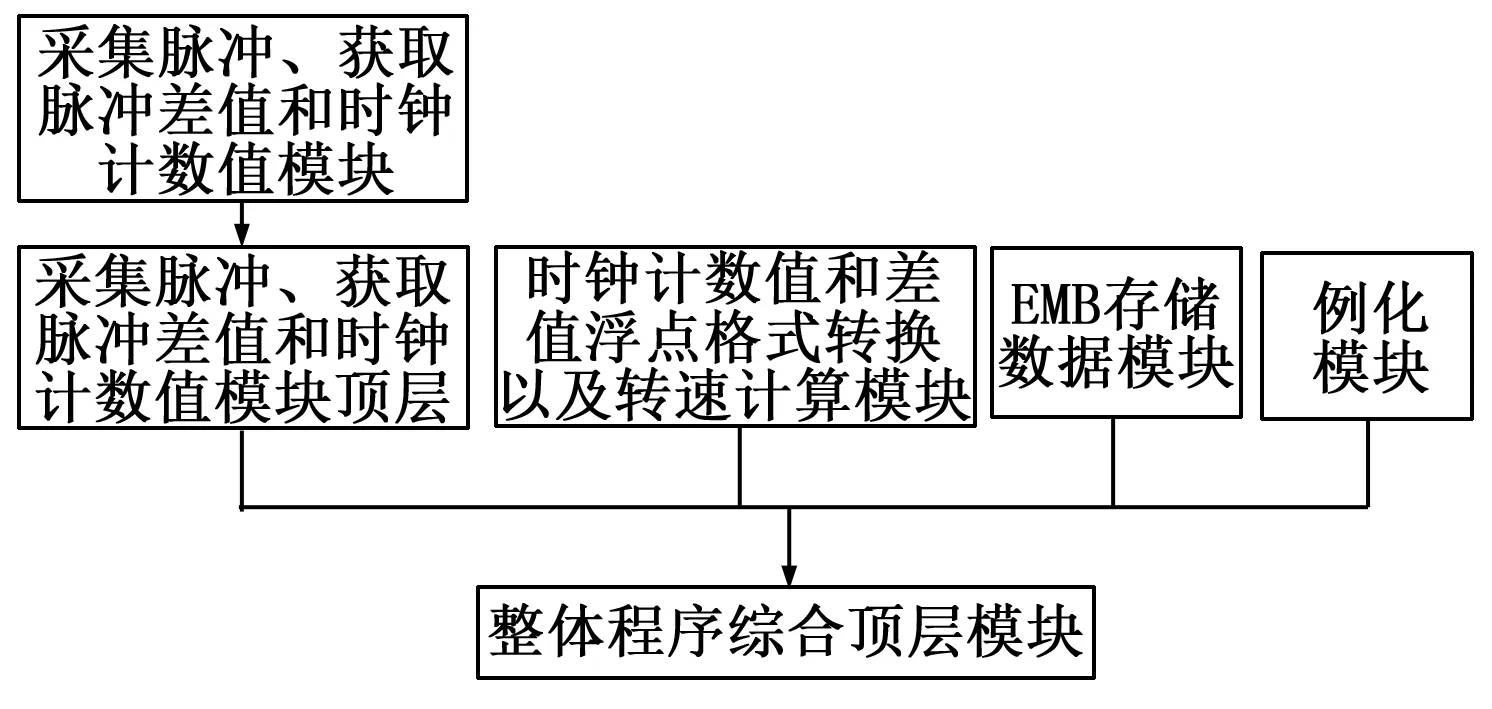

FPGA程序设计采用分模块的设计方法,具体模块划分如图3所示。

1)采集脉冲边沿、获取脉冲边沿差值和时间模块:

此模块用于采集A、B两相的脉冲的上升沿和下降沿并计算沿数和判断方向,并依据改进的变M/T法取得脉冲边沿的差值和相应差值所花的时钟计数值。

2)采集脉冲边沿、获取脉冲边沿差值和时钟计数值模块顶层:

此模块为采集脉冲边沿、获取脉冲边沿差值和时钟计数值模块的顶层,方便其他模块调用。

3)时钟计数值和差值浮点格式转换和转速计算模块:

此模块先将采集脉冲边沿、获取脉冲边沿差值和时钟计数值模块所发来的脉冲边沿差值和相应差值所花的时钟计数值按照IEEE(Institute of Electrical and Electronics Engineers国际电子电器工程师协会)转换成浮点格式的数据,然后调用浮点乘法计算模块和浮点除法计算模块进行浮点格式的转速计算。

图3 增量式编码器FPGA测速电路模块组成

4)EMB存储数据模块:

此模块通过例化的EMB模块,将前面模块所采集到的脉冲边沿个数、脉冲边沿差值、相应差值所花的时钟计数值和计算出的转速(脉冲/秒)存入不同的地址当中,之后ARM可在相应的地址当中读取。

5)例化模块:

此模块是从软件平台primace里面直接例化的模块,包括例化ARM内核、例化系统时钟模块(此程序为ARM内核配置200 MHz的时钟,为FPGA配置了20 MHz的时钟)、例化浮点除法计算模块和浮点乘法计算模块。

6)整体程序综合顶层模块:

此模块是整个工程的综合模块,联系工程中不同文件,并处理FPGA芯片内部和外界的连接。

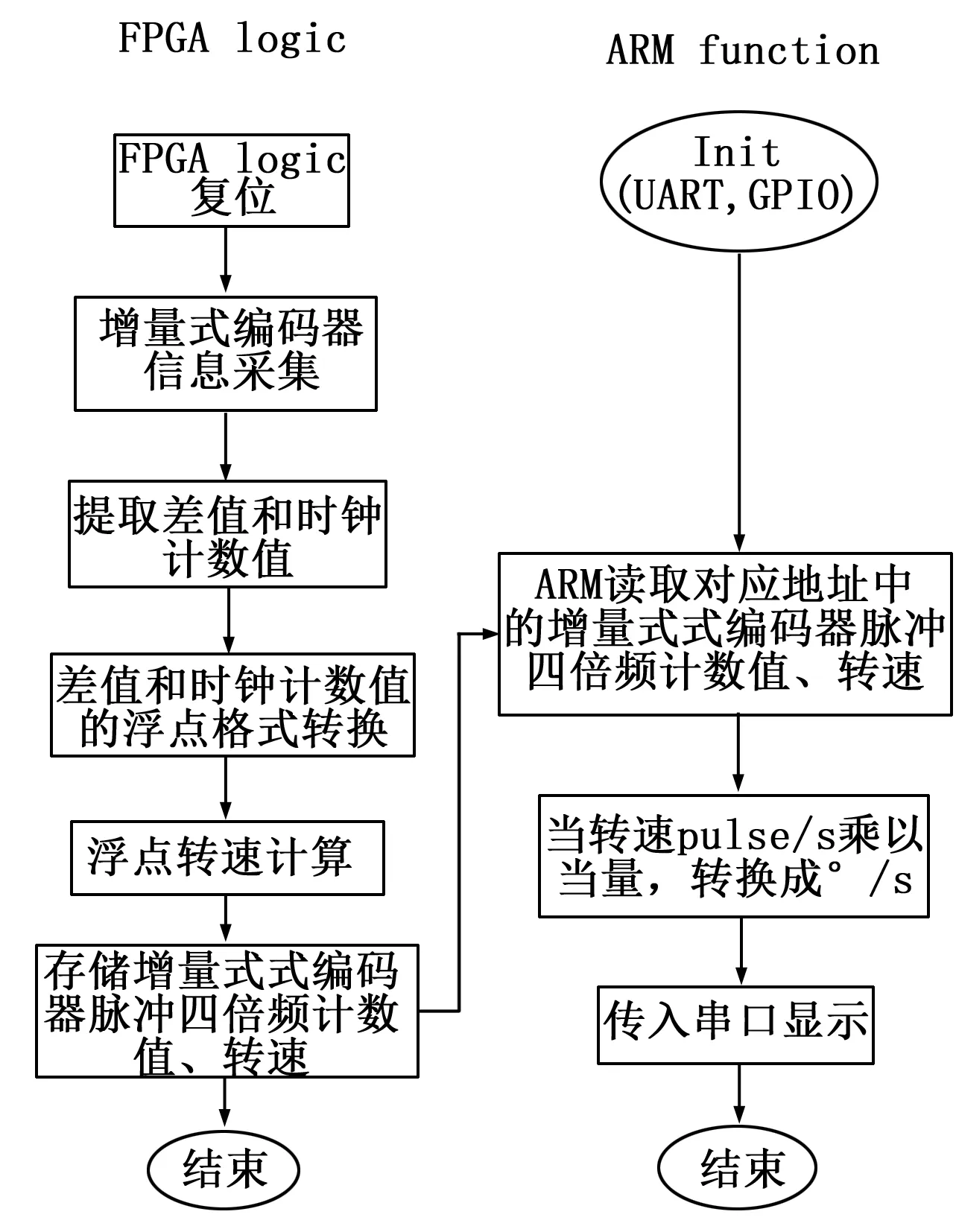

3.2程序流程

步骤1:判断方向。

程序中将采集的A相和B相分别表示为变量phase_A和phase_B,分别检测phase_A的上升沿L2H_Sig_A和下降沿H2L_Sig_A,以及phase_B的上升沿L2H_Sig_B和下降沿H2L_Sig_B,用来判断电机转动的方向direction。

步骤2:脉冲边沿计数。

通过变量L2H_Sig_A、H2L_Sig_A、L2H_Sig_B、H2L_Sig_B来对编码器光电脉冲进行四倍频计数,同时判断direction的值来确定count_edge的计数方向,正转则加,反转则减。此四倍频计数方法可在一定范围内消除电机低速转动时的干扰脉冲[2],因为干扰脉冲一般出现在A相或是B相的同一电平之下,这样程序会分别判断一次正转和一次反转,脉冲边沿计数值会一加一减从而抵消。

步骤3:脉冲边沿差值和时钟计数值的提取。

依据电机转速的快慢,提取脉冲边沿差值和相对应的时钟计数值,并提供给后续模块使用。

步骤4:脉冲边沿差值和时钟计数值的浮点格式转换。

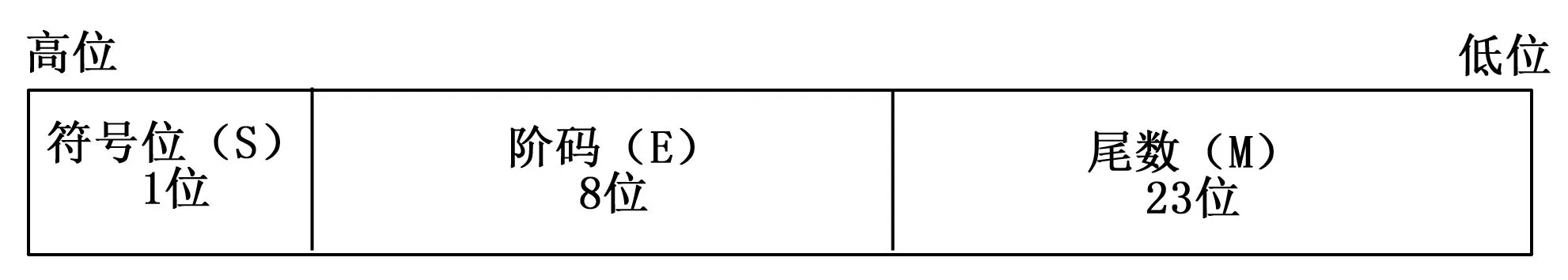

由于需要在FPGA里面将转速计算出来,这就涉及到了FPGA的浮点计算问题,本设计采用的编程软件Primace7.0带有Floating Point IP核,调用此核能够进行浮点数的算术运算,但是其传进去的参数必须得是32位的浮点数格式的形式,所以得先将脉冲边沿差值和时钟计数值转换成浮点格式后再送入Floating Point IP核进行计算,从而算出转速。按照IEEE制定的IEEE浮点数表示法可以将一个整数转换为32位的单精度浮点数格式,如图4所示。

图4 IEEE浮点数表示法

其中符号位为第31位,当脉冲边沿差值小于0则为1,反之则为0;阶码则为需转换数据data的指数域;尾数则为需转换数据data的二进制形式并去掉除符号位的最左侧的1之后所剩下的数[3]。即可以总结下面的公式(2)。

(2)

其中:1.M表示在M的二进制数据形式的最左侧补上一个1后的数。通过上述方法在FPGA编程实现脉冲边沿差值和相对应的时钟计数值的单精度浮点格式转换。

步骤5:转速计算。

通过调用Floating Point IP核中的浮点乘法模块和浮点除法模块来进行浮点乘除法,再依据脉冲边沿差值、时钟计数值,最终就可以FPGA中算出电机转速speed(脉冲/秒)。

图5 程序流程图

步骤6:数据的存储与传出。

首先调用存储单元EMB的IP核,然后可将脉冲边沿计数值和转速speed等存储起来。由于在芯片CME-M7里面ARM和FPGA共享EMB的地址,所以ARM可以很方便的对FPGA存储在EMB里的数据进行读取,并将转速乘以当量转换成度每秒(°/s),并通过串口传出至PC机显示。整体程序流程图见图5。

4 实验验证与分析

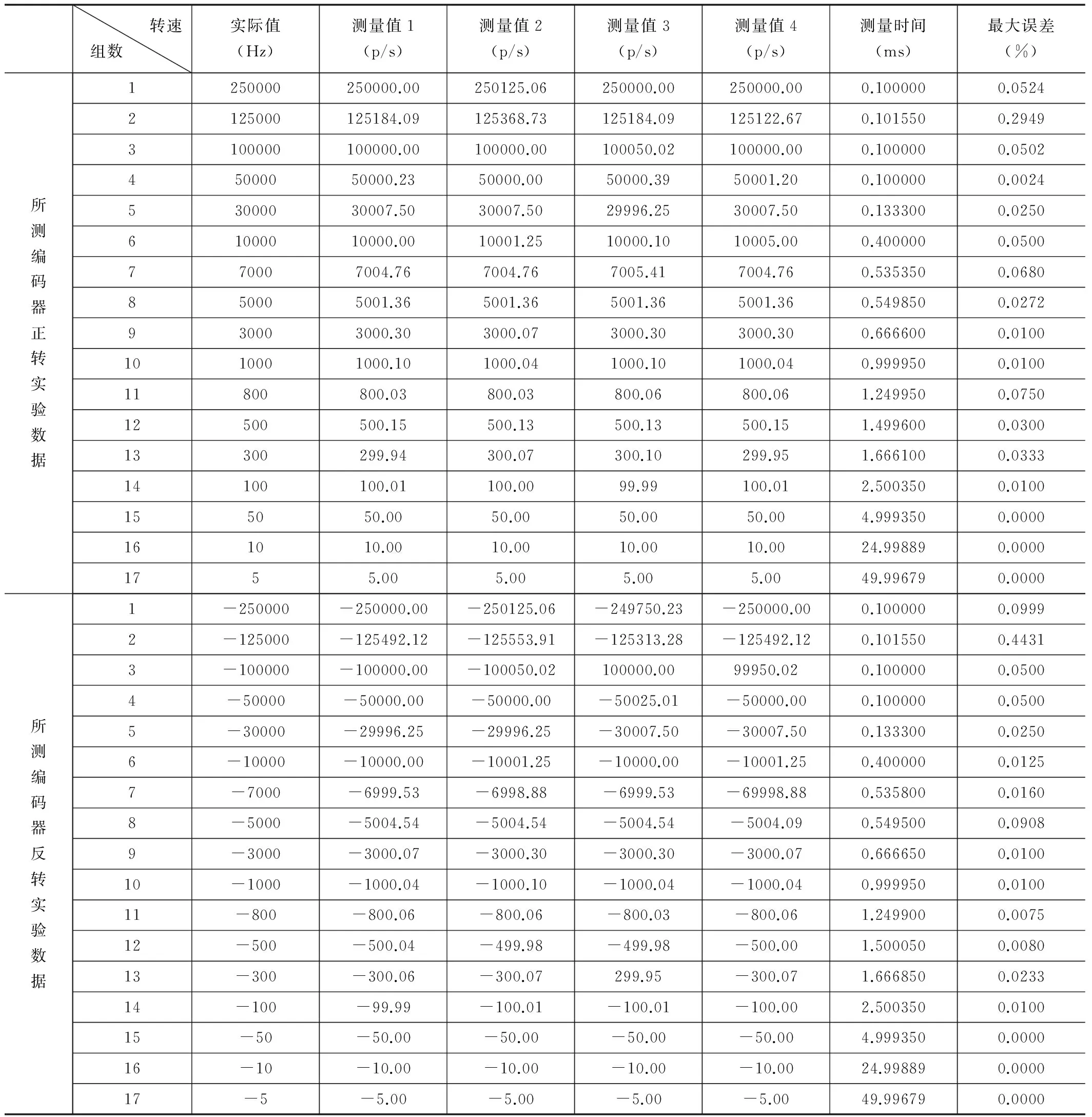

为了验证所设计的测速电路,本文使用多功能脉冲信号源来产生模拟每圈60 000线束的增量式光电编码器的相位相差90°的A相脉冲和B相脉冲,并将多功能脉冲信号源接入所设计的基于国产FPGA 的增量式光电编码器测速电路系统中进行对比测速验证。表1记录了在不同的转速下进行对比测速验证的实验数据。表1中,p/s表示每秒发生的脉冲数,即等同于单位Hz;实际值表示多功能脉冲信号源发出的模拟的A相脉冲和B相脉冲的频率;测量值表示的是所设计的测速电路所测量的脉冲频率;测量时间表示不同转速下测量速度所需的测量时间。

从表1的数据可以知道,实验时分别在250 kHz~5 Hz的脉冲频率之间取了17组不同的频率进行测量,并从正反转两个方向进行了实验验证。当给所设计的测速电路输入不同的脉冲频率时,测速时间随着脉冲频率的增加而缩短,随着脉冲频率的减小而加长,当脉冲频率在250 kHz~5 Hz之间变动时,对应的测速时间范围为100 μs~50 ms之间变动,其中测速时间可以依据具体伺服控制系统进行调整,以满足响应时间的要求;测速误差的最大值为0.443 1%,最小值为0%;上述结果说明本文设计的测速电路得到了实现,同时也证明了测速电路测速范围宽、测量精度高等特点。

5 结束语

本设计研究针对于目前伺服测速系统的发展方向--更高的采样频率、更简洁的算法和更强的实时性,采用了一种改进的变M/T测速方法,并利用该方法在国产FPGA上实现了基于增量式光电编码器的测量电机转速的电路,同时,在国产FPGA里面也实现了浮点运算,使得可以直接从FPGA里面得到编码器的转速,这在很大程度上提高了测速电路的抗干扰能力,同时整个测速电路都是设计在FPGA逻辑里面的方式也大大提高了测速的实时性,而且所使用的FPGA芯片和FPGA编程软件完全是我国自主研发生产的,这增强了测速系统的自主性。经实验验证,所设计的测速电路能够满足现今伺服系统的对于测速方面的精度和动态响应速度的要求。

表1 实验对比结果

[1]文晓艳,等.增量式编码器测速的典型问题分析及应对策略[J].电工技术学报,2012,27(2):185-189.

[2] 李汉.一种光电编码器抗振动测速的方法[J] .电气传动,2010,40(6):78-80.

[3] 符茂松.32 位 IEEE 和 IBM 浮点数结构及其转换方法[J] .工程地球物理学报,2011,8(6):759-766.

[4] 李大英.基于FPGA的电机测速电路设计与实现[J] .机械设计与制造,2011,12(3):78-80.

[5] 梅荣军,等.基于FPGA的增量式编码器信号采集系统[J] .测控技术,2014,33(7):54-60.

[6] 王俊山,等.基于FPGA的增量型光电编码器抗抖动二倍频电路设计[J] .现代电子技术2010,9:157-159.

[7] 夏宇闻,等.Verilog数字系统设计教程[M] .北京:北京航天航空大学出版社,2005.

Research of Speed Measuring Circuit of Incremental Photoelectric Encoder Based on Domestic FPGA

Ma Lingzhi,Li Hong

(College of Electrical and Information Engineering, Changsha University of Science & Technology,Changsha410114, China)

It is very important to measure the speed of motor by using the incremental photoelectric encoder for the servo motion system. According to the requirement of frequency and real-time of the speed measuring system and combining with China’s own production of FPGA(Field-Programmable Gate Array)chip, it proposed a method by using domestic FPGA chip-CME M7 which embed ARM kernel as the developing platform of the hardware and Verilog HDL to programme to design a speed measuring circuit of motor of incremental photoelectric encoder based on domestic FPGA. Through the verification of the experiment, it is proved that the design of the speed measuring circuit is high precision, wide speed range, good real-time performance and strong anti-interference ability.

domestic FPGA; incremental photoelectric encoder; speed; verilog HDL

2015-07-18;

2015-08-27。

国家自然科学基金2010年资助项目(61074018)。

马玲芝(1989-),女,湖南郴州人,硕士研究生,主要从事电路与系统、测量与控制、FPGA应用方向的研究。

李鸿(1962-),男,浙江人,教授,博士,主要从事非电量电测和机电一体化、仪表及数控领域方向的研究。

1671-4598(2016)01-0233-04

10.16526/j.cnki.11-4762/tp.2016.01.064

TP274.2

A