基于S12X系列双核单片机的CAN网关设计

2016-09-07豆海利

冯 源,豆海利,赵 刚

(1.中国航空计算技术研究所,西安 710072; 2.空军工程大学 理学院,西安 710051)

基于S12X系列双核单片机的CAN网关设计

冯源1,豆海利2,赵刚1

(1.中国航空计算技术研究所,西安710072; 2.空军工程大学 理学院,西安710051)

集成XGATE协处理器内核的S12XE系列双核单片机具有处理速度快、反应时间短、功耗低等优点,在嵌入式应用中具有独特优势和很好的应用前景;文章采用16位双核单片机MC9S12XEQ512作为主控制器,以集成信号和电源隔离功能的CAN收发器芯片ADM3053来实现CAN接口电路,设计并实现了一个可以连接3个CAN通信子网的CAN网关,有效实现了系统的小型化、低功耗、低成本;采用双核处理技术来优化CAN网关的处理流程,由协处理器XGATE来处理各种中断,S12X主CPU则专注于协议处理和消息转发;实际应用表明,系统运行稳定可靠,与传统的采用单处理器实现的CAN网关相比,系统的数据吞吐能力和实时性得到了明显改善。

CAN网关;S12X主CPU;协处理器XGATE;精简指令流;软中断;信号量

0 引言

随着微处理技术的发展及复杂系统对微控制器的实时性和计算能力要求的日益提高,带协处理器的微处理器应用越来越广泛。美国Freescale公司推出的S12XE系列双核单片机,其内部集成了可编程RISC内核的XGATE协处理器,专门用来处理I/O和中断。其性能往往优于一个智能的DMA控制器,从而提高了系统的实时处理能力,减轻了主CPU的工作负荷,使得主CPU更多注重于处理系统核查、应用解算等任务。

CAN(controller area network),即控制器局域网,是一种有效支持分布式控制和实时控制的串行总线,具有分布性能好,可靠性高、扩展性好、成本低等优点,较好地解决了工业现场设备级(传感器、执行器、控制模块)的互连通信问题。在某些特定场合,如网络中节点数量过多、通信距离过长、不同波特率和应用层协议的两个CAN网络在数据交换时就需要增加CAN网关设备。

本文基于S12XE系列双核单片机MC9S12XEQ512设计实现了一种可以连接3个CAN通信子网的CAN网关设备,通过该网关能够实现子网之间消息的过滤、转发、流量控制、协议转换等功能。

1 XGATE的功能结构及中断配置

1.1XGATE的功能

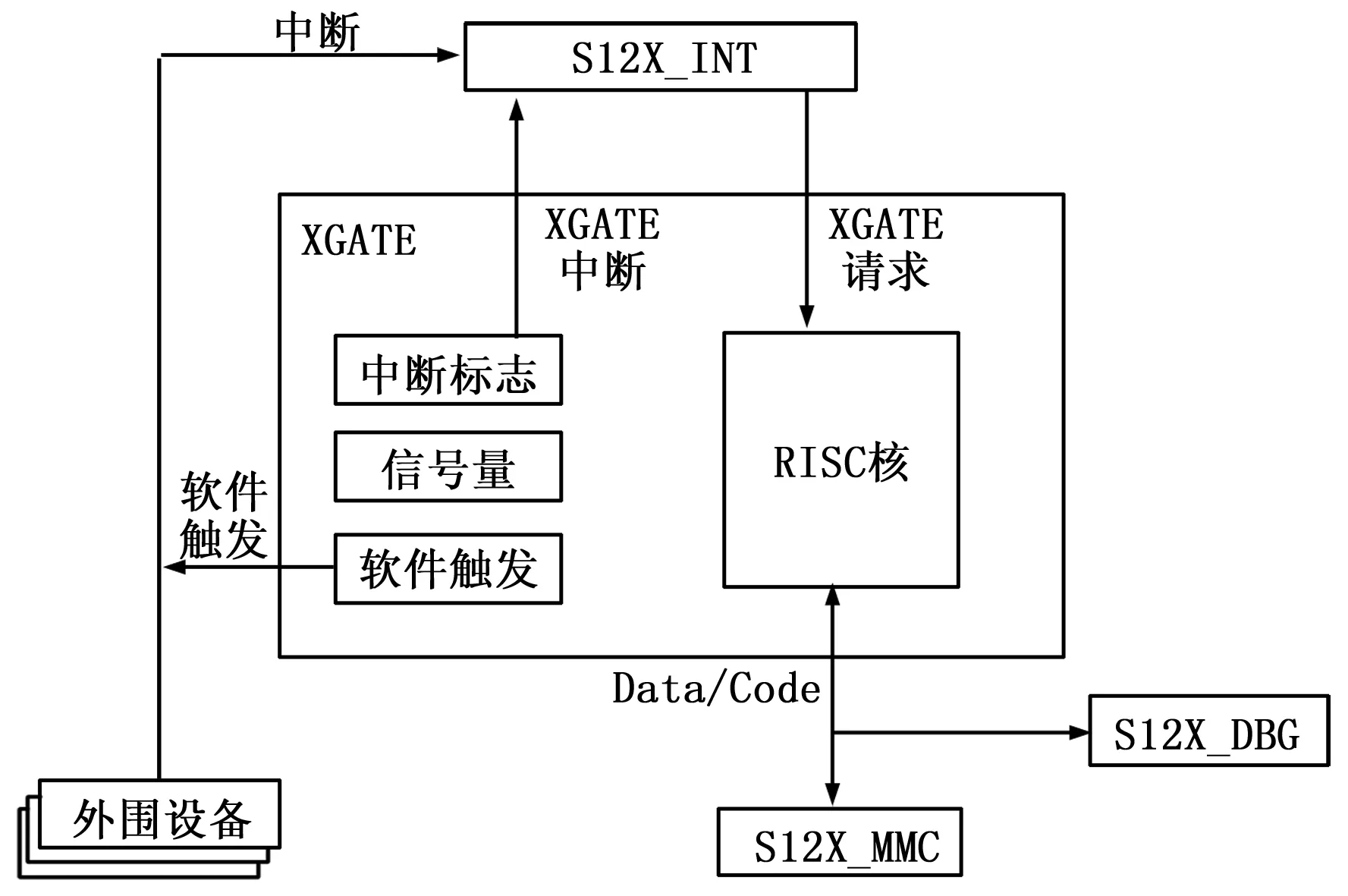

协处理器XGATE是专门为处理中断和I/O设计的,内部结构如图1所示。它采用精简指令流(RISC)结构,速率比S12X主CPU快1倍,中断处理更快。XGATE和主CPU之间通过片内的双口RAM交换数据,同时两个内核之间可以互发中断请求。当主CPU与协处理器存在竞争问题时,S12X单片机采用了8个内部硬件信号量予以解决。

图1 XGATE内部结构框图

1.2S12X的中断配置及响应

在S12XE系列双核单片机中,可以选择主CPU或协处理器XGATE来响应外部中断事件。图2是典型的S12X的中断配置及响应,在每个中断的配置寄存器INT_CFGDATAx中,通过开关信号RQST来选择中断处理内核,ILVL[2:0]域定义了中断优先级,它在两个内核中都起作用。在典型的双核应用中,先由XGATE来响应中断,当XGATE执行完中断服务程序后,通知S12X主CPU并将处理的结果提交给它。这样由XGATE负责与底层硬件密切相关的驱动,S12X主CPU只需关注上层的应用控制算法,从而在提高应用程序反应速度的同时减少了主CPU的中断负荷。

图2 S12X的中断配置及中断响应

2 CAN网关的需求分析

本文所要设计的CAN网关要求具备3个CAN通道,分别连接3个CAN通信子网。其中CAN0通道连接1个通信速率为500 Kbps的高速CAN子网CAN0,CAN1和CAN2通道分别连接1个通信速率为125 Kbps的低速CAN子网CAN1和CAN2。

网关的具体功能要求如下:

1)低速CAN子网CAN1和CAN2上使用相同的协议数据格式,高速CAN0子网上使用另一种协议数据格式,网关需要完成两者之间的协议数据格式的转换;

2)来自于低速CAN子网CAN1和CAN2上的消息可以全部转发到高速CAN0子网上;

3)针对低速CAN1和CAN2网络,网关的对应通道分别设置了消息过滤表,来自于高速CAN0子网上的消息,经过消息过滤后,转发到低速CAN1和CAN2子网上;

4)低速CAN1和CAN2网络之间不要求数据转发。

3 CAN网关的硬件设计

3.1系统结构和原理框图

本文设计的CAN网关的系统结构和原理框图如图3所示,采用集成了4个MSCAN模块的双核单片机MC9S12XEQ512作为该网关的主控芯片,负责对CAN控制器的初始化,并控制消息的接收、消息拆装与重组、过滤和转发等。CAN物理层接口采用了ADI公司的集成CAN收发器ADM3053,它是将CAN收发器与iCoupler磁耦隔离技术和isoPower集成式隔离DC/DC转换器集成在一起,由单芯片实现了CAN接口信号和供电的完全隔离,有效实现了系统小型化、低功耗、低成本。此外,本设计中增加了接口防护电路,包括共模电感和瞬态抑制保护器件(TVS)。

图3 CAN网关的系统结构和原理框图

3.2硬件实现

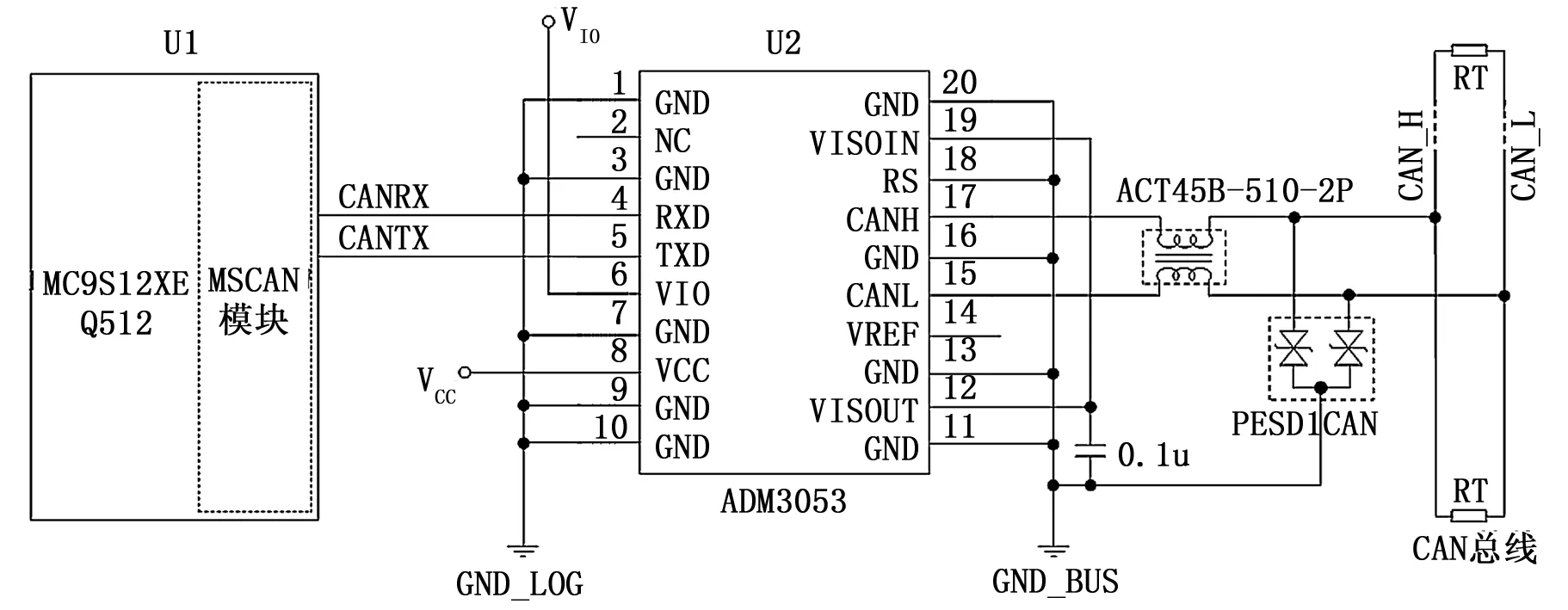

本文中CAN接口电路图如图4所示。

图4 CAN接口电路原理图

ADM3053根据隔离功能划分为逻辑端(图中左侧)和总线端(图中右侧),两端连接独立的电源和地信号。

ADM3053的逻辑端与主控芯片MC9S12XEQ512相连,管脚接线如下:

1) MC9S12XEQ512中MSCAN模块的接收引脚CANRX和发送引脚CANTX分别与ADM3053中接收器输出引脚RXD和驱动器输入引脚TXD相连;

2) ADM3053内部信号隔离功能由逻辑端的VIO引脚提供电源,它与MC9S12XEQ512的I/O供电电源相连;

3) ADM3053的内部电源隔离功能由逻辑端的VCC引脚提供电源,它与+5 V电源相连;

4) ADM3053逻辑端的地信号GND_LOG与MC9S12XEQ512的电源地信号一致。

ADM3053的总线端与外部总线接口防护电路相连,管脚接线如下:

1) ADM3053的内部电源隔离输出引脚VISOUT与CAN收发器供电输入引脚VISOIN连接,这两个引脚外部分别通过滤波电容接地;

2) CANH和CANL通过共模电感ACT45B-510-2P与系统中的CAN总线相连,总线两端要求分别接入120 Ω端接电阻;

3) CANH、CANL与总线地信号GND_BUS之间连接TVS管PESD1CAN,用于抑制瞬态干扰。

4 CAN网关中双核工作体制的构建

4.1数据共享的实现

1)定义共享数据区

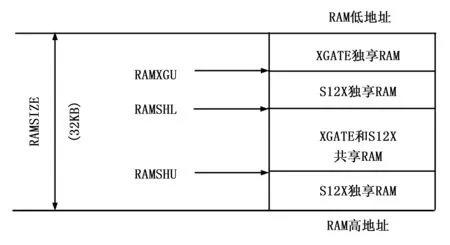

S12X主CPU和协处理器XGATE之间交互数据是使用片内双端口RAM,开辟消息缓冲区,以共享内存的方式实现。通过设置边界寄存器的值,可以将其划分为XGATE独享RAM、S12X独享RAM、XGATE与S12X共享RAM几个部分,如图5所示。

图5 RAM分配区

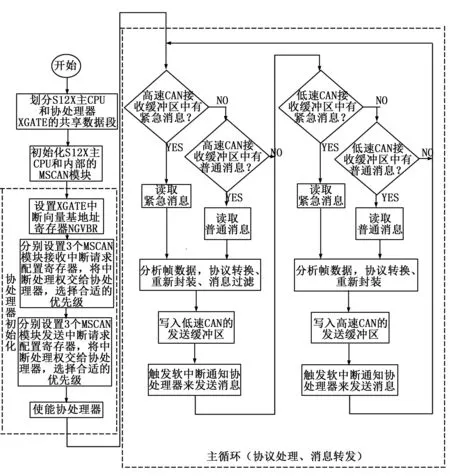

图7 CAN网关的工作流程图以及双核处理器的功能划分

在上述的RAM分配方案中,共享RAM空间用于S12X主CPU和XGATE之间交换数据,消息缓冲区就定义在该区域中。XGATE独享RAM用于存放XGATE的应用程序,而XGATE应用程序在RAM中运行比在Flash中运行速度快一倍,同时避免了由于竞争影响主CPU的运行速度。本设计中,S12X主CPU工作时钟频率是50 MHz,XGATE以最高100 MHz的时钟频率运行片内RAM中的程序。

2)共享资源的互斥访问

为了保证共享数据的完整性,使用其内部集成的8个硬件信号量来同步两个内核对共享数据的访问。

S12X主CPU和XGATE协处理器之间解决共享资源竞争的程序框图如图6所示。在XGATE应用程序中,锁定信号量指令的后面一定要紧跟一条BCC指令,判断锁定是否成功。如果不成功,则通过BCC指令再次执行锁定操作,直到锁定成功。在S12X主CPU应用程序中,给XGATE信号量寄存器的相应位写1的指令之后一定要紧跟一条位测试指令,读信号量寄存器中的相应位,判断S12X主CPU是否已经成功锁定信号量。如果相应位仍为0,则接着再次执行给信号量寄存器的相应位置1的指令,以等待XGATE释放该信号量。

4.2S12X主CPU与XGATE的相互中断

S12X主CPU和XGATE之间可相互中断以同步它们的运行。XGATE有一个特殊的指令SIF,用于向S12X主CPU提交中断。通常SIF为XGATE线程的最后一条指令,用以触发S12X主CPU中断。另外XGATE有8个软件中断源,S12X主CPU可以通过置位或清除XGATE软中断触发寄存器(XGSWT)中的相应位来触发或清除这8个中断。

5 CAN网关的软件设计

5.1网关工作流程的设计

为了缓解网关工作时可能出现的数据阻塞和延迟问题,增强系统的数据吞吐能力和实时性。本文采用主处理器与协处理器并行协调工作的方式来设计工作流程,实现网关的功能,如图7所示。需要说明的是,图中仅展示了1路高速CAN与1路低速CAN之间的转换流程,根据处理流程可以方便地扩展到与2路低速CAN之间的转换。

构造双核应用程序的过程实际上就是将CAN网关的整个处理流程尽量合理分布到主CPU和协处理器上,完成双内核之间的通信并响应外设事件的过程。这个双核程序相当于将整个应用程序划分为两级,第一级运行在S12X主CPU上,包括main()函数和S12X主CPU的中断服务程序;第二级运行在协处理器XGATE上,执行XGATE中断服务程序。这样由XGATE完成底层外设的初级处理,由S12X主CPU来完成网关的协议处理和消息转发等高层应用。

在双核单片机的工作过程中,这两个处理器的工作方式是不同的,S12X主CPU的工作是主动的,始终在运行;而协处理器XGATE的工作是被动的,是由中断触发的。

5.2数据结构

数据结构的设计主要包括消息缓冲区和消息过滤表。

1)消息缓冲区:

本文针对每一路CAN接口,都设置了独立的发送和接收缓冲区。接收缓冲区用于存放来自上一级子网,等待处理的消息。发送缓冲区用于存放经过协议转换和消息过滤后等待发送到下一级子网的消息。缓冲区采用环形缓冲结构,并根据消息类型划分为紧急消息缓冲区和普通消息缓冲区。

2)消息过滤表:

为了实现高速CAN子网向低速CAN子网转发过程的消息过滤功能,在网关的低速CAN通道上需要设置消息过滤表。消息过滤表中只存放需要转发到下一级CAN子网的CAN消息ID,并且按照消息ID由小到大的顺序排列。

在系统启动时,对该表的内容进行初始化。在消息转发过程中,以CAN消息ID作为关键字来搜索此表,如果匹配成功,就转发消息,匹配失败则不需要转发,该消息就被滤除。查找算法采用典型的折半查找实现即可。

5.3S12X主CPU程序设计

在S12X主CPU上运行的程序包括main()函数和S12X主CPU的中断服务程序。

1)S12X主CPU的main()函数:

main()函数流程图如图8所示,在main.c文件中首先按照发送和接收缓冲区的数据结构来定义各个缓冲区变量,然后将其声明为全局变量,并分配到共享存储空间中。在main()函数中先配置S12X主CPU的时钟和锁相环,然后初始化MSCAN模块和XGATE协处理器,最后进入主循环处理流程。在主循环中,依次轮询高速和低速CAN通道的接收缓冲区,分析帧数据,进行协议转换、消息过滤后写入到下一级CAN子网的发送缓冲区,最后触发软中断通知协处理器来发送消息。

图8 S12X主CPU的main()函数流程图

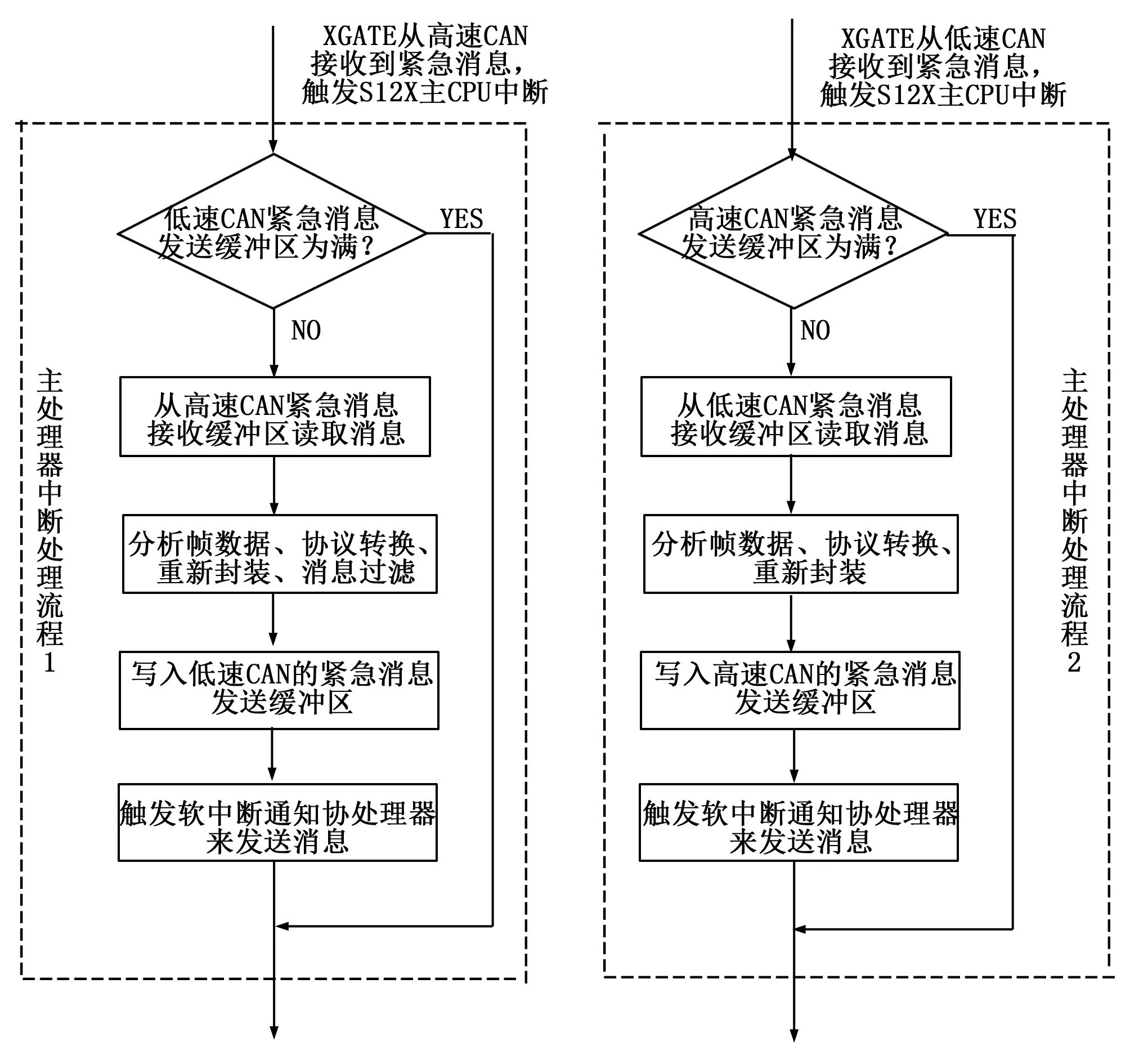

2)S12X主CPU的中断服务程序:

S12X主CPU的中断处理流程图如图9所示,S12X主CPU的中断服务程序是用于直接处理XGATE接收到的紧急消息。当XGATE接收到紧急消息时,写入接收缓冲区,然后通过SIF指令向S12X主CPU提交中断;主CPU响应中断,在中断服务程序中立即读取紧急消息并进行解析、协议转换和消息过滤,然后写入到下一级子网的发送缓冲区,最后触发软中断通知协处理器来发送消息。

图9 S12X主CPU的中断处理流程图

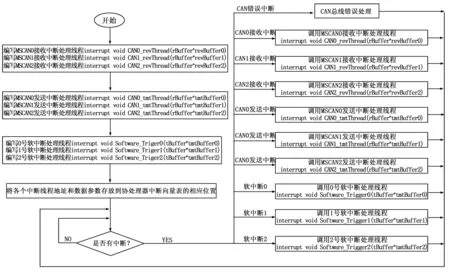

5.4协处理器XGATE程序设计

XGATE代码就是一段段独立的中断服务程序,没有主程序。XGATE的中断服务程序也称为线程。XGATE代码的执行是由中断驱动的,在没有中断时,进入休眠态,不执行任何指令,处于低功耗状态。

在本文的设计中将MSCAN模块的接收中断、发送中断和软中断的处理交由XGATE负责。XGATE的工作流程如图10所示,需要编写各中断的中断服务程序,并根据各个中断服务程序的起始地址和参数来填写XGATE中断向量表。

图10 协处理器工作流程

在图7的CAN网关的工作流程图中,已经描述了协处理器XGATE响应软中断、MSCAN发送中断和接收中断后的CAN消息发送和接收的详细处理过程。

在MSCAN模块接收到CAN消息时,会触发XGATE的CAN消息接收中断处理线程interrupt void CANx_rcvThread( rBuffer *rcvBufferx )。对于接收到的数据,区分紧急消息还是普通消息。如果XGATE接收到紧急消息时,写入接收缓冲区,然后通过SIF指令向S12X主CPU提交中断;主CPU响应中断,在中断服务程序中立即读取紧急消息并进行解析、协议转换和消息过滤,然后写入到下一级子网的发送缓冲区。如果XGATE接收到普通消息时,只写入接收缓冲区,但不向S12X主CPU提交中断,只等待S12X主CPU在主循环中轮询到接收缓冲区才对该消息进行处理,然后写入到下一级子网的发送缓冲区。

CAN消息的发送功能是通过引入两个独立的中断来实现,分别是主CPU触发的软中断线程interrupt void Software_Triggerx(tBuffer *tmtBufferx )和MSCAN模块的发送中断处理线程interrupt void CANx_tmtThread(tBuffer *tmtBufferx )。当S12X主CPU完成消息解析、协议转换和消息过滤,并将其写入到下一级子网的发送缓冲区后,主CPU通过软中断来通知协处理器进行CAN消息的发送。另外由于使能了MSCAN模块的发送中断,一旦MSCAN内部的发送缓冲区中出现“空”窗口可以写入消息时,就会立刻向协处理器触发发送中断,由协处理器负责CAN消息的发送。

6 结束语

当前的CAN网关绝大多数是采用单处理器实现,为了缓解网关工作时可能出现的数据阻塞和延迟问题,增强系统的数据吞吐能力和实时性,笔者采用主处理器与协处理器并行协调工作的方式来设计工作流程,实现了一个可以连接3个CAN通信子网的CAN网关。

在CAN网关的双核应用程序中,由协处理器XGATE全面负责各种中断响应,如3路CAN通道的发送中断、接收中断、错误中断等,而S12X主CPU则专注于协议处理和消息转发。充分利用S12X主CPU和XGATE之间可以相互中断的机制,来同步双核程序的运行,有效实现了CAN网关的整个处理过程。

[1]邵贝贝,宫辉.嵌入式系统中的双核技术[M].北京:北京航空航天大学出版社,2008.

[2] 罗峰,孙泽昌.汽车CAN总线系统原理、设计与应用[M].电子工业出版社,2010.

[3] 王宜怀,曹金华.嵌入式系统设计实战-基于飞思卡尔S12X微控制器[M]. 北京:北京航空航天大学出版社,2011.

[4] 卢玉传,杜志岐,樊江滨,等.车载双路CAN总线冗余网关的设计[J].车辆与动力技术,2012(1): 45-50.

[5] 李广鑫,秦贵和,刘文静,等.CAN总线网关的设计与实现[J].长春邮电学院学报,2010,28(2): 166-171.

[6] 闫海明,冯源,田苗.基于DSP内嵌ECAN模块的总线接口设计[J].现代电子技术,2013,36(11): 112-115.

[7] Ross Mitchell.Tutorial:Introducing the XGATE Module to Consumer and Industrial Application Developers (AN3224) [R].Freescale Semiconductor,2006.

[8] Steve McAslan.Using XGATE to Implement a Simple Buffered SCI (AN3144) [R].Freescale Semiconductor,2005.

[9] Joachim Krücken.How to Configure and Use the XGATE on S12X Devices (AN2685) [R].Freescale Semiconductor,2004.

Design of CAN Bus Gateway Based on S12X Series Dual-core MCU

Feng Yuan1,Dou Haili2,Zhao Gang1

(1.Aeronautics Computing Technique Research Institute, Xi’an710072, China;2.College of Science, Air Force Engineering University, Xi’an710051, China)

S12X series dual-core MCU with a coprocessor XGATE has the advantages such as high speed of data processing, short reaction time and low power consumption. So it has more good application prospect in the field of embedded application. In this design, the 16-bit dual-core MCU named MC9S12XEQ512 has been selected as the main processor. The CAN transceiver chip ADM3053 has been used to implement the CAN interface circuit, in which CAN transceiver, the signal isolation function and isolated DC-to-DC converter are all integrated. The paper describes the design and implement of CAN gateway having three CAN interfaces for solving the CAN network's extending and interconnection, achieving the purposes of interface miniaturization, low power consumption and low cost. The technology of dual processors in embedded system design has been also applied to optimize the performance of the gateway. The coprocessor XGATE is used to handle the miscellaneous interrupts and the main processor S12X CPU is used to analyze the protocol and exchange messages. The application results show that the gateway can work stably and reliably. Compared with the existing gateway realized by the traditional single core processor, the performance of data throughput and reliability has been improved.

CAN gateway;S12X CPU;coprocessor XGATE;RISC;software triggers;semaphores

2015-03-13;

2015-09-16。

上海市研究生教育创新计划学位点引导布局与建设培育项目(13sc002)。

冯源 (1981-) ,男,陕西西安人,硕士,工程师,主要从事机载网络通信技术方向的研究。

1671-4598(2016)01-0191-05

10.16526/j.cnki.11-4762/tp.2016.01.053

TP393

A