基于FPGA的PLC并行执行定时器/计数器的设计

2016-09-07徐晓宇李克俭蔡启仲潘绍明

徐晓宇,李克俭,蔡启仲,潘绍明,余 玲

(1.广西科技大学 电气与信息工程学院, 广西 柳州 545006;2.广西科技大学鹿山学院 电气与计算机工程系, 广西 柳州 545616)

基于FPGA的PLC并行执行定时器/计数器的设计

徐晓宇1,李克俭1,蔡启仲1,潘绍明1,余玲2

(1.广西科技大学 电气与信息工程学院, 广西 柳州545006;2.广西科技大学鹿山学院 电气与计算机工程系, 广西 柳州545616)

针对ARM+FPGA构建的PLC系统,分析PLC对定时器/计数器的功能需求,设计了可以并行执行的定时器/计数器,构建的定时器/计数器共用一个端口读写控制器与FPGA中央控制器进行数据通信,定时器/计数器内部工作是相互独立的,能够并行的工作,并通过使用地址映射存储器使得定时器/计数器的指令执行更加高效;对中央控制器与定时器/计数器的通信时序和通信格式进行了设计,方便了中央控制器对定时器/计数器的控制与测试;通过仿真测试,该定时器/计数器能够满足PLC定时器/计数器的基本功能,并且达到了稳定的定时/计数的设计要求。

PLC系统 ;定时器/计数器 ;并行执行;FPGA;通信格式

0 引言

PLC的内部资源包括内部继电器、专用继电器、数据存储区、定时器/计数器、保持继电器等,其中,定时器与计数器是PLC中最重要的资源之一[1]。

设计的ARM与FPGA协同工作的PLC中,将使用高速低功耗的ARM作为PLC的主控制器。双口RAM与ARM的快速GPIO端口相连接,作为ARM与FPGA之间的通信接口[2]。中央控制器主要用以完成对双口RAM内部ARM写入的数据进行读出、处理、整理和写入操作。多操作位逻辑运算

控制模块主要用以实现逻辑运算指令[3]。输入存储与读取控制模块主要用以读取外部开关量的状态信息[4]。数据输出控制模块主要用以将程序执行结果处理后驱动外部负载[5]。

1 PLC定时器/计数器功能需求和可重构设计

1.1定时器功能需求分析

定时器作为PLC重要的软元件,根据PLC的实际使用情况,定时器的数量设计为256个,

编号为T0~T255,其中T0~T199为通用型100 ms定时单位定时器、T200~T247为通用型10 ms定时单位定时器、T248~T251为积算型1 ms定时单位定时器、T252~T255为积算型100 ms定时单位定时器。

1.2计数器功能需求分析

根据PLC的实际使用情况,计数器的数量设计为235个,编号为C0~C234,其中C0~C100为断电复位型加计数器、C101~C200为断电保持型加计数器、C201~C220为断电复位型加减计数器、C221~C234为断电保持型加减计数器。

1.3定时器/计数器的可重构设计

基于FPGA的可重构技术,就是利用FPGA可以多次重复编程配置的特点,通过分时复用的方式利用FPGA内部的逻辑资源,使在时间上离散的逻辑电路功能模块能在同一FPGA中顺序实现的技术[6]。

设计的定时器/计数器为可重构的设计,最多可设计有256个定时器,235个内部计数器。可以根据具体工程应用来设计其内部定时器/计数器的数量,以达到对FPGA资源的灵活配置。

2 FPGA与定时器/计数器的通信端口和时序设计

2.1FPGA与定时器/计数器的通信端口设计

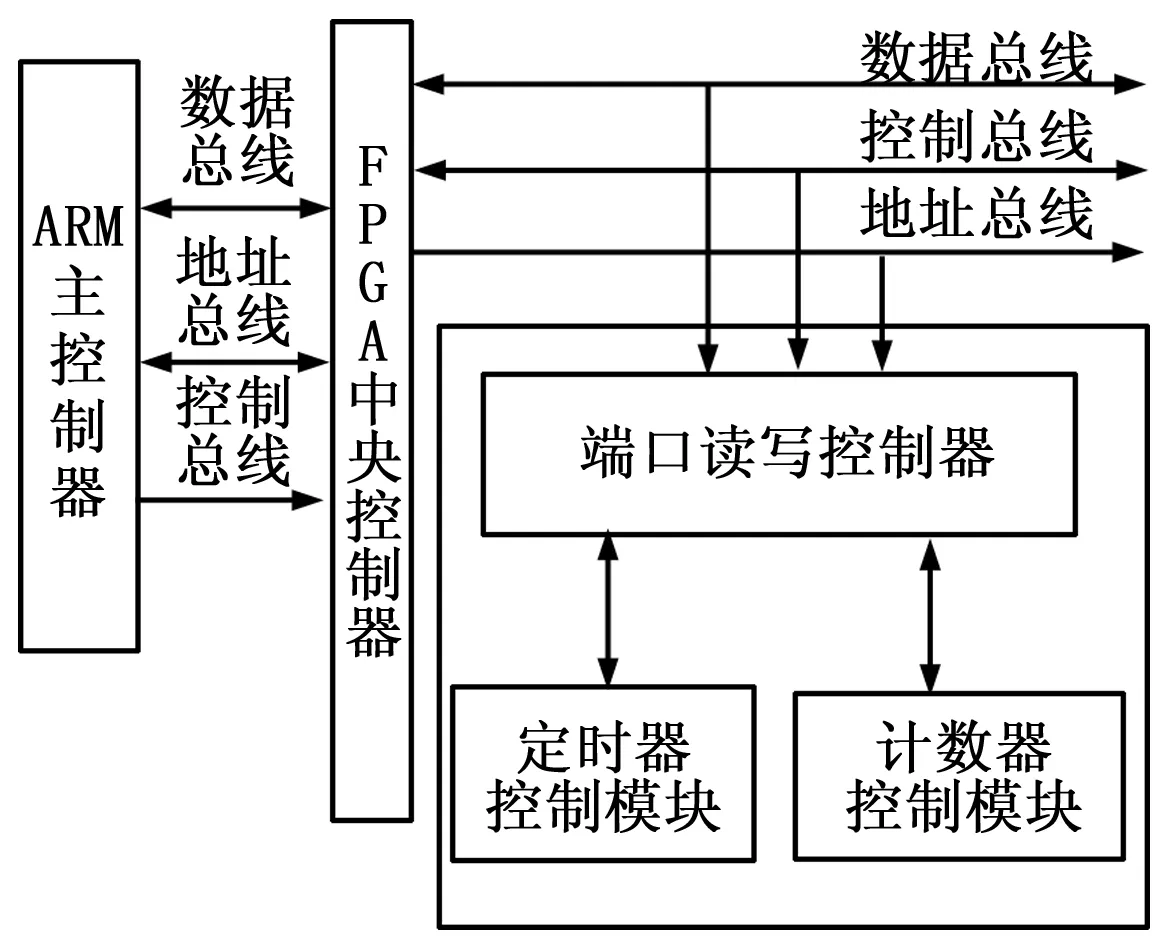

定时器、计数器通过总线的形式与FPGA中央控制器进行数据的交互,它们的工作是相互独立的,能并行地工作,相互之间不影响。它们使用相同结构和功能的端口读写控制器与中央控制器进行数据交互,在相同的时刻只能有一个模块占用总线与中央控制器进行通信。FPGA与定时器/计数器通信框图如图1所示。

图1 FPGA与定时器/计数器通信框图

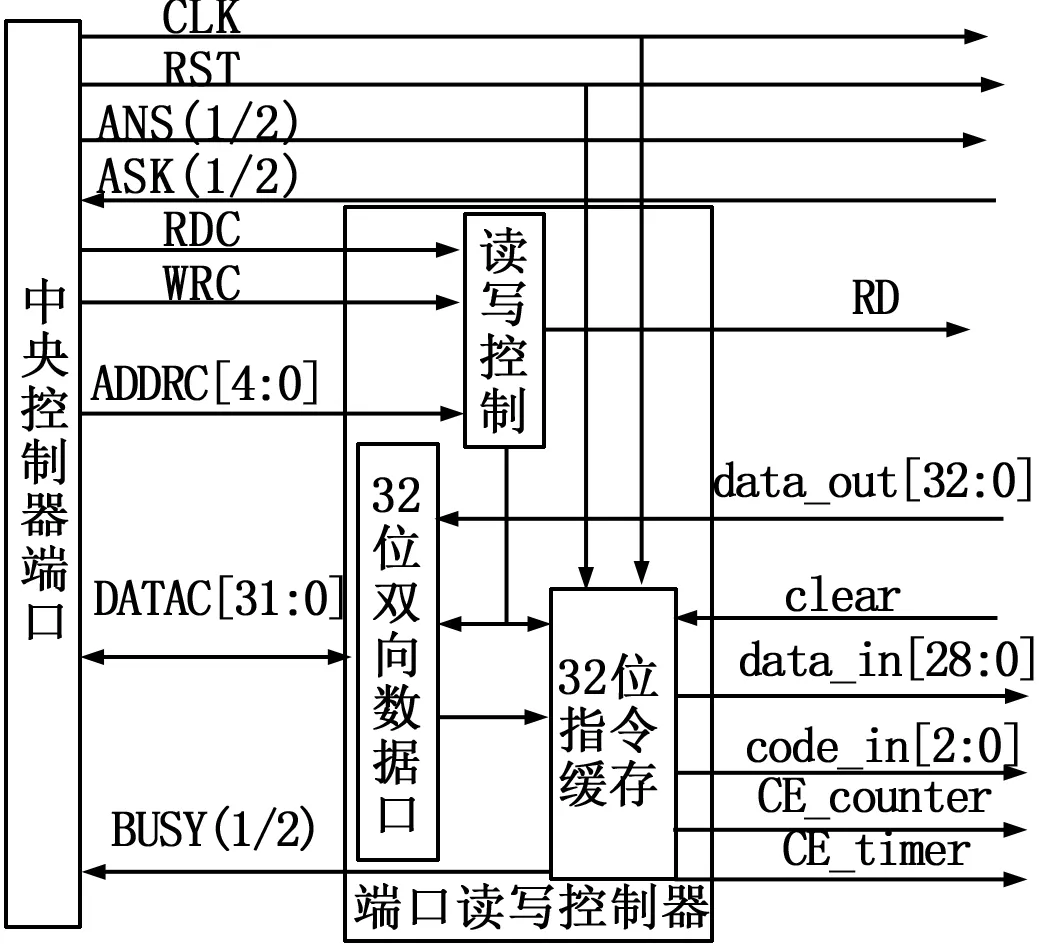

端口读写控制器主要实现与中央控制器的接口,定时器/计数器根据读写时序,通过端口读写控制器实现与中央控制器的数据交换。端口读写控制器结构图如图2所示。RST复位线使用低电平复位;ADDRC是模块地址线; RDC和WRC为低电平使能;ASK(1/2)与ANS(1/2)线均为低电平有效。读写控制模块通过判断RDC和WRC以及ADDRC的状态,控制组合逻辑三态门构成的32位双向I/O口DATAC进行数据的输入或输出。端口读写控制器的32位指令缓存可以存储一条指令,由29位data_in线输出对D28~D0即指令数据,由3位code_in线输出D31~D29即指令类型。CE指令执行标志线。当存储有指令时,置BUSY(1/2)线和CE线为低电平。

图2 端口读写控制器结构图

2.2定时器/计数器的读写时序设计

BUSY(1/2)线为忙信号输出线,当中央控制器检测到BUSY(1/2)线为高电平时才可以对定时和计数器进行写操作。当定时和计数器需要中央控制器对其进行读操作时,先通过定时和计数器读请求信号线ASK(1/2)发送一个时钟周期即20ns的请求脉冲,然后等待中央控制器读应答信号线ANS(1/2)上的应答脉冲,通过置低读信号线RDC同时选中定时和计数器地址即可从DATAC读取3个时钟周期即60 ns的数据。中央控制器同定时和计数控制模块的写时序、读时序如图3、图4所示。

图3 定时器/计数器写时序图图4 定时器和计数器读时序图

3 定时器/计数器模块设计

由ARM与FPGA协同构建的PLC控制系统,ARM作为PLC主控制器通过数据总线、地址总线、控制总线向FPGA发送指令命令,FPGA接收到ARM的指令命令之后,通过FPGA中央控制器与计数器进行通信。

3.1定时器设计

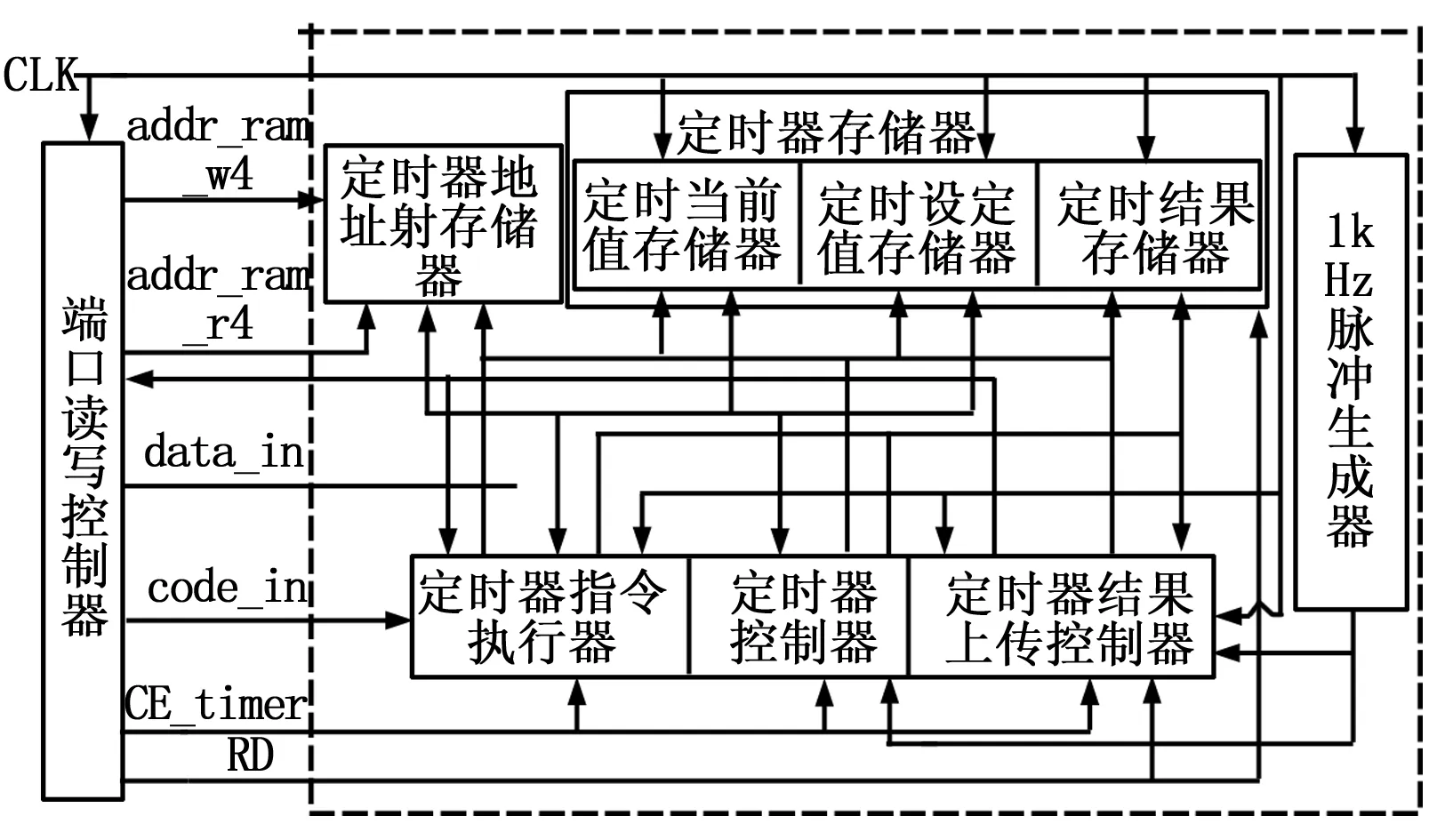

定时器总体结构图设计如图5所示,其中主要包含以下模块:端口读写控制器,定时器地址映射存储器,定时器存储器,定时器指令执行器,定时器控制器,1 kHz脉冲生成器。

图5 定时器总体结构图

3.1.1定时器地址映射存储器

定时器当前值和设定值在相应存储器中的存储位置与定时器本身的编号对应。当进行定时器操作或者进行定时器结果上传操作时,只需要从定时器地址映射存储器中的第一个地址开始顺序读取被使用的定时器的编号,以此编号为地址,便可以迅速地在定时存储器中找到使用了的定时器的相关数据进行操作,达到了提高系统执行效率的目的。

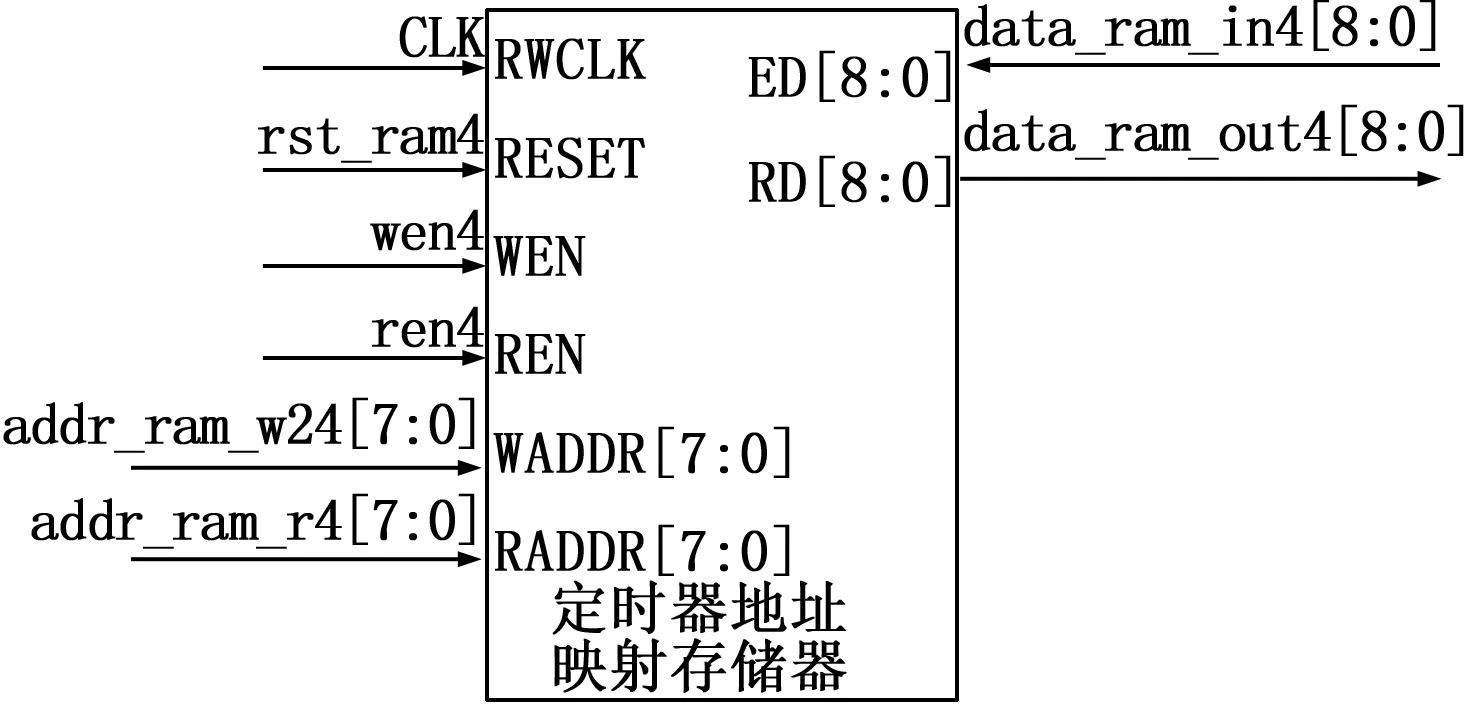

定时器地址映射存储器的封装如图6所示。RWCLK为读写时钟输入端口,读与写共用一个时钟;RESET为复位信号输入端口;WEN为写使能信号输入端口;REN为读使能信号输入端口;WADDR为写入地址输入端口;RADDR为读出地址输入端口;WD为写入数据输入端口;RD为读出数据输出端口。定时器地址映射存储器使用Libero8.3IDE提供的双端口存储器IP核生成。

图6 定时器地址映射存储器封装图

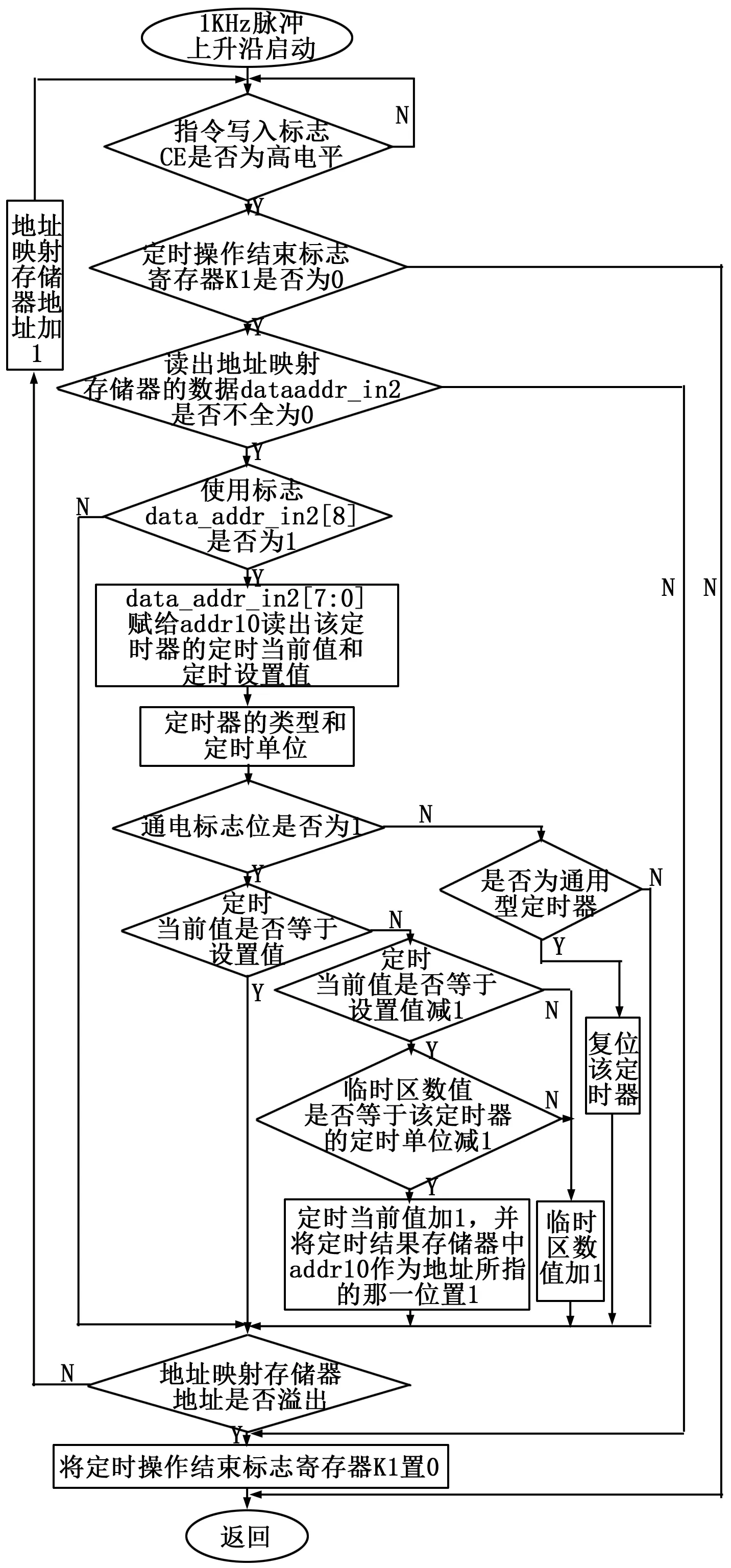

3.1.2定时器控制器

当1 kHz脉冲上升沿到来时定时控制器将会启动,当指令写入标志CE为高电平即定时器内没有指令且定时操作结束标志寄存器K1为0时,定时控制器将会执行定时操作。先通过从地址映射存储器中读取被使用了的定时器的编号;两个时钟周期后,从定时存储器中读取出的定时器的信息;第3个时钟周期后,对定时器的定时数据进行判断。操作完毕后将相关信息写入定时存储器。定时器控制器程序流程图如图7所示。

图7 定时器控制器程序流程图

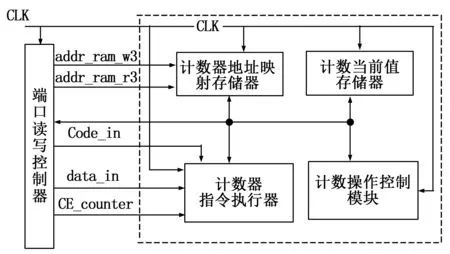

3.2计数器设计

根据功能需求分析所确定的计数器控制模块的功能设计计数器控制模块的功能模块,计数器结构设计如图8所示,其中包含以下功能模块:端口读写控制器,计数器地址映射存储器,计数器指令执行器,计数当前值存储器。

图8 计数器总体结构图

3.2.1计数器地址映射存储器

计数器地址映射存储器与定时器设计原理相同,使用Libero8.3IDE提供的双端口存储器IP核生成。

3.2.2计数器指令执行器

当中央控制器对定时器控制器发送指令之后,指令通过端口读写控制器被送至指令执行器。指令类型通过端口读写控制器的输出线code_in线输入指令执行器,指令数据通过端口读写控制器的输出 data_in线输入指令执行器,同时端口读写控制器置低CE线,启动计数器指令执行器。指令执行结束后,使端口读写控制器置高BUSY线和CE线。计数器指令执行器的结构如图9所示。

图9 计数器指令执行器结构图

4 中央控制器与定时器/计数器通信数据格式

设计的中央控制器与定时器/计数器通信的数据格式以指令及信息的形式,设计有5种指令,3种信息。

4.1中央控制器发送的指令数据格式

4.1.1复位指令

中央控制器发送给定时器或者计数器,当D31~D29为001时,对所有定时器/计数器进行复位;当D31~D29为010时,该复位命令对积算型的定时器、计数器和地址映射存储器不进行操作,复位指令数据格式表如表1所示。

表1 复位指令数据格式表

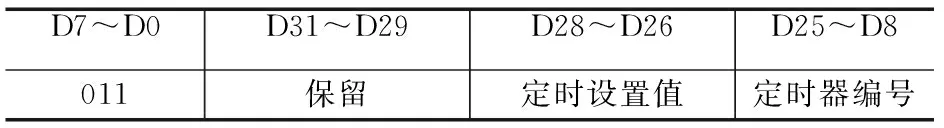

4.1.2初始化指令

该指令由中央控制器发送,是PLC用户应用程序执行复位指令后发送给定时器/计数器的指令。定时器初始化指令数据格式如表2所示。

表2 定时器初始化指令数据格式表

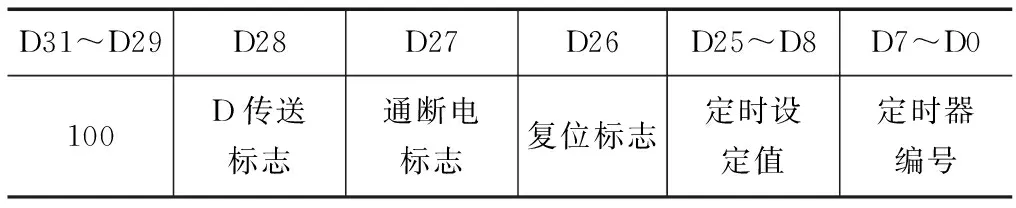

计数器初始化指令数据格式如表3所示。

表3 计数器初始化指令数据格式表

4.1.3断电保存指令

该指令由中央控制器发送,用于当PLC断电时中央控制器告知定时器、计数器进入断电保存阶段。指令数据格式如表4所示。

表4 断电保存指令数据格式表

4.1.4状态传送指令

该指令由中央控制器发送,将状态信息发送到相应的定时器计数器。定时器状态传送指令数据格式如表5所示。

表5 定时器状态传送指令数据格式表

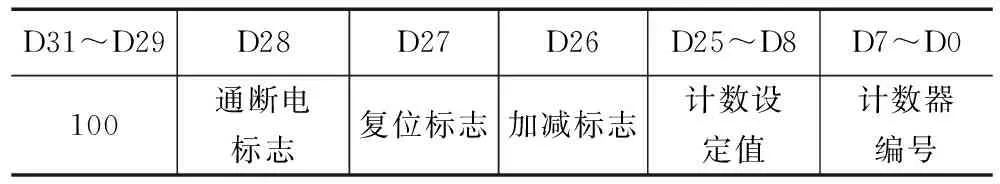

计数器状态传送指令数据格式如表6所示。

表6 计数器状态传送指令数据格式表

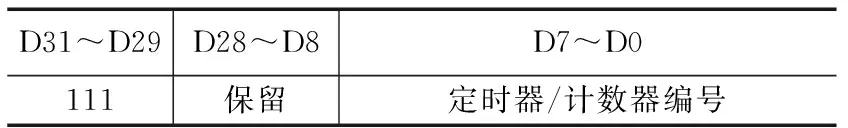

4.1.5读取当前值指令

该指令由中央控制器发送,用来读取定时器/计数器的当前值。指令数据格式如表7所示。

表7 读取当前值指令数据格式表

4.2定时器/计数器发送的信息数据格式

4.2.1定时结束/计数到信息

该信息由定时器、计数器发送,告知中央控制器该定时器/计数器编号的定时器定时结束信息或计数器计数到信息。

表8 定时结束/计数到信息数据格式表

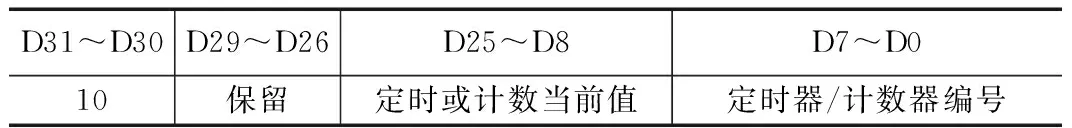

4.2.2定时/计数当前值信息

该信息由定时器、计数器发送,在接收到中央控制器读取当前值指令后发送给中央控制器。定时/计数当前值信息数据格式如表9所示。

表9 定时/计数当前值信息数据格式表

4.2.3断电保存信息

该信息由定时器、计数器发送,在接收到中央控制器断电保存指令后发送此信息给中央控制器,用以保存正在使用的积算型定时器、积算型计数器的当前值及其对应的定时器/计数器编号。数据格式如表10所示。

表10 断电保存信息数据格式表

5 仿真测试

在使用VerilogHDL语言完成硬件描述方面的设计后,使用ModelSim软件配合编写的testbench.v文件模拟中央控制器对定时器/计数器的输入,然后观察定时器/计数器的输出情况[7-8]。

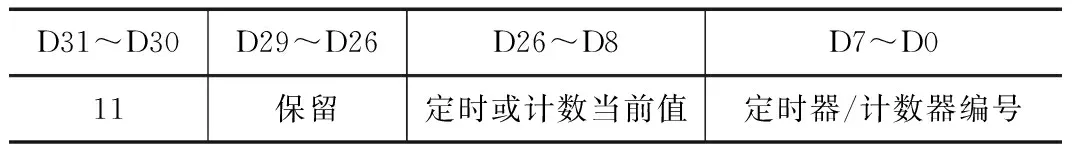

5.1定时器功能的仿真测试

设计的定时器模块地址为00100,先根据之前设计的中央控制器同定时和计数控制模块的通信协议初始化指令的数据格式,模拟中央控制器写入定时器初始化指令0x600001f9和0x600001fa初始化两个定时器。模拟中央控制器写入状态传送指令0x980002f9修改定时器F9H从断电至通电并将其设定值改为2 ms, 模拟中央控制器写入状态传送指令0x880001fa修改定时器FAH从断电至通电。分别在0.9 ms时和1.9 ms时观察定时器的输出情况。时序仿真的结果如图10所示。

图10 定时器时序仿真结果

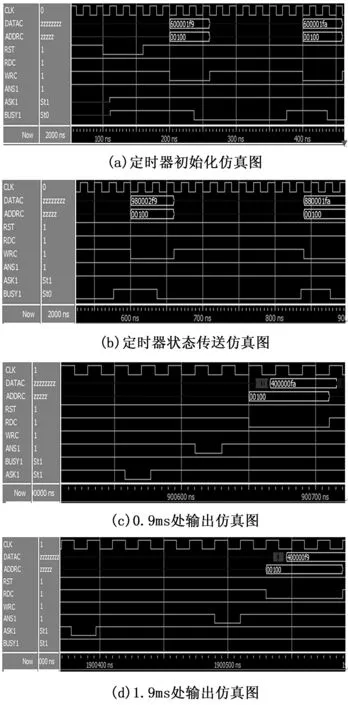

5.2计数器功能的仿真测试

设计的计数器模块地址为00010,模拟中央控制器写入计数器初始化指令0x6000000f和0x600000fa初始化两个编号为0FH(16)和FAH(250)的计数器。其中编号为0FH的计数器为通用型单增计数器,编号为FAH的计数器为积算型加减计数器。时序仿真的结果如图11所示。

图11 计数器时序仿真结果

由仿真测试可知,中央控制器通过状态传送指令告知计数器的驱动的通断电,由计数器根据驱动的通断电状态对计数器进行计数,计数器能正常工作。

6 结语

本文以ARM+FPGA构建了PLC系统,对此PLC系统的FPGA构建的定时器/计数器进行了介绍。然后对设计所使用的软件平台、硬件平台和编程语言进行了说明。同时对定时和计数控制模块的总体结构进行了设计,重点对端口读写控制器及中央控制器与定时和计数控制模块的时序进行了设计,设计了端口读写控制器的内部结构以及其读写控制的功能,设计的定时器/计数器具有可重构的功能,可以根据需要来增减定时器/计数器的数量和种类。

[1]王成福.可编程序控制器及其应用[M].北京:机械工业出版社,2007.

[2]孙培燕,李克俭,蔡启仲,等. FPGA数据总线宽度不相等的双口RAM的设计[J]. 科学技术与工程,2014,35:249-253.

[3]李静,蔡启仲,蒋玉新,等.基于FPGA 的多操作位逻辑运算控制器的设计[J].测控技术, 2015(2):81-84.

[4]李静,蔡启仲,张炜,等.基于FPGA的PLC输入存储与读取控制器的设计[J].仪表技术与传感器,2014(6):33-36.

[5]周曙光,李克俭,蔡启仲,等.基于FPGA的PLC位信息输出控制器设计[J].计算机测量与控制,2014(6):1750-1753.

[6]谷銮,徐贵力,王友仁. FPGA动态可重构理论及其研究进展[J]. 计算机测量与控制,2007,11:1415-S1418.

[7] 夏宇闻.Verilog数字系统设计教程[M](第2版).北京:北京航空航天大学出版社,2008.

[8] 王金明.数字系统设计与Verilog HDL[M](第3版).北京:电子工业出版社,2009.

Design of Parallel Operated Timer /Counter in PLC Based on FPGA

Xu Xiaoyu1,Li Kejian1,Cai Qizhong1,Pan Shaoming1,Yu Ling2

(1.Guangxi University of Technology,Liuzhou545006,China;2.Lushan College,Guangxi University of Science and Technology, Liuzhou545616, China)

PLC system based on ARM and FPGA construction, analysis the functional requirements of the PLC to the timer / counter, design can be executed in parallel timer / counter, construct the timer / counter. And shared with a single port read write data communication controller and FPGA as the central controller, timer / counter for internal work is independent of each other, parallel work. And through the timer / counter instruction operation more efficient by the use of memory address mapping. The communication between the central controller and timer / counter is designed, and the control and testing of the timer / counter is convenient. Through the simulation test, the timer / counter can satisfy the basic function of PLC timer / counter, and achieve the design requirements of the stability of timing / counting.

PLC system; timer / counter; parallel operated; FPGA; communication format

2015-09-22;

2015-11-09。

广西科学基金项目(桂科自2014GXNSFA118392);广西教育厅科研项目(2013LX092)。

徐晓宇(1988-),男,河北唐山人,硕士研究生,主要从事嵌入式系统与自动化装置方向的研究。

李克俭(1962-),女,湖北武汉人,教授,高级工程师,主要从事电力电子技术与自动化装置方向的研究。

1671-4598(2016)01-0182-05

10.16526/j.cnki.11-4762/tp.2016.01.051

TP332

A