雷达信号处理机并行自动测试系统设计

2016-09-07张晓曦吴翼虎刘永强

张晓曦,吴翼虎,刘永强

(中航工业西安航空计算技术研究所,西安 710065)

雷达信号处理机并行自动测试系统设计

张晓曦,吴翼虎,刘永强

(中航工业西安航空计算技术研究所,西安710065)

为了测试和评价某型雷达信号处理机的功能与性能,提供了一种以PCI总线为基础,结合虚拟仪器、数据库和直接数字频率合成等技术的多机并行自动测试系统设计,实现了为雷达信号处理机提供雷达回波模拟、高稳定度ADC采集时钟和多通道多类型信号输入,重点完成对雷达信号处理机多类型通讯总线测试和关键性能实时检测与分析,结合典型产品定量给出测试结果并分析,验证了测试系统的有效性。

雷达;自动测试;多机并行;实时

0 引言

现代雷达作为军民两用的重要设施,已在国防建设和国民经济发展中发挥着重要作用。现代雷达系统复杂性不断提高,涉及微波、高频、脉冲、数字、直流、开关量等各种信号和ARINC429、RS422、SPI和USB等多种总线接口,使得自动测试技术在雷达的研制、生产、维护和故障检测等方面中起到的作用日益突出,因此操作方便、功能齐全自动测试系统(ATS)成为现代雷达研制和生产的必需设备。设计一种结合ARINC429通讯总线、PCI总线、虚拟仪器(VI)技术和网络化体系结构等技术和方法的雷达信号处理机机自动测试系统,可并行对多台信号处理机进行主要性能参数测试,该系统平台可靠性好、测试精度高、软件架构易扩展,满足雷达信号处理机硬件平台多机并行测试的需求。

1 ATS需求分析和功能组成

1.1待测单元描述

待测雷达信号处理机为弹载雷达信号处理硬件平台,包括4路AD采集单元、通信接口单元、离散量控制单元等功能模块。雷达信号处理机对雷达接收机解调后的基带信号进行采集处理,并与制导系统中飞控、波控和遥测等功能单元进行通信。

1.2ATS功能需求及组成

通过对被测单元的分析,ATS需要提供如下功能:为信号处理机提供+5 V和±15 V电源、提供4路中频雷达回波模拟信号、提供雷达信号处理机的工作时钟及采样时钟、多路位指令输入输出信号和多路同步脉冲输出信号及其相关信号测试,以及ARINC429接口、SPI接口,USB接口和RS422等多种接口及测试。

ATS是集信号发生、信号检测和通讯测试为一体的雷达信号处理机综合测试系统,包括硬件平台和软件平台两大部分。

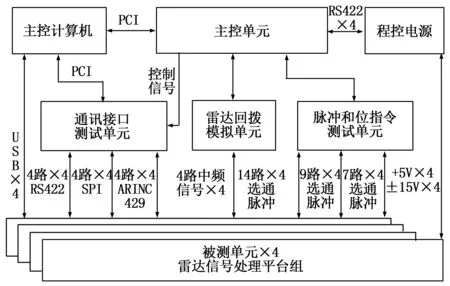

2 ATS硬件设计

硬件平台主要包括主控计算机、程控电源、频谱分析仪、主控制器模块、中频信号源(包括采样信号发生器、基准信号发生器)、通讯接口测试模块和同步脉冲/位指令测试模块组成。整个硬件平台以工业控制微机(主控计算机)为核心,通过标准的仪器总线、网口、RS232和PCI等总线将测试资源连接,构成测试仪器网络,由虚拟仪器软件进行统一控制。主控计算机通过PCI总线访问主控制器模块和各个通讯模块,主控制器模块通过ARINC429总线和被测单元交互信息。ATS硬件平台系统结构如图1所示。

图1 ATS硬件平台系统结构

2.1主控计算机

主控计算机是整套系统的控制中心,负责整套系统的管理协调,安装有Windows操作系统以及应用软件,它通过PCI总线来控制测试板卡资源,负责系统所有仪器资源调度及测试流程控制执行等,是整个测试设备的顶层控制中心,被测单元的USB接口和主控计算机直接相连。

2.2主控单元

主控单元是主控计算机控制下的二级调度核心,主控计算机通过PCI总线访问和控制主控单元,主控单元通过ARINC429总线与被测单元进行信息交互,它能够产生各类控制信号,完成主控计算机各项测试任务到各功能单元任务下发和被测单元反馈测试结果数据的上报。通过RS232接口控制程控电源输出。

2.3雷达回波模拟单元

该单元恒温晶振为基准,经滤波、倍频后输入到AD9910,DDS芯片在主控单元控制下按照测试项目需要,经过滤波、倍频、放大、衰减和调制等功能电路,产生4路的模拟基带的中频信号,该单元结构如图2所示。

图2 雷达回波模拟单元

为了模拟实际应用场景,ADC采样时钟输入采用另外的一路恒温晶振经滤波放大处理后输出。

2.4通讯接口测试单元

通讯接口单元包括ARINC429通讯模块、SPI串行通讯模块和RS422通讯模块,在主控制器的作用下,ATS系统通过ARINC429总线与被测单元通信,其他两模块完成对被测单元的SPI和RS422等接口的通讯测试,所有通讯板卡均为标准PCI通讯卡。

2.5脉冲和位指令测试单元

同步信号测试包括时序关系和脉冲宽度等信息的测量。ATS的主控单元通过ARINC429总线对被测单元发出指令,被测单元产生时序可控和脉冲宽度可控的各脉冲信号并输出到ATS,脉冲和位指令测试单元通过计数器计算各信号时序和脉宽;通过标准IO口完成离散量信号的采集和输出工作。脉冲和位指令测量结果通过PCI总线传输到主控计算机。

2.6程控电源

雷达信号处理机需要对输入中频信号进行谱分析,为防止电源带来的寄生干扰引起处理指标下降,电源选用线性电源,提供高分辨率、高精确度的纯净直流电。程控电源由主控计算机通过RS232接口控制,实时控制其向被检测单元提供工作电源,包括+5 V和±15 V。

这里指出:测试系统硬件设计难点在于高精度、高稳定度中频信号设计。如果给DDS提供较低精度的时钟源将直接影响测试系统对雷达信号处理机的评价精度。因此选用高精度、高稳定度时钟源、利用直接频率合成技术设计实现低相噪DDS源是实现中频信号源的核心和难点,也是实现评价系统的关键所在。

3 ATS软件设计

3.1ATS软件组成及基本工作流程

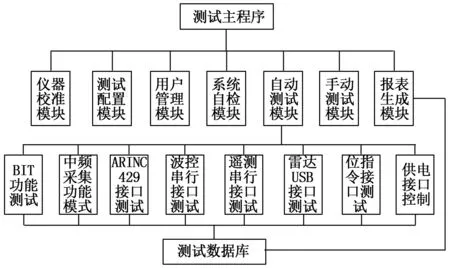

软件平台主要由平台内核、用户工具、测试程序集、故障诊断模块等组成。从通用性和后期维护角度考虑,本系统选择Windows XP作为主控计算机的操作系统。系统的开发工具选择Lab Windows/CVI。该软件采用通用的C语言编程,功能强大且灵活性强,具有丰富的测试用图形控件,内含虚拟仪器软件体系结构(VISA)库及智能虚拟仪器(IVI)库等。测试程序按功能划分包括:仪器校准模块、测试配置模块、系统自检模块、用户管理模块、自动测试模块、手动测试模块和报表生成模块等,测试软件结构如图3所示。

图3 ATS系统功能组成

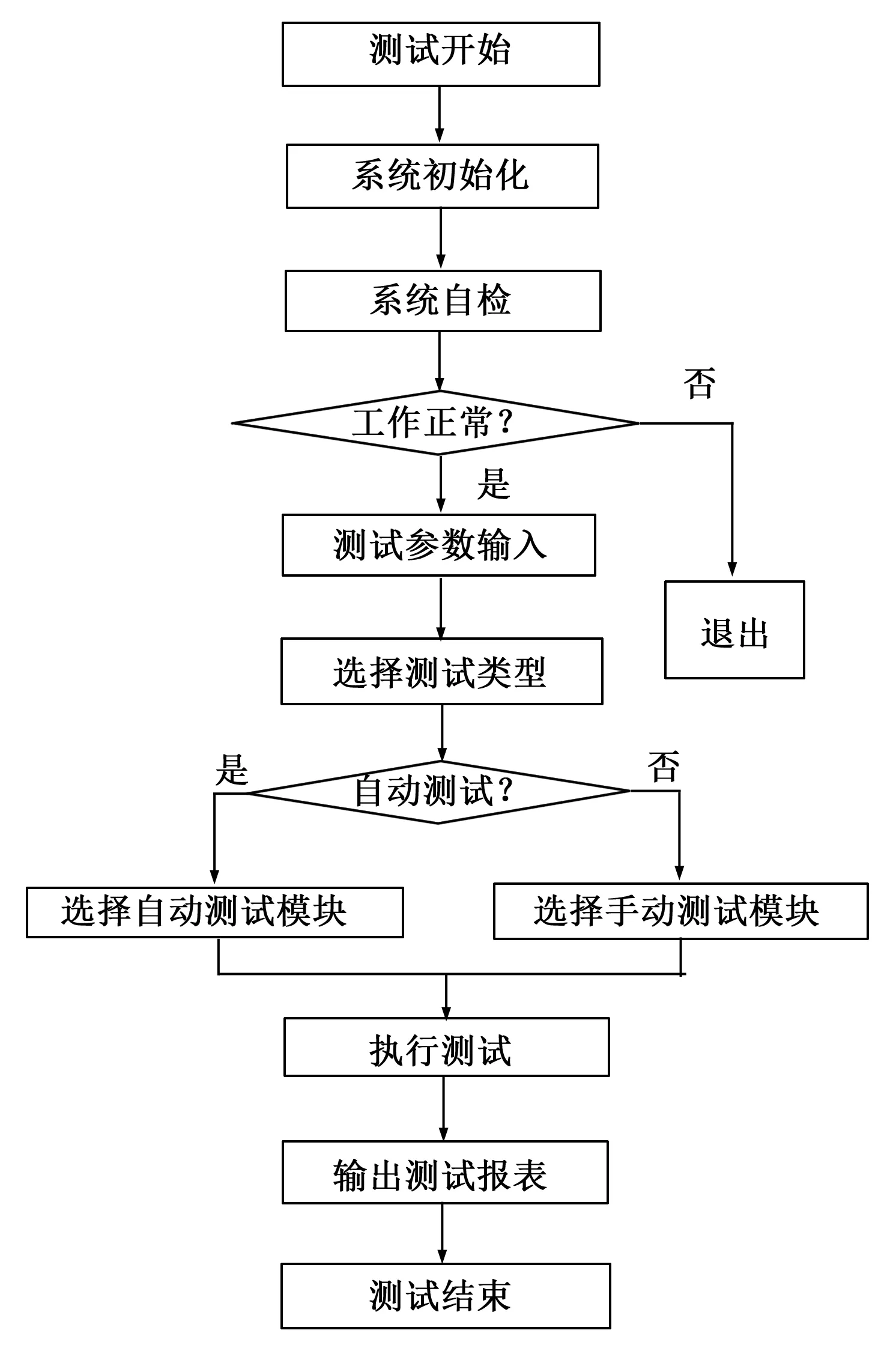

其中,自动测试模块又包含BIT功能测试、中频信号采集功能测试、ARINC429总线测试、波控SPI串行接口测试、遥测RS422串行接口测试、USB接口测试、位指令接口测试和供电接口控制等功能,测试软件工作的基本流程如图4所示。

3.2ATS与被测单元的数据通讯

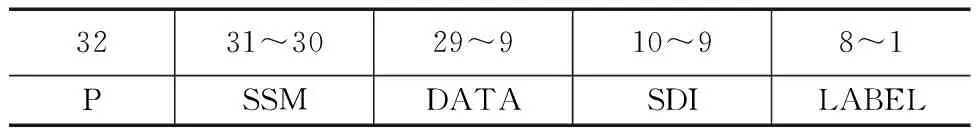

根据被测单元的接口情况,ATS和被测单元采用标准的ARINC429总线协议交互信息,数据由32位二进制数构成,包括8位标志位(LABEL)、21位数据位(DATA)、2位状态位(SSM)和1位奇偶校验位(P)。其中:P为奇偶校验位;SSM为符号/状态矩阵:00表示正常数据、01表示未准备好、10表示进行功能测试、11表示故障;DATA为传输数据;SDI为源/目标标识位;LABEL为传输参数标识,数据格式定义见表1。

表1 ARINC429字格式

ATS与被测单元的通信机制采取应答式通信机制,测试的基本流程如下:

图4 ATS软件工作流程

自动测试从ARINC429测试开始,当该项测试通过后继续进行其它测试项测试。ATS发送测试命令后,被测单元返回该测试项测试字,ATS在正确识别测试字后根据测试项进入测试状态或等待状态。测试状态时ATS测量被测单元输出信号并将测试结果送到主控计算机进行数据比较。等待状态时输出被测单元所需的测试信号并接收被测单元输出结果后进行数据比较。传输的数据段将所有测试项按要求编成测试通道号,第一包先发送测试通道号,后发测试数据。

3.3测试实例与结果分析

ATS测试程序集包括多个功能和性能测试测试函数。为验证系统测试效果,采用ATS同时对4台雷达信号处理机进行了功能和性能测试。ATS系统通过ARINC429总线接收被测雷达ADC采集的原始数据,调用ATS测试集Matlab函数进行性能分析后得到ADC采集的主要指标。

表2给出了4台雷达信号处理机同时测试时第1通道的主要性能指标,表3给出了同一台信号处理机4个通道ADC采集通道间性能指标。通过ATS测试分析,可以准确评价雷达硬件处理硬件平台的ADC采集性能,为信号处理机硬件平台的科学评价提供有效依据。

表2 单通道ADC测试主要指标

表3 通道间ADC测试主要指标

这里指出:软件设计关键在于设计合理的窗函数,对中频信号采集后将数据在合理带宽内处理,保证测试系统对硬件评价的科学性,该ATS自动测试平台能够对多台信号处理机多通道进行并行测量,对于理论有效位数为14位的ADC,其ENOB最高可达12.4,SFDR最高为87.4,表明软件设计参数选择合理。产品多通道间隔离度、幅相一致性指标测试结果亦满足设计需求,测试平台引入通道间的测试误差小,测试结果能够反映实际信号处理机的实际性能。

4 结束语

讨论了雷达信号处理机自动测试系统的研制问题,利用多项通用测试技术,采用标准化、开放式的系统结构和设计思想,自动测试系统具有了良好的通用性和可扩展性。该测试系统性能可靠、操作简便、自动化程度高、测试速度快、测试结果准确,并能够同时对多台产品并行测试和数据分析。在系统资源允许的情况下,只需更换测试模块及电缆,即可测试其它类型雷达信号处理机,采用的技术和方法也可推广应用到其它机弹载电子设备测试。

[1]丁鹭飞,耿富录.雷达原理[M].西安:西安电子科技大学出版社,2001.

[2] 李行善.自动测试系统集成技术[M].北京:电子工业出版社,2004.

[3] 摆卫兵,洪光,张东煜.某型地空导弹红外位标器自动测试仪设计[J].计算机测量与控制,2012,20(10):2666-2668.

[4] 马艳.某型雷达自动测试设备的设计[J].计算机测量与控制,2012,20(12):3260-3262.

[5] 陈杰,宋东,翟兴彦,等.某型机载雷达综合测试系统设计与应用[J].测控技术,2009,28(6):92-95.

Design of Automatic Test System for Parallel Radar Single Processor

Zhang Xiaoxi,Wu Yihu,Liu Yongqiang

(Xi’an Aeronautics Computing Technique search Institute,AVIC,Xi’an710065,China)

In order to test and evaluate the features and performance of a kind of radar single processor, this article provides a multi-parallel automatic test system design .It is on the basis of PCI bus combined with Lab Windows/CVI, Database and Direct Digital Synthesis technology. It has achieved a radar signal processor which can provide radar echo simulation, high stability ADC acquisition clock and multi-channel type pulse input. Furthermore it is focused on the completion of the multi-type radar signal processor bus test and analysis of key performance. Also it can provide quantitative test results and analysis combined with typical products. Finally,it has completed the verification of the effectiveness of the test system.

radar; automatic test; multi-parallel; real-time

2015-07-13;

2015-09-06。

张晓曦(1983-),男,内蒙古通辽人,工程师,主要从事导航、制导与控制,高速实时信号处理方向的研究。

1671-4598(2016)01-0126-02

10.16526/j.cnki.11-4762/tp.2016.01.035

TP3

A