基于FPGA的多通道超声波测距系统设计

2016-09-07吴思聪

刘 君, 伍 璨, 吴思聪

(天津理工大学 电子信息工程学院,天津 300384)

基于FPGA的多通道超声波测距系统设计

刘君, 伍璨, 吴思聪

(天津理工大学 电子信息工程学院,天津300384)

超声波测距是一种非接触式连续测量方法,具有电路简单、测量精度高等优点;传统的测距系统多采用单片机实现,无法满足现代测距实时性、立体化、多向性的要求;因此设计了一种基于FPGA的多通道超声波测距系统,所有通道同时进行检测与处理,系统具有较高的扩展性;硬件部分采用US_100超声波传感器实现了超声信号的发射与接收,采用京微雅格C192芯片对回波信号进行检测和处理,实现了从2厘米到4米的距离的精确测量,测量结果送入LCD12864进行显示;软件设计采用Verilog HDL语言在Primace编辑环境下进行开发,在Modelsim软件下进行仿真,并通过HR3开发板验证了全部设计功能;测试结果表明:该测距系统运行稳定可靠,测量精度高。

现场可编程门阵列;多通道;回波信号处理;超声波

0 引言

超声波具有稳定性强、易于制造、价格低廉、无辐射等优点,在多个领域有着广泛应用[1]。通常谐振频率高于20 kHz的声波称为超声波,频率越高,反射能力越强,而绕射能力越弱[1-2]。利用超声波的这种特性,常常用渡越时间检测法进行距离的测量[3-4]。传统设计方法多基于单片机设计,具有电路简单,成本低等优点,但无法满足现代测距立体化、多向性和实时性的要求[5-6]。本文设计了一种基于FPGA的多路超声波测距系统,采用渡越时间的测距原理,实现了四路超声测距通道并行检测、同时显示,相对于传统的测量方法提高了测距的速度与准确度,且系统具有较高的扩展性。

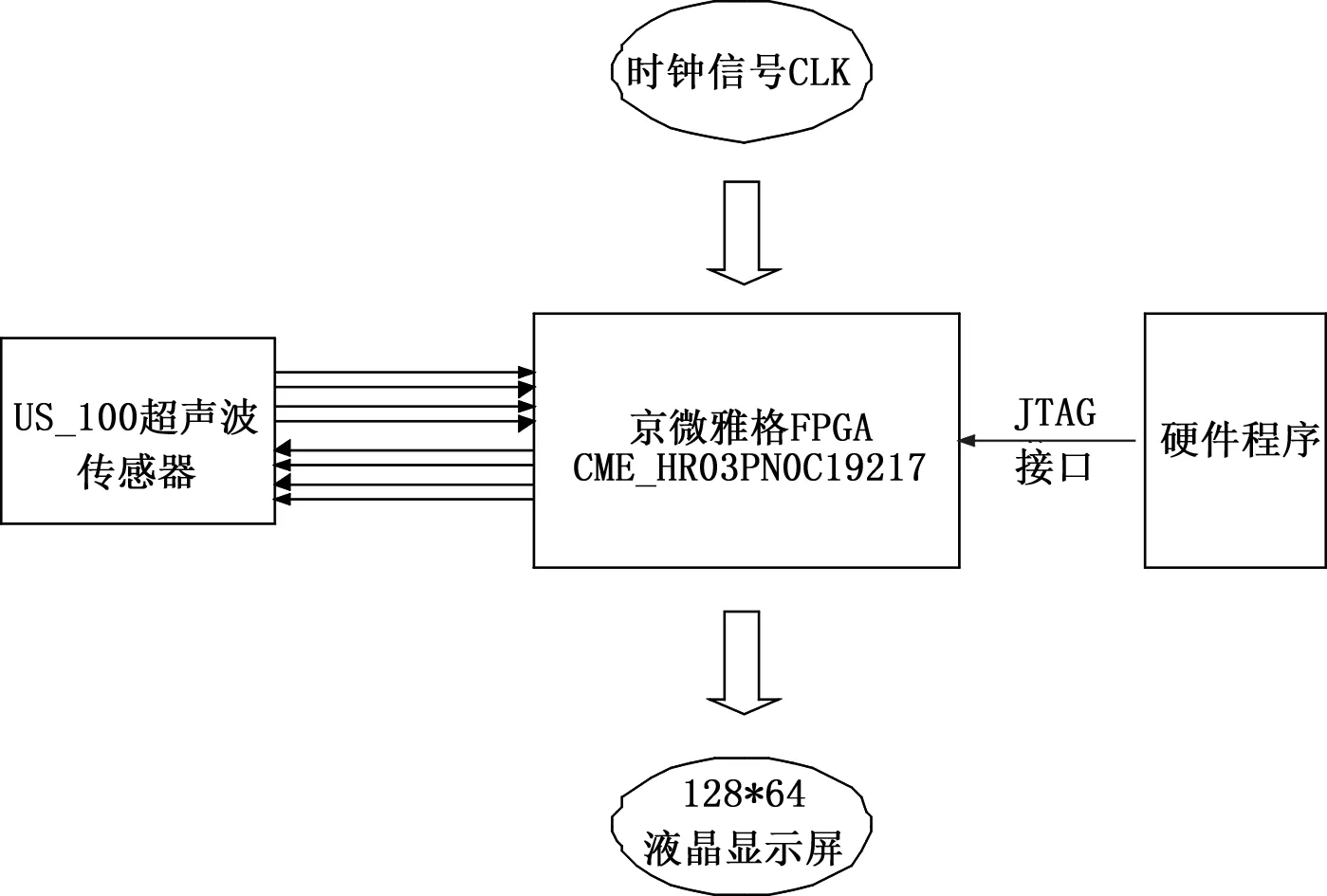

1 系统硬件设计

传统的多通道超声测距系统多采用控制器顺序触发超声探头并检测其回波信号,因此系统延时较大,无法真正实现多通道的同时检测,因此本文设计了一种基于FPGA的多通道超声波测距系统,利用FPGA的并行处理的特点,实现多通道并行检测和处理,并将处理的结果送入LCD液晶显示器进行显示,系统框图如图1所示。

图1 系统框图

1.1开发板CME_HR3及开发环境Primace

FPGA(Field Programmable Gate Array现场可编程门阵列)是在PAL,GAL,EPLD等可编辑器件基础上发展的产物[7]。本次设计选用的CME_R系列HR03PN0C192I7芯片是一种高性价比的可编程逻辑器件,主要面向低功耗的应用领域,拥有高性能、低成本的优势,其软件开发环境是由国内自主研发的Primace开发套件。Primace开发套件具有完整的EDA工具流程,自带丰富的IP核资源,能有效地进行快速研发设计,缩短IC产品研发周期,可以快速高效地进行FPGA或者CAP的应用设计。

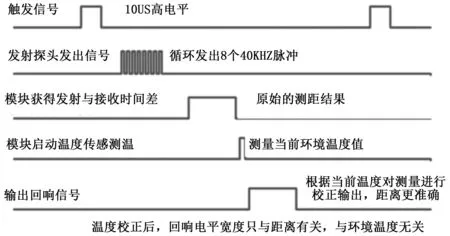

1.2US_100超声波测距传感器

US_100超声波测距传感器是一种非接触式传感器,可以实现2厘米到4.5米距离测量。将该模块的工作电压设定在3 V,即可以满足低功耗的要求,也可实现与FPGA电平的匹配。同时,由于内部自带温度传感器,可结合温度对测距结果进行校正,因此输出信号不需再进行温度校准,减小后续的工作。该模块可工作在串口触发模式或者电平触发模式,本次设计采用电平触发模式进行测距,图2为电平触发方式下US_100的时序图。由时序图可知,只要FPGA产生一个大于10 μs的触发信号,超声波传感器就可以发出 8个40 kHz 的超声波脉冲,并对超声回波信号进行温度修正,修正后的回波信号送入FPGA进行后续处理。

图2 US_100超声波测距模块工作时序图

1.3LCD128*64液晶显示屏

传统的LED数码管无法实现同时显示各个通道的测量结果,因此本文选用了较为常用的LCD液晶显示屏进行测量结果的显示。QC12864B点阵液晶显示屏是一种内部自带中文字库的点阵型液晶显示模块[8],其横向可以显示128个点、纵向可以显示64个点,由此得名128*64液晶点阵显示,能够满足四路测量结果的同时显示。

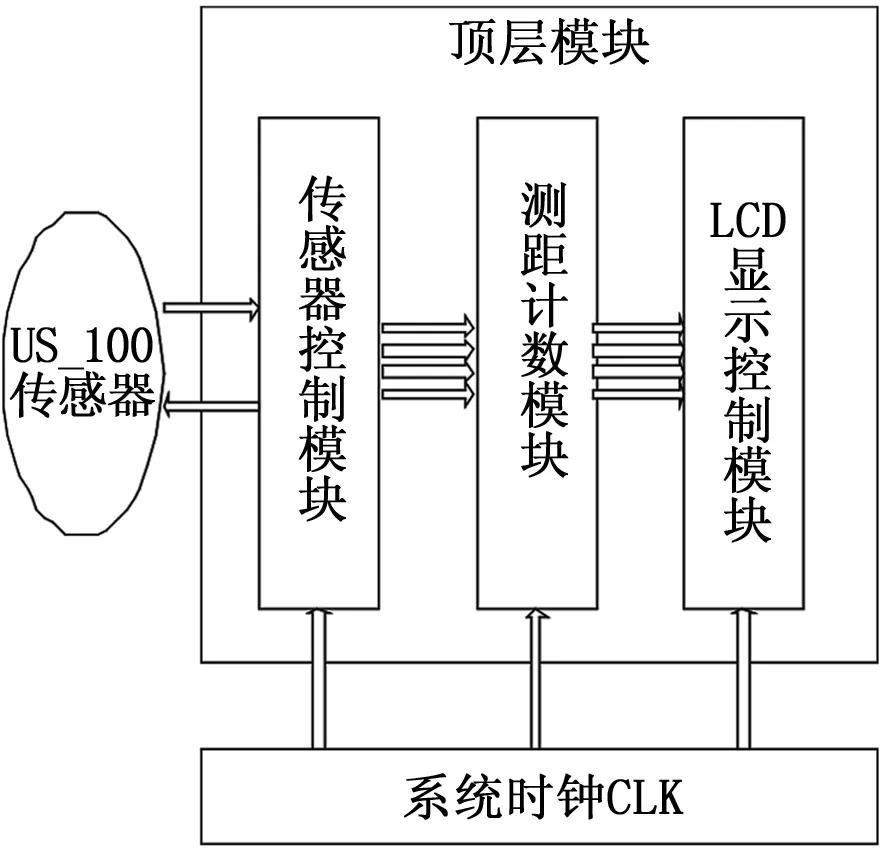

2 系统软件模块设计

本设计采用Verilog HDL语言Primace开发环境下进行软件设计。整个系统可分为传感器控制模块、测距计数模块、显示模块和顶层模块,软件设计框图如图3所示。

图3 软件设计框图

2.1传感器控制部分

为了使超声测距模块正常工作,该模通过FPGA要产生一个大于10 μs的触发信号(Trig),并且能够检测传感器的回波信号(Echo)。该模块采用状态机进行设计,如图4所示,状态机由5个状态组成,在st0状态完成对控制器的初始化;st1状态负责产生触发信号;在st2状态一旦检测到echo信号为高电平,则立刻转入到st3状态;在st3状态下,当检测到Echo信号为高电平时,启动计数器并完成对回波信号的测量,一旦检测到Echo信号变为低电平,锁存存测量的结果,并产生一个完成信号;st4准备下一次触发。黄河系列HR03开发板上提供的晶振时钟为20 MHz(周期为50 ns),而US_100要求的触发信号维持时间大于10 μs,故对时钟计数250次达到定时要求:

50 ns*250=12.5 μs;

(1)

图4 控制器状态转移图

2.2测距计数模块

测距计数模块主要功能是将超声波传感器的回波信号转换为化测量的距离,传统的测量方法都是通过测量超声回波信号的时间,再用声速乘以时间得到两倍的测量距离。但在FPGA系统里,由于采用了硬件描述语言进行设计,按照传统的设计方法将占用大量的FPGA资源,不利于系统的开发。因此在本次设计中采用一种预先计算的方法进行数据测量,既保证了测量的精度又节省了FPGA的资源。超声回波信号Echo高电平持续的时间是通过系统时钟进行测量的,根据US_100工作原理,从US_100传回的Echo信号已经转化为340 m/s标准音速的时长,若系统频率为20 MHz时,则1 mm的距离需计个数为可由式(2)确定(其中声速v为340 m/s,T为50 ns)。则N等于117.64,N取整数

(2)

117或者118。

则当N=118时,对应的测距长度为:

340 m/s*50 ns*118/2=1.003 mm;

(3)

当N=117时,对应测距长度为:

340 m/s*50 ns*117/2=0.995 mm;

(4)

通过上述计算可以发现,当采用118作为计数器的终值时,会产生0.003 mm的数据偏差;当采用117作为计数器的终值时,会产生-0.005 mm的数据偏差。所以选择118时系统误差更小,更符合设计要求。当毫米位(data1)测量完成后,后续的厘米位(data2)、分米位(data3)、米位(data4)的计数可遵循十进制计数的法则,依次完成对超声回波信号的测量与转换。对测距计数模块在Modelsim下进行功能仿真。图5为单通道的测距计数模块仿真结果图,如图所示,可以确认计数的过程是符合逻辑的,在Echo信号为高电平时,计数器开始工作并进行计数,data1计数到9后data2准确的产生进位,当计数完毕后在控制器产生一个Echo_done信号完成计数,并对计数结果进行锁存。

图5 计数模块仿真图

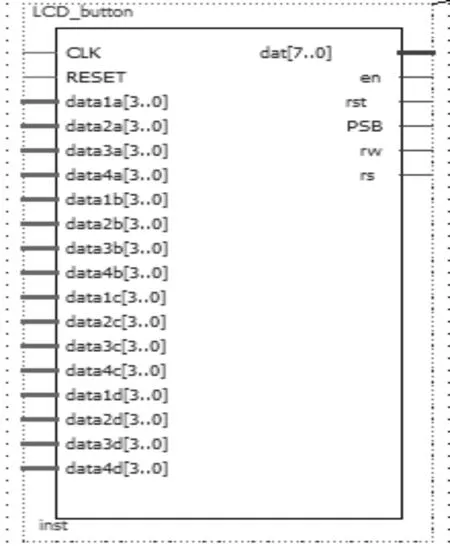

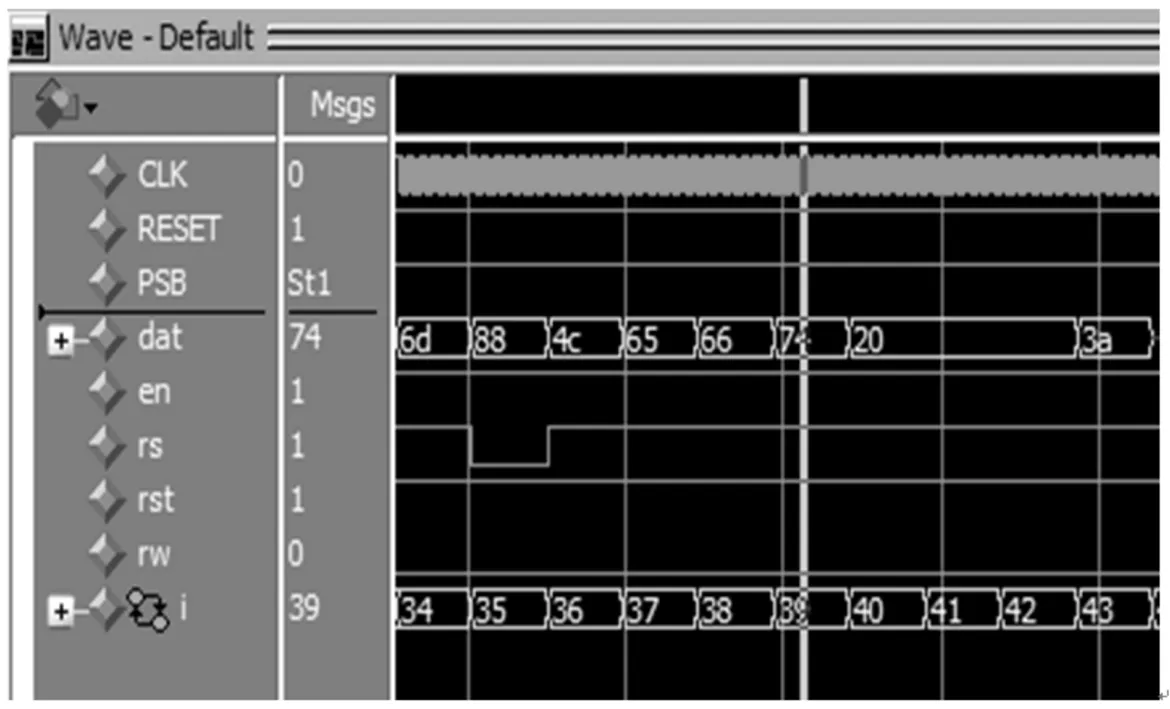

2.3128*64LCD液晶显示控制模块

该模块采用状态机设计方法,参照12864的工作状态进行设计,首先进行液晶显示屏的初始化,然后在显示屏上显示出各个通道的测量结果,整个显示过程循环进行。选用的128*64LCD液晶显示屏的指令执行时间为72 μs,即两条指令的输入间隔应大于72 μs,即此状态机的时钟频率基准应小于13.8 KHz,因此选用12.5 KHz的时钟作为基准,控制状态机状态转换,从而驱动LCD显示屏工作。送入的LCD_control模块的数据是BCD码,通过一个加法器加上30 H,实现数据到ASCII码的转换。图6为液晶显示模块例化图(调用了来自Quartus的例化图),data1a~data4b依次为A、B、C、D四路传感器测量所得毫米、厘米、分米、米位。dat[7..0]、en、rst、rw、PSB、rs为输出信号,与LCD显示屏的管脚相连,实现对LCD的操作。图7为控制模块的仿真图,可以看到在rs=0时输出的是LCD的行定位指令,之后连续的输出要显示的字符与测量的结果。

图6液晶显示模块例化图

图7 控制模块仿真图

2.4顶层模块设计

本次设计使用的Priamce开发套件内无法生成各自模块的例化模型,因此将设计好的文件保存在一个工程目录下,通过Verilog语言中的端口名关联法完成模块间的互联[7-9]。以一路传感器控制模块关联为例,说明其中使用的端口名关联法:

UR_control_FSM M1(.CLK(CLK), .trig(trig1),.echo(echo1),.echo_done(echo_done1),

.RESET(RESET),.d1(d1a),.d2(d2a),.d3(d3a),

.d4(d4a));

UR_control_FSM 是调用的已经例化的传感器控制模块;M1是调用模块的命名;.CLK为调用模块的输入信号端口名;括号内CLK是wire型外部连线或输出输入口线;其他端口类同。此外,如需多次调用已有例化模块UR_control_FSM,则只要在模块命名处采用不同模块名称即可。

3 系统调试、下载与验证

为了验证设计能否达到我们的设计要求,需要将程序下载到芯片内部,并进行实际测量。常用的下载配置模式包含主动配置AS(active serial configuration方式、被动配置PS(passive serial configuration)方式和JTAG方式,此次选用JTAG配置模式[10-11]。把输入、输出端口分配到指定的引脚后,通过下载线将程序下载到CME_HR3芯片上,并自动完成固化过程。

实验证明多通道超声波测距系统的4个US_100探头可同时对不同的方向进行距离测量,测量结果能够在LCD显示屏上实时的显示。为了进一步测试测距系统的测量精度,调整各个通道的障碍物与传感器的距离,观察并记录测量结果,测试结果如表1所示。从测试结果中可以得出结论:此次搭建的测距系统平台测距结果误差保持在±0.004 m内,测距结果可靠。

表1 测距测试结果

单位:m

4 结束语

本文设计了一种基于FPGA的多通道超声波测距系统,采用京微雅格的黄河C192作为主控芯片实现了多路超声信号同时检测与处理,器件占用的逻辑单元占总数的22%;调用的寄存器占总数的11%;参与分配的I/O口占总数的18%;PLB缓存寄存器调用率为57%。本设计可用于车载智能终端的超声测距部分,由于FPGA具备丰富的开发资源,可在此系统继上续增加测距通道的数量,也能够搭载其他传感器实现对时间、温湿度的测量,也可实现对酒精传感器、胎压的检测确保驾驶员的安全行驶,具有较高的扩展性和更为广阔的应用前景。

[1]卜英勇,王纪婵,赵海鸣,等. 基于单片机的高精度超声波测距系统[J]. 仪表技术与传感器, 2007(3): 66-68.

[2] 张攀峰,王玉萍,张健,等. 带有温度补偿的超声波测距仪的设计[J]. 计算机测量与控制,2012,20(6): 1717-1719.

[3] 高韵沣,何少佳,邓子信,等. 高精度嵌入式超声波测距系统的研究[J].计算机测量与控制,2015,23(1):25-26.[4] 夏继强,郑昆,郑健峰,等. 基于STM32的收发一体式超声波测距系统[J]. 仪表技术与传感器, 2014(8): 43-45.

[5] 顾国荣,鲍骏成,李海乐. 基于单片机的超声波测距系统设计[J]. 沿海企业与科技,2012(2): 42-45.

[6] 王巧花,邬昌军,姚建松. 基于单片机的超声波测距系统设计[J]. 煤矿机械,2014,35(6): 234-236.

[7] 陈大新,胡学同,周杏鹏. 利用FPGA改进超声波测距模块设计[J]. 传感器与微系统,2005,24(2): 57-59.

[8] 顾菘. 一种通用的TFT-LCD显示控制器的设计与实现[J]. 电子设计工程, 2012,20(15): 173-175.

[9] 黄继业,潘松. EDA技术实用教程[M]. 北京:科学出版社,2002.

[10] 丛伟林. 16Mbit FPGA配置存储器设计研究[D]. 成都:电子科技大学,2012.

[11] 唐文娟,颜永红,杨世明,等. 16通道剂量率在线检测系统的软硬件设计[J]. 核电子学与探测技术, 2011,31(3): 355-358.

Design of Multi-channel Ultrasonic Ranging System Based on FPGA

Liu Jun,Wu Can,Wu Sicong

(School of Electronics and Information Engineering,Tianjin University of Technology, Tianjin300384,China)

Ultrasonic ranging is a non-contact and continuous measurement which is simple in circuitry and high in accuracy. The single-channel ranging system can't meet the requirements such as real-time, three-dimensional and diversity. This paper designs a multi-channel ultrasonic ranging system based on FPGA(Field Programmable Gate Array) which is produced by Capital Microelectronics and tests and processes the echo signal come from US_100.The system can realize distance measurement from 2 centimeter to 4.5 meters. And the results can be displayed on LCD (Liquid crystal display). All software modules are designed by using Verilog HDL in Primace editing environment, and verified on the Modelsim and HR3 FPGA platform. The test results show that this system is stable and highly accurate.

field programmable gate array; multi-channel; echo signal processing; ultrasonic wave

2015-08-06;

2015-09-07。

天津理工大学育苗项目(LGYM201243);天津理工大学教学改革研究赞助项目(YB12-09)。

刘君(1980-),男,天津人,博士在读,讲师,主要从事信号检测与处理方向的研究。

1671-4598(2016)01-0078-03

10.16526/j.cnki.11-4762/tp.2016.01.021

TP3

A