一款高增益、低功耗、宽带宽全差分运放设计

2016-09-07周吉,龚敏,高博

周 吉,龚 敏,高 博

(四川省微电子技术重点实验室,四川大学物理学院,成都 610064)

一款高增益、低功耗、宽带宽全差分运放设计

周吉,龚敏,高博

(四川省微电子技术重点实验室,四川大学物理学院,成都 610064)

基于SMIC 0.18 μm工艺模型设计了一种低电压1.8 V下的高增益、低功耗、宽输出摆幅、宽带宽的运算放大器电路。采用增益自举技术的折叠共源共栅结构极大地提高了增益,并采用辅助运放电流缩减技术有效地降低了功耗,且具有开关电容共模反馈(SC-CMFB)电路。在Cadence spectre平台上仿真得到运放具有极高的开环直流增益(111.2 dB)和1.8 V的宽输出摆幅,单位增益带宽576 MHz,相位裕度为58.4°,功耗仅为0.792 mW,在1 pF的负载时仿真得到0.1%精度的建立时间为4.597 ns,0.01%精度的建立时间为4.911 ns。

低功耗;运算放大器;高增益;宽带宽;折叠共源共栅

1 引言

运算放大器(简称运放)是许多模拟系统和混合信号系统中一个完整且关键的部分,随着无线通讯技术和CMOS集成电路制造工艺技术的迅猛发展,电源电压越来越低,功耗要求越来越小,但数模混合信号系统对分辨率和速度的要求却越来越高,因此高性能的运放设计成为了必要[1]。根据模拟电路设计的“八边形法则[1]”,运放的关键性能参数如增益、速度、功耗、输出摆幅等参数相互制约,这对高性能放大器的设计提出了许多难题。因此,设计同时具有高增益、宽带宽、宽输出摆幅并且低功耗的放大器便成为了本设计的难点[1,2,3]。高速、高精度的应用需要运放具有很高的增益和带宽,而这必然会增加运放的功耗,Mersi A.等发表的文献中采用两级带补偿结构的运放功耗仅为0.86 mW[4],而这种结构对进一步提高运放带宽等有一定的局限性,本文采用了一种不同的低功耗运放结构,希望解决这个问题。

2 运放结构分析和选择

目前常见的几种放大器结构主要有两级放大器、套筒共源共栅放大器以及折叠共源共栅放大器等。

两级运放在这些结构运放中具有最大的输出摆幅,但是它引入了更多的极点和零点,频率特性比较差,需要额外的频率补偿,并且带宽较小,速度较慢,此外,两级结构还消耗了更多的功耗。

套筒共源共栅结构的优点是具有极好的频率特性,它有很高的单位增益带宽,所以速度很快。但是,套筒结构的输出摆幅较小,特别是在电源电压越来越低的趋势下,它的应用受到了一定的限制。

折叠共源共栅结构由套筒结构衍生而来,具有和套筒结构相近的良好的频率特性,因此同样具有很大的带宽和速度。由于有4路电流,功耗比套筒结构要大,但是折叠结构有较大的输入共模范围和输出摆幅。此外,运放的全差分结构相比于单端结构,有更好的共模噪声抑制和更大的输出摆幅,并且能够消除偶次谐波失真,因此本设计选用全差分折叠共源共栅结构。

3 运放的电路设计

3.1运放结构设计

随着CMOS工艺特征尺寸的不断减小,晶体管的本征增益在深亚微米尺寸下变得很小[1],因此,要获得很高的增益,就需要采用增益提高技术。一种“增益自举技术[3,5,6]”可以极大地提高运放的增益,它的原理是通过增大输出电阻来提高运放的增益。从图1的增益自举原理图可以得到,其输出电阻增大了约Av倍:

其中,gm2是M2的跨导,Av是辅助运放的直流增益,Ro1、Ro2是M1、M2的输出电阻。

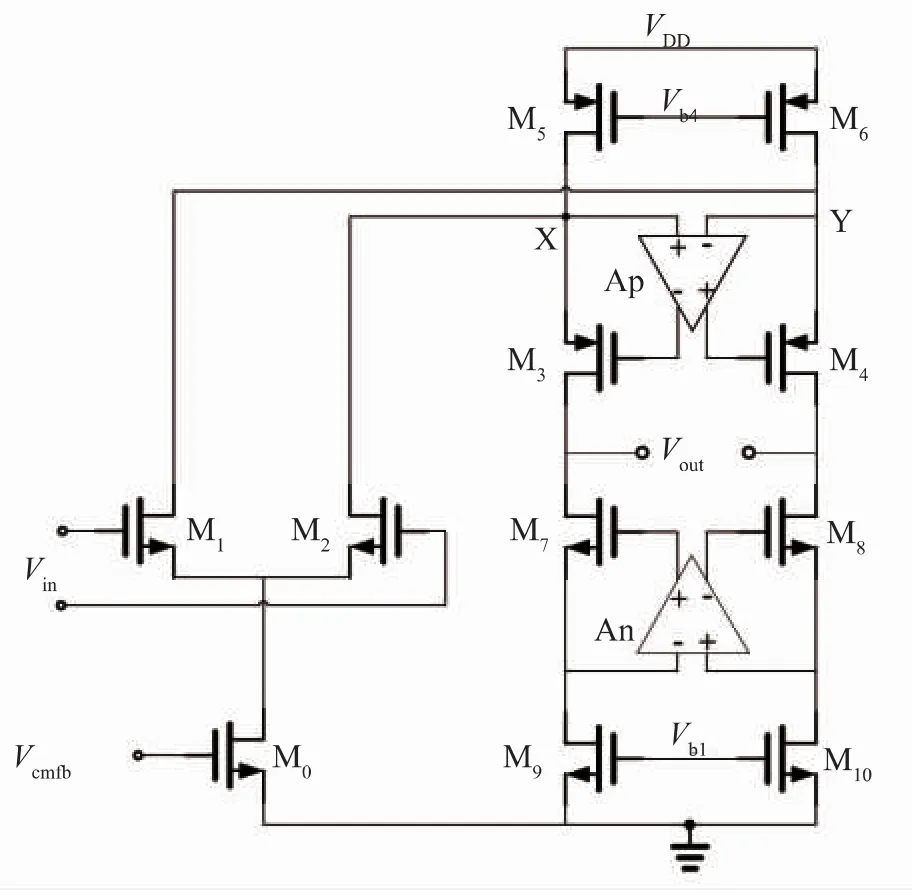

如图2是采用了增益自举技术的折叠共源共栅运放的电路结构图,它由主运放Am和辅助运放Ap、An组成。

普通折叠共源共栅结构运放增益为:

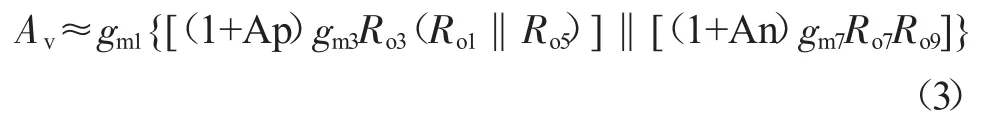

采用增益自举技术的折叠共源共栅运放的增益为:

相比于普通折叠结构,引入增益自举技术使得增益增大了约辅助运放倍。

图1 增益自举技术原理图

图2采用增益自举技术的折叠共源共栅运放结构图

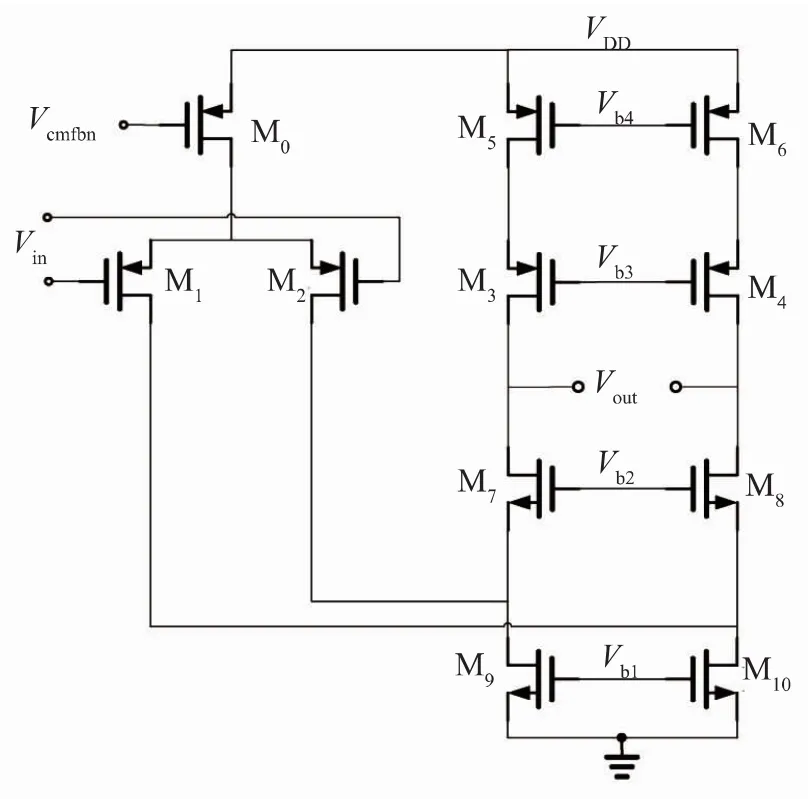

图3和图4分别是Ap、An辅助运放的电路结构示意图。其中,An、Ap辅助运放采用和主运放相似的结构,这样不仅减小了电路复杂程度和所需偏置电压个数,同时增加了电路匹配性,图中偏置电压Vb1~Vb4由镜像电流源产生,Vcmfb是共模反馈控制电压。

3.2高增益、宽带宽设计

根据图2的增益自举折叠共源共栅电路图和其相应的增益公式(3),分析运放的高增益、宽带宽设计:

(1)由于NMOS管的电子迁移率比PMOS管的空穴迁移率大,所以选用NMOS管输入,以得到更大的gm1,提高运放增益。此外,运放单位增益带宽GBW=gm1/CLe,其中CLe为总的等效负载电容,所以增大gm1还增大了单位增益带宽。

图3 p型辅助运放Ap

图4 n型辅助运放An

(2)图2中折叠点X处的寄生电容Cx,它包括了CGD5、CDB5、CGS3、CSB3、CGD1、CDB1的寄生电容,以及Ap辅助运放的输入电容,因此Cx较大,运放的次极点在X处。选取较小的MOS管尺寸和增大过驱动电压的方法减小Cx,从而得到高的次极点频率,增大带宽。但这是以牺牲增益或输出摆幅为代价的,因此需要在这之间进行折衷。

(3)因为饱和区MOS输出电阻Ro∝L/ID[1],L是MOS管栅长,ID是MOS管电流。由图2可知,M5,6管流过两倍于M3,4管的电流,所以设计L5,6是L3,4的2倍,以增大Ro5,6来提高运放的增益;

(4)饱和区MOS管本征增益gmRo∝(WL/ID)1/2,增大W、L或减小偏置电流ID可以提高运放增益。一般情况下速度和噪声的要求确定了ID,因此MOS管的尺寸是唯一变量,并且MOS管的W/L需要保持定值,以保证过驱动电压不变。由于M1~M4在信号通路上,希望它们的电容保持最小,而M7~M10对信号的影响小得多,因此增大M7~M10的W和L来提高运放的增益,同时几乎不影响带宽。

3.3低功耗设计和共模反馈

从图2可以看到,Ap、An辅助运放的负载分别是主运放的共源共栅管M3,4和M7,8的寄生电容,它与主运放的负载相比很小,因此选取辅助运放和主运放电流之比为1∶10,并通过仿真优化这个比值。采用这种辅助运放电流缩减技术,有效地降低了运放功耗,同时还减小了寄生电容,增大了运放带宽。

在高增益全差分运放中,输出共模电平对器件的特性和失配相当敏感,而且不能通过差动反馈来达到稳定,这可能使输出MOS管进入线性区而不能正常工作,因此必须增加共模反馈电路来稳定输出共模电压。

共模反馈电路主要有连续时间型和开关电容型(SC-CMFB)[6,7,8],连续时间型会影响运放的输出摆幅、增益等,同时会增加额外的功耗;开关电容型则不会,但是需要时钟控制信号,考虑到运放的低功耗设计,这里选择开关电容型共模反馈电路。

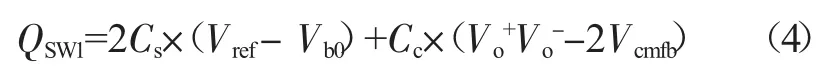

图5是开关电容共模反馈电路,SW1和SW2是两相不交叠时钟控制的开关,Vo+、Vo-是运放的差分输出电压,Vref是期望的输出共模电压,Vb0是初始偏置电压,Vcmfb是共模反馈控制电压,Cs和Cc是电容。

图5 开关共模反馈电路结构图

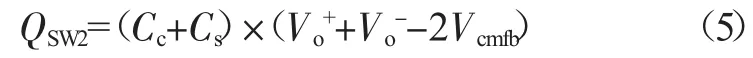

它的原理是:在SW1相,电容Cs和Cc上的总电荷为:

在SW2相,电容Cs和Cc上的总电荷为:

由电荷守恒得:

因此,通过负反馈的作用,使输出共模电压等于Vref,达到了共模反馈的目的。

4 电路仿真结果及版图

在Cadence spectre平台上进行AC仿真得到结果如图6所示,低频直流增益为111.2 dB,单位增益带宽576 MHz,相位裕度58.4°。

建立时间仿真:在运放的差分输入端加入幅度为200 mV的阶跃输入信号,在负载电容为1 pF时,得到的建立时间仿真结果如图7所示,0.1%精度的建立时间为4.597 ns,0.01%精度的建立时间为4.911 ns,均小于5 ns,能够满足较高速度的应用要求。

图6 运放ac仿真结果图

图7 建立时间仿真结果图

表1 运放性能参数对比

表1给出了本设计与参考文献中在运放性能参数上的一些对比:和文献[8]相比功耗相近,但本设计具有更高的直流增益和更大的带宽;与文献[4]在相同工艺尺寸下,得到了更小的功耗以及更大的增益和带宽,并且本设计采用的单级增益自举电路结构与其两级结构相比更加简单,无需额外的补偿电路。此外,一般认为,60°的相位裕度是最合适的数值[1],相位裕度过大会减慢运放的速度特性,相位裕度过小会产生振荡现象和稳定性问题。本设计的运放相位裕度为58.4°,因此可以提供快速稳定的建立。

图8 运放版图

运放的版图如图8所示,版图面积约为90 μm×90 μm。图中分别标注了辅助运放Ap、An及主运放Am的位置。

5 总结

本文基于SMIC 0.18 μm CMOS工艺,设计了一款高增益(111.2 dB)、宽带宽(576 MHz)、宽输出摆幅(1.8 V)、低功耗(0.792 mW)且具有良好稳定性的运放电路。采用折叠共源共栅结构和增益自举技术,并通过MOS管尺寸、电流和过驱动电压设计,极大地提高了运放增益、带宽和摆幅;采用辅运放电流缩减技术和开关电容型共模反馈有效降低了运放功耗,仿真结果表明运放具有良好的性能。

[1]毕查·拉扎维,陈贵灿,程军,张睿智,等译.模拟CMOS集成电路设计[M].西安:西安交通大学出版社,2009.

[2]Paul R Gray,Paul J Hurst.Analysis and Design of Analog Integrated Circuits[M].4th Edition,New York:John Wiley &Sons,Inc,2001.

[3]MOHAMMAD M A.A new modeling and optimization of gain-boostedcascodeamplifierforhigh-speedand low-voltage applications[J].IEEE TCSII,2006,53(3):169-173.

[4]Mersi A,Pirbazari M M,Hadidi K,et al.High gain two-stage amplifier with positive capacitive feed back compensation[J].IEEE IET Institution of Engineering and Technology,2015,9(3):181-190.

[5]朱江南,杨兵,姜岩峰.一种高增益全差分运算放大器的分析与设计[J].微电子学,2015,45(6):714-717.

[6]赵郁炜,朱红卫.一种10位200 MHz流水线模数转换器的设计[J].微电子学,2014,44(5):587-596.

[7]Ojas Choksi,Richard Carley L.Analysis of switchedcapacitorCommon-ModeFeedbackCircuit[J].IEEE Transactions on Circuits and Systems-II:Analog and Digital Signal Processing,2003,50(12):906-916.

[8]Rui Zou.Design of a Fully Differential Gain Boosted Operational Amplifier for High performance ADC[A]. Watada J,Yabuuchi Y.2013 Sixth International Conference on Business Intelligence and Financial Engineering(BIFE)[C].New York:IEEE,2013.539-541.

Design of a Fully Differential High Gain and Low-power and High Bandwidth Amplifier

ZHOU Ji,GONG Min,GAO Bo

(Key Laboratory of Micro-electronics Technology of Sichuan Province,College of Physical Science and Technology of Sichuan University,Chengdu 610064,China)

A Low-voltage 1.8 V with High Gain and High unity bandwidth and low-power integrated operational amplifier was designed based on SMIC 0.18 μm CMOS process.Adopted gain-boosting technique in folded-cascode architecture greatly raised the gain.Used assisted-amplifier current scaling-down technique effectively reduced the power consumption,also had SC-CMFB circuit.Simulation results on Cadence spectre show that the DC open-loop gain is 111.2 dB and 1.8 V output swing with a unity gain frequency of 576 MHz and phase Margin of 58.4°,0.792 mW power dissipation only. Besides 4.597 ns setting time of a 0.1%accuracy and 4.911 ns setting time of a 0.01%accuracy under the 1 pF load.

low-power;operational amplifier;high gain;high bandwidth;folded-cascode

TN402

A

1681-1070(2016)05-0026-05

2016-3-7

周吉(1990—),男,四川内江人,四川大学物理学院微电子学系硕士研究生,研究方向为超大规模集成电路设计。