面向应用型本科教育的FPGA课程教学探讨

2016-09-06陈新武陈咏恩黄文霞孙秋菊

王 鹏, 陈新武, 陈咏恩, 黄文霞, 孙秋菊

(1. 信阳师范学院 物理电子工程学院, 河南 信阳 464000;2. 同济大学 通信软件及专有集成电路设计中心, 上海 200092)

面向应用型本科教育的FPGA课程教学探讨

王鹏1,2, 陈新武1, 陈咏恩2, 黄文霞1, 孙秋菊1

(1. 信阳师范学院 物理电子工程学院, 河南 信阳464000;2. 同济大学 通信软件及专有集成电路设计中心, 上海200092)

结合实际的工程和教学经验,对FPGA课程的教学改革进行了有益的探索,并对教学关键点进行了整理,重点介绍如何理解FPGA和HDL语言的硬件电路特质,以及阻塞和非阻塞赋值的本质区别。在FPGA课程教学中综合采用多种措施,并特别加强对学生代码风格的训练,使学生在接触课程时产生浓厚兴趣,逐步建立硬件电路思维。

FPGA课程; 硬件描述语言; 并发执行; 代码规范

FPGA是现代电子技术领域中发展最为迅猛的领域之一,自1985年Xilinx公司推出首款FPGA产品XC2064以来,它就以其固有的高度灵活性、硬件级并行执行等优势迅速占领了诸多电子设计领域[1]。2015年6月,半导体巨头Intel公司宣布以167亿美元的价格收购FPGA主要生产商Altera公司,这次并购也使更多人认识到了FPGA的巨大价值。与FPGA产业的飞速发展相对应,目前国内几乎所有高校也都针对电子相关专业本科生开设了FPGA设计基础、可编程逻辑器件等专业课程[2]。然而该课程的教学普遍存在着明显的重理论、轻实践问题,大量课时浪费在讲述FPGA内部结构原理和复杂的HDL语法上,留给学生思考、设计的时间很少,绝大部分本科生在完成课程学习后仍然不能理解FPGA的硬件电路实质,仍然采用类似C语言的思维进行HDL代码编写[3]。兼之一些授课教师也缺乏工程经验,知识更新不及时,更进一步制约了授课效果,培养出来的学生基本不具备实际FPGA开发能力,这与现实中FPGA应用人才的缺乏形成了鲜明的对比。

1 深入理解FPGA的硬件理念

FPGA设计的主要手段是HDL语言,由于其开发过程与传统的单片机、CPU比较相似,加之HDL语言在语法上也与不少软件语言类似,使得许多学生以学习软件编程语言的方式学习HDL,而许多授课教师也未能意识到这一点,或者即使意识到了,但强调程度仍不够,这样就导致了学生虽然掌握了HDL语法,但由于没有硬件电路思维,不能深刻领会HDL语言的最终实现目标是硬件电路,设计出来的代码常常只能用作仿真而无法综合,或者即使可以综合,也存在着占用资源大、代码运行效率低等问题[4]。

曾经有不少人对FPGA究竟属于软件还是硬件感到困惑,其中甚至不乏具有丰富经验的电子工程师。事实上,只需简单了解FPGA的构造即可发现,其内部包含大量的LUT、寄存器、可编程布局布线、IO以及存储资源等。其中LUT可实现任意组合逻辑功能,寄存器则用于实现时序功能。明白了这一点,就会清楚地意识到FPGA是一种典型的硬件级可编程数字集成电路。

2 HDL语言的选择

目前,常用的HDL语言主要包括Verilog和VHDL,二者都有各自的优缺点,也都能较好地完成电子设计工作。事实上,从可综合代码角度来看,二者并没有本质区别,相同的逻辑功能,使用Verilog和VHDL实现并无太大差别。许多EDA软件如Synplify、ISE、ActiveHDL等都支持Verilog和VHDL混合编程,甚至还有专业软件可以自动在Verilog和VHDL之间完成转换[5]。

但是,Verilog和VHDL还是有各自的特点,一般地,EDA业界公认Verilog语法灵活、代码紧凑,VHDL则结构严密、代码比较冗长。而从使用现状来看,Verilog更为流行。据统计,在美国高层次数字系统设计领域中,应用 Verilog 和 VHDL 的比率是 90%和 10%。日韩、台湾和美国类似,欧洲 VHDL 发展稍好,但也不如Verilog。在中国,绝大多数集成电路设计公司也都采用 Verilog ,但VHDL在一些军工研究所及高校也有一定的市场[6]。

另一方面,Verilog 的成熟资源也比 VHDL 丰富,许多半导体厂商在提供器件行为仿真模型时仅提供Verilog模型。 而且Verilog在较短的时间内即可掌握,而 VHDL 不够直观,一般认为至少要半年以上的专业培训才能掌握。虽然传统意义上认为VHDL在更大规模的系统设计中有一定优势,但随着Verilog-2001、Verilog-2005等新一代Verilog标准的出现,Verilog的系统级、算法级描述能力得到了很大改善,VHDL的相对优势已经越来越少。

此外,随着EDA技术的不断发展,SystemVerilog、SystemC作为新型HDL语言的代表也已经出现,这些语言加入了许多面向对象语言特性[7-8],并在许多EDA公司得到了广泛应用,但其各自的强项分别是设计验证和算法仿真建模,在传统的RTL级代码领域, Verilog的生命力依然很旺盛,而且Verilog也在不断更新自身以迎合时代发展,在可以预见的将来,Verilog仍会在EDA设计领域中占据十分重要的地位。

因此在HDL语言的选择上不必盲目求新讲述SystemVerilog/SystemC,而在Verilog和VHDL这两种经典HDL之间,前者的发展势头更好,授课采用Verilog无疑是更主流、更迎合业界现状的选择。

3 FPGA课程教学思路

在专业转型的大背景下,FPGA课程作为典型的应用技术专业课,其授课目的应当是让学生理解与掌握这种与传统CPU截然不同的设计实现方式,并顺利成长为合格的FPGA开发工程师,但由于在FPGA课程学习中还会经常涉及到其他课程的专业知识,如讲述FIR数字滤波、DDC数字下变频等处理模块时,就要求学生必须具有数字信号处理及通信原理基础。因此,各转型高校应当在修订培养方案时注意专业课程的安排次序及教学进度,保证教师在讲解一些FPGA实用模块时学生具备相应的专业知识基础。

3.1开课吸引学生兴趣

目前许多FPGA教材的概述部分充斥着大量的专业词汇,这对于此前未接触过FPGA的学生,很容易感到困惑且难以接受。因此,授课教师在开始课堂讲述时,切忌一上来就引入过多的新概念,可转而从可编程逻辑器件的发展历史、市场规模乃至开发人员的就业前景等着手,首先要吸引学生对该课程的兴趣,让学生真正认识到FPGA开发是一门很有用的技术。例如,可介绍可编程逻辑器件领导厂家Xilinx公司的快速发展历程,从1984年成立时仅有3名员工,只花了10年的时间,公司收入就达到了10亿美元,现在Xilinx已发展成了全球最大的FPGA生产商,年销售额数十亿美元[9],同样地,拥有3 000名员工的Altera公司被Intel公司以167亿美元高价收购也是FPGA巨大价值的绝好例子。再加上丰富的图片、视频向学生介绍FPGA的典型产品及应用,如火星探测计划、航空武器等。通过这些手段,学生很快就能对FPGA器件产生浓厚的兴趣,使学生主动学习相关知识,相应的授课效果也得到了改善。

3.2强调FPGA与CPU的本质区别

由于FPGA与单片机、ARM等CPU在开发过程上的相似性,许多学生难以理解FPGA与CPU的差异,这导致学生经常使用学习CPU的思路来学习FPGA,带来许多不必要的麻烦。为了加深印象,可以从日常生活中提取许多生动实例,向学生强调FPGA的硬件电路本质。类似商品房和自建房的区别,从事CPU开发就像是购买开发商提供的商品房,其户型、面积等类似于CPU的主频、缓存等关键参数,购房者(开发人员)只能在开发房提供好的户型图中选择一种比较适合自己的房子,并可对房子进行装修(编程开发),但选择户型和装修的自由度都有限,而从事FPGA开发则像是完全自行建房。FPGA为设计人员提供了大量的建筑材料,如LUT、RAM、PLL(类似于砖块、钢筋、水泥等),开发人员可以自行将这些底层建筑原料设计成适合的建筑物(FPGA工程),建筑的户型、面积等均可以由设计人员自行决定。FPGA开发远比CPU开发灵活,也更为底层,因此,FPGA设计工程质量的好坏就完全依赖于开发者自身;而CPU开发人员的主要精力则是在软件代码设计上,只需考虑代码运行结果的正确与否及效率的高低,具体的代码执行过程则由CPU自行完成,开发人员一般不必关心。通过这个生活实例的对比讲解,学生可以比较透彻地理解FPGA开发与CPU开发的重大区别,并有助于消除其对FPGA的误解。

3.3淡化原理图设计输入

原理图设计方式是传统数字电路的一种常见设计手段,该设计方式也被FPGA所继承,Altera和Xilinx两大FPGA厂商在其设计套件Quartus II和ISE中均提供可选的原理图设计方式[10]。不仅如此,国内几乎所有的EDA教材也都将基于原理图方式的设计手段作为FPGA设计入门教程,并在学生掌握原理图设计手段后再介绍基于HDL的设计方式,这一方面是由于原理图方式具有可视化效果好、上手快等优点,另一方面则是因为学生在之前的数字电路课程中已经习惯于阅读和设计各种由逻辑门电路、触发器等元器件构建的电路原理图。然而事实上,这种设计方式在实际的FPGA应用中早已被淘汰,其可移植性差、不适合复杂系统等先天缺陷,注定它只适合于以分离元器件为主的特定时期[11]。

自从成熟的HDL出现以后,真正有效的FPGA设计手段就一直是基于HDL可综合代码的设计方式。因此,讲述FPGA设计时不推荐学生采用原理图的设计方式,而是一开始就要求掌握基于HDL的设计方式。虽然这种方式不如原理图直观,但HDL自身就是面向硬件设计的,学生只有掌握了这种方式才能真正发挥FPGA的强大功能,而且现代FPGA内部集成LUT和寄存器越来越丰富,一些高端FPGA芯片的寄存器及LUT资源达数百万量级。采用HDL可以很好地完成此类复杂的数字系统设计,其设计效果远远优于原理图设计方式。

不推荐原理图设计方式的另一个有力证据则来源于FPGA生产商, 目前最大的FPGA厂商Xilinx公司自2012年开始推出用于取代ISE的全新FPGA开发套件Vivado(最新版本为2015.1),该开发工具已经明确不再支持基于原理图的开发手段,因此,FPGA授课教师应该及时吸纳最新的设计理念,直接讲述基于HDL的设计方式。

3.4阻塞与非阻塞赋值

阻塞与非阻塞赋值是Verilog语言中的著名难点,也是其特有的语法现象,甚至许多具有多年经验的FPGA工程师也未能完全理清该问题。阻塞赋值的理念相对容易理解,因为它与软件语言中的串行执行概念是大致相同的,即后一条语句执行时,前一条语句已经执行完毕了,初学者学习这种赋值一般比较自然,但学习非阻塞赋值时则有较大难度。

许多教科书上只是简单地介绍非阻塞具有并发执行特性,且语句的先后书写顺序与执行结果无关,但对非阻塞赋值的详细执行过程并没有仔细介绍,初学者更是对并发执行的特性难以接受。事实上,借用信号与系统中的δ冲激函数概念,可以有效地帮助学生理解非阻塞赋值的实质。

下面以典型的阻塞与非阻塞赋值对比语句为例,从执行机理上解释二者的区别(该实例被多个教材采用,但解释方式各有不同):

代码1(阻塞赋值):

module tst(q1,q2, clk_osc) ;

input clk_osc;

output [7:0] q1,q2;

reg [7:0] q1,q2;

always @(posedge clk_osc)

begin

q1=q1+8′d1;

q2=q1;

end

endmodule

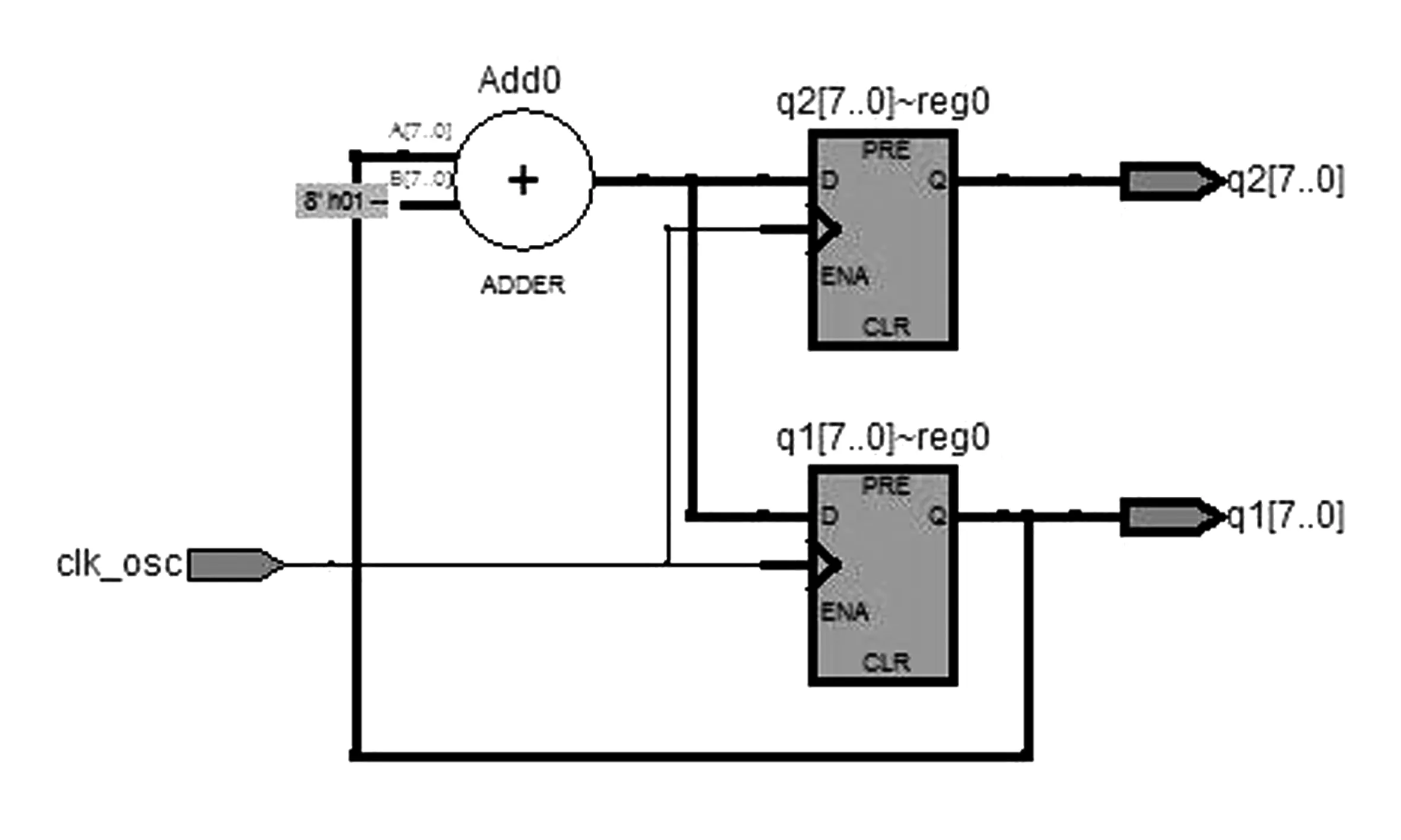

上述代码采用了阻塞赋值,在执行到q2=q1时,q1=q1+8′d1已经执行完毕,即意味着在任何时刻,q2的输出实际上与q1完全相同,如果将上述代码进行综合,其电路如图1所示,其中的q2输出部分虽然也有一个寄存器,但它与下方q1输出寄存器是完全等价的,如果把综合器的代码优化功能打开,q2输出寄存器将会被彻底优化掉,此时q2共享q1输出数值。

图1 阻塞赋值综合后RTL级电路图

而如果是非阻塞赋值,其代码为:

代码2(非阻塞赋值,仅列出always块语句,其他同代码1):

always @(posedge clk_osc)

begin

q1<=q1+8′d1;

q2<=q1;

end

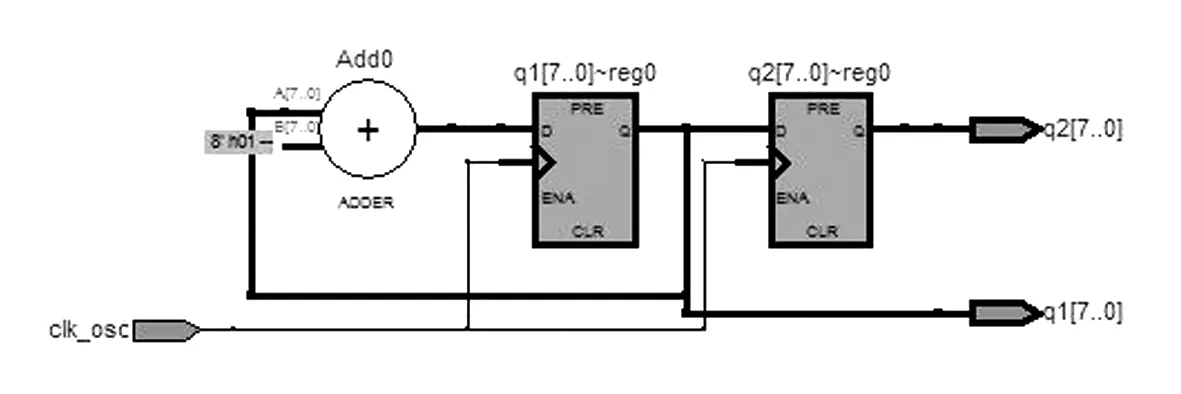

非阻塞赋值的重要特点是表达式运算与目的变量值更新分开进行,对于上述非阻塞赋值过程块,其执行过程可以分析如下:首先执行q1<=q1+8′d1语句,即进行q1累加操作,得到新的q1值,但并不立即更新,而是需要一个极小的δ时间才能完成,同样地,q2<=q1语句执行也是一样,得到新的q2值后也不立即更新,而且该时刻参与运算的q1依然是老值,而不是q1<=q1+8′d1语句得到的新值,只有在δ时间过去后,全部非阻塞语句的目的变量值才能被更新。因此,整个过程块的执行效果就是q1完成累加计数,而q2则对q1进行一级寄存处理,相应的RTL综合视图如图2所示。

图2 非阻塞赋值综合后RTL级电路图

需要说明的是,以上分析来源于Verilog语言的语法特性,EDA仿真器在仿真非阻塞赋值代码时,由于其工作平台是基于串行执行理念的CPU,所以即使是非阻塞赋值,依然需要通过串行执行的步骤实现,只是由于它具有表达式计算与赋值更新分开完成这一独特语法现象,运行效果与实际硬件电路的并行运行特性等同。教师在讲授非阻塞赋值时,务必要让学生理解,之所以有非阻塞赋值这种特殊操作,是为了模拟硬件电路的并发运行特点,但它本身仍是通过串行执行完成的。

大量FPGA教科书为了进一步加深学生对两种赋值的理解,常常加入大量阻塞非阻塞混合使用的实例。事实上,授课教师只需让学生清楚这两种赋值的本质区别及应用范围即可,在实际EDA工程设计中,出于代码可读性和可维护性的考虑,阻塞和非阻塞赋值是严格禁止在同一过程块语句中出现的,而许多教材花了大量篇幅讲授的这些实例并没有实用价值,反而让学生过于追求复杂语法,得不偿失。

3.5重视良好的代码风格

由于并发执行语句的存在,HDL语言在可读性上明显逊色于各类软件高级编程语言,而且代码量普遍很大,即使是一些中小规模HDL设计,其代码也通常都在数千行甚至上万行,再加上后期的功能升级等要求,均对HDL代码的可读性、可维护性提出了更高要求。正因为如此,良好的代码风格在HDL中显得尤为关键[12]。

目前,国内的主流EDA教材对HDL代码风格重视程度明显不够,多数教材甚至直接缺失该部分内容。这导致许多学生虽然学习了FPGA课程,但在工作后从事FPGA开发时代码书写混乱,几乎没有可维护性,并不能真正完成具有工程实用性的FPGA设计。事实上,几乎所有的业界知名半导体公司及研究所均有相应的HDL代码风格及规范要求,如华为公司、中兴公司、中国航天科技集团等。Xilinx和Altera公司作为FPGA主要生产商,也在其产品手册中给出了许多代码设计规范要求,这些要求虽然细节不尽相同,但仍有许多共通之处,如同步化设计、合理的注释、变量命名原则、状态机书写范式等。这些代码风格上的要求恰恰是目前FPGA课堂教学最为欠缺的。许多公司及研究所在招聘应届生从事FPGA开发时,常常还需要花大力气对其进行代码风格和规范书写的专门培训。因此,在FPGA课堂教学时就要开始重视代码风格问题,将一些业界的通用性要求向学生讲述清楚,在课堂实验时要求学生自觉做到这些并逐步培养自身代码书写规范能力,以提高工程化设计能力。这一点在当下应用型教育愈发重要的背景下,尤其具有重大的现实意义。

4 总结与结论

结合FPGA技术的发展现状,提出了面向应用型本科教育的FPGA课程改革及教学关键点,结合工程和教学经验,总结了一些具有较强参考价值的教学思路,包括深入理解FPGA的硬件电路属性、HDL语言的选择、FPGA与CPU的本质区别,以及Verilog的教学难点、代码规范的重要性等。只有让学生真正理解了这些课程关键点,才能理清学习思路,做到有的放矢,在学习中不走弯路,最终达到学以致用,成为优秀的FPGA应用型人才。

References)

[1] 杨海钢,孙嘉斌,王慰.FPGA器件设计技术发展综述[J].电子与信息学报,2010, 32(3):714-727.

[2] 覃洪英. FPGA实验教学方法改进探讨[J]. 实验室科学, 2012, 15(4):79:82.

[3] 朱磊,卫建华,邱春婷.FPGA课程实践环节教学改革[J].高等工程教育研究,2008, 30(12):134-136.

[4] 刘宁庄.实践教学方法在FPGA课程教学中的应用[J].高校实验室工作研究,2013 (1):22-24.

[5] 安健,吴悦,杨洪斌,等. Verilog到VHDL翻译器的设计与实现[J].计算机工程与设计,2005,26(10):2695-2697.

[6] 夏宇闻.Verilog数字系统设计教程 [M].3版.北京:北京航空航天大学出版社,2014.

[7] 姚爱红,孙盟哲,张智钧,等.基于断言的Compact PCI总线IP核功能验证[J].小型微型计算机系统,2014,35(3):676-680.

[8] 崔惠珊,崔海青,李淼.基于SystemVerilog的多通道ARINC429总线通讯板卡的设计[J].现代电子技术,2014,38(16):54-57.

[9] 胥京宇.Xilinx 20nm All Programmable Ultra Scale产品系列面世[J].世界电子元器件, 2014(1):34-36.

[10] 梁瑞宇,奚吉. HDL项目设计的创新实验设计[J].中国科教创新导刊,2013,34(10):28-30.

[11] 段帅君. 基于Verilog HDL语言的CAN总线控制器设计及测试[D]. 长春:吉林大学,2009.

[12] 邸志雄. HDL代码质量评估方法关键技术研究与电路性能优化[D].西安:西安电子科技大学,2013.

Exploration of FPGA course teaching for application-oriented undergraduate education

Wang Peng1,2, Chen Xinwu1, Chen Yongen2, Huang Wenxia1, Sun Qiuju1, Zhong Lijuan1

(1. College of Physics & Electronics, Xinyang Normal University, Xinyang 464000, China;2. Communication Software & ASIC Design Centre, Tongji University, Shanghai 200091, China)

Combining the long-term engineering and teaching experience, beneficial explorations on FPGA course reform were accomplished, and key points of FPGA course were listed clearly. The natures of FPGA and HDL’s hardware circuit were interpreted in detail to help students understand this knowledge point. Essential differences of blocking and non-blocking assignments of Verilog HDL were presented clearly, too. With methods depicted above, plus specialized training on HDL coding style, the students’ interests in FPGA course were enhanced clearly. Besides, the students can distinguish FPGA and CPU easily along with course studying. Hardware-circuit-oriented thinking was also established naturally.

FPGA course; hardware description language; concurrent-operation; coding norm

10.16791/j.cnki.sjg.2016.03.047

2015- 09- 17修改日期:2015- 11- 03

河南省教育厅教师教育课程改革研究项目(2013-JSJYZD-026);河南省高等学校重点科研项目(15A510011)

王鹏(1985—),男,河南周口,博士,高级工程师,主要研究方向为超大规模集成电路设计、数字通信.

E-mail:pengpwn1985@163.com

G642.4

A

1002-4956(2016)3- 0185- 04