基于FPGA的雷达信号高速实时采集和显示系统设计*

2016-08-18孙玉梅张彦飞王美春王选诚

孙玉梅,张彦飞,王美春,王选诚

(烟台南山学院东海校区电气与电子工程系,山东烟台265713)

基于FPGA的雷达信号高速实时采集和显示系统设计*

孙玉梅*,张彦飞,王美春,王选诚

(烟台南山学院东海校区电气与电子工程系,山东烟台265713)

雷达回波采集的目的是为雷达数据处理和目标检测、定位、跟踪做必要的准备。本系统采用带有RAID适配卡的工控机作雷达视频回波采集的主控设备,设计了基于FPGA的雷达信号高速采集卡。利用FPGA内部双口RAM的乒乓切换与缓冲区环行存储技术保证了连续采集。采用数据抽取、坐标查表映射等技术在微机显示器上以PPI(平面位置)方式进行实时显示。试验结果表明本系统能够对每秒50万点的雷达回波信号进行实时高速连续采集、存储和实时显示。

雷达;信号;数据采集;FPGA

现代雷达信号处理需要现场采集大量的雷达视频回波数据,以分析和研究目标回波信号的各种特性为目标的信息提取和处理提供依据[1]。传统基于计算机的大多数雷达信号采集系统通常采取的方法是:首先在计算机内开辟一大块内存缓冲区,然后将采集的数据通过计算机接口存入缓冲区,一旦缓冲区存满便停止采集,最后再进行数据存盘。这样很难做到长时间的连续采集、实时显示与实时存盘。其原因是由于计算机在显示与存储数据上花费的时间较多,难以保证在不丢失采集数据的情况下实时显示与实时存储采集数据。

本文设计并实现了一种雷达视频回波信号的高速采集、实时显示与实时存储系统。该系统采样频率能达到10 MHz,采样精度为14 bit,采集数据以DMA结合中断方式被写入计算机公用缓冲区[2],由于对公用缓冲区的读写采用环形指针,因此可以循环不断地将采集数据写入缓冲区,同时读出缓冲区中的数据进行实时显示[3-4]。为了保证实时显示与实时存储,计算机必须在雷达天线旋转一圈时间内完成一圈所有数据的显示与存储。采用约数据抽取、坐标查表映射和DirectDraw等技术[5]对采集的数据的实时显示,用RAID磁盘阵列(廉价冗余磁盘阵列)对采集的数据实时保存,有效提高了采集存储设备的实时存储能力。

1 系统组成与工作流程

1.1系统组成与工作原理

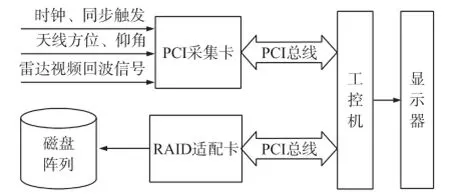

本系统以工控机为平台,雷达视频回波信号的采集主要由PCI采集卡来完成。PCI采集卡根据来自雷达系统的时钟、同步触发信号和天线方位、仰角信号来控制对雷达视频回波信号的采集,并将采集数据通过计算机PCI接口传输到计算机内存中,供计算机处理与显示[6]。最后计算机通过插在计算机PCI槽中的RAID适配卡来控制往磁盘阵列上实时存储采集数据。系统组成与工作原理框图如图1所示。

项目来源:国家自然科学基金项目(61273058)

收稿日期:2015-06-24修改日期:2015-08-05

图1 系统组成与工作原理框图

由于采用32 bit/33 MHz的PCI采集卡,其总线数据传输速率可达132 Mbyte/s,而系统采样频率为10 MHz,采样精度为14 bit,数据率为20 Mbyte/s,完全可以满足雷达视频回波数据的传输要求。

1.2系统工作流程

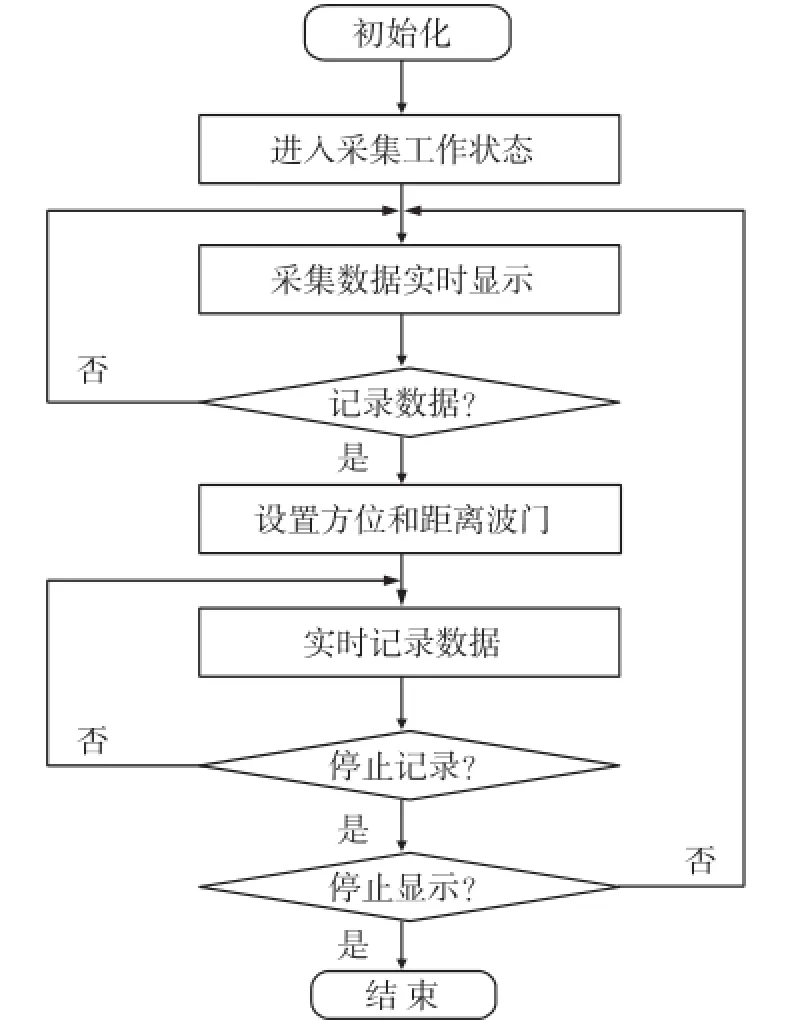

本系统要求能够在普通显示器上对采集的雷达视频回波信号进行长时间的实时显示。同时在显示过程中,可对任意区域设置采集方位和距离波门,将采集的数据实时存储在磁盘阵列上。系统的工作流程如图2所示。

在采集工作状态,采集卡将全方位、全距离上的雷达视频回波信号采集传输到计算机内存中;实时显示时,在普通显示器上以PPI(平面位置)显示方式进行实时全屏显示,同时可对局部区域用B显方式进行开窗放大显示;数据记录时,既可对重点目标区域设置方位和距离波门进行实时存储,也可对全程数据进行实时存储[7-8]。

图2 系统工作流程图

2 主要功能实现

2.1PCI采集卡的硬件设计

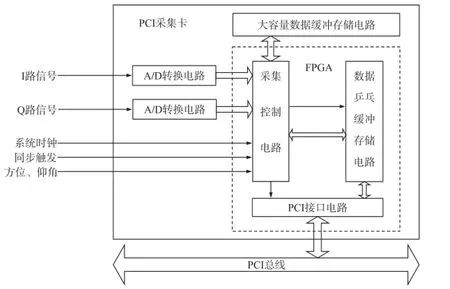

PCI采集卡主要完成对雷达视频回波信号的数据采集。它由双路高速高精度A/D转换电路、大容量数据缓冲存储电路、采集控制电路、数据乒乓缓冲存储电路、PCI接口电路组成。其中采集控制电路、数据乒乓缓冲存储电路、PCI接口电路在FPGA的内部实现。采集卡组成框图如图3所示。

图3 采集卡组成框图

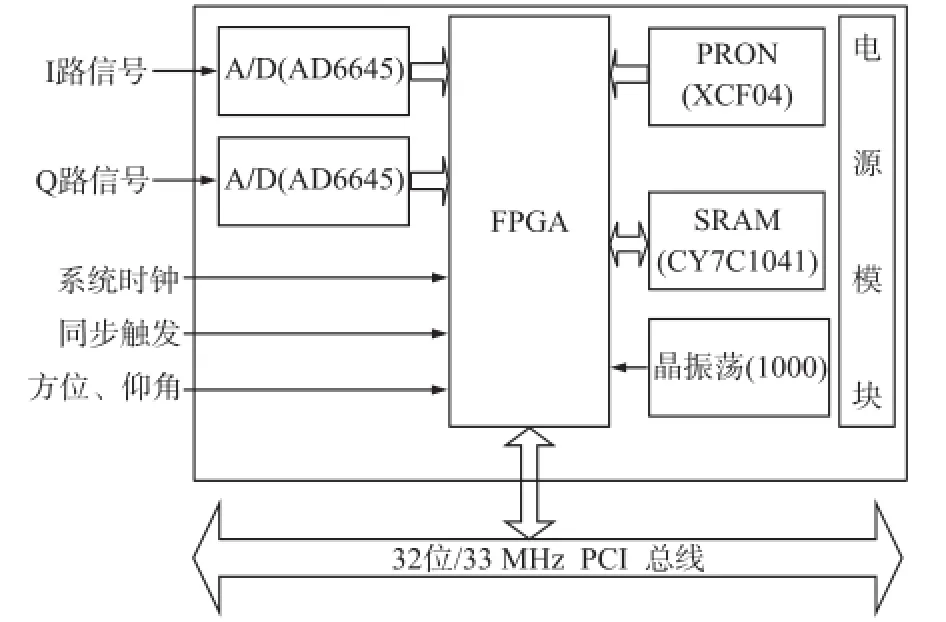

利用FPGA来实现32 bit/33 MHz的PCI接口逻辑,完成对雷达视频信号的采集时序控制与数据传输的控制。由于FPGA具有层次化的存储器系统,因此可以在FPGA内部配置高速双口RAM用来作为数据传输的乒乓缓冲存储器[9]。同时,为了节省FPGA的内部逻辑资源,在FPGA外围配置了适当的SRAM作为大容量数据缓冲存储器。PCI采集卡硬件电路结构框图如图4所示。

图4 采集卡硬件电路结构框图

图4中,FPGA芯片采用能够支持高速雷达信号处理的Xilinx公司的Virtex-7系列XC7VX1140T芯片[10],它是密度比较高的FPGA,其多达119万个逻辑单元实现了突破性容量,实现2.8 Tbit/s总串行带宽。与Virtex-6系列器件相比,其系统性能提高一倍,功耗降低一半,信号处理能力提升1.8倍,I/O带宽提升1.6倍,存储器带宽提升2倍。A/D转换采用ADI公司的14 bit 80MSPS的高速高精度模数转换芯片AD6645。SRAM采用Cypress Semiconductor公司的32 bit SRAM芯片CY7C1354。

2.2FPGA实现PCI接口逻辑

PCI总线协议必须实现PCI目标设备状态机、PCI主控设备状态机等逻辑。目标状态机完成必要的对配置寄存器以及目标设备I/O映射与内存映射端口读写。主控状态机负责交换过程的启动和数据的读写控制。为了实现PCI总线各控制信号间的时序关系,可以根据具体的交换过程来设计相应的状态机。下面以目标设备I/O写为例加以说明:当帧有效信号(FRAME#)为低电平有效时,标志着一次交换过程的开始,C/BE#[3:0]为“0011”表明此交换为I/O写,同时AD[31:0]上的数据为此次交换的I/O地址。如果该I/O地址与设备配置寄存器中I/O基地址寄存器的值相同,目标设备就要通过使DESEL#有效来声明这次交换。作为主设备在有效FRAME#、I/O地址和C/BE#后就在AD[31:0]上驱动要传输的数据,在C/BE#上驱动字节使能,同时使能目标准备好信号IRDY#,直到检测到目标设备有效的DRDY#信号后,此次交换中的主设备和目标设备就停止驱动各种信号。而目标设备在准备好接收数据后就可以使能DRDY#,此后目标设备检测到IRDY#时就可以根据具体的字节使能C/BE#[3:0]将AD[31:0]总线上的数据进行锁存,从而完成整个交换过程[11]。

本系统利用VHDL语言在FPGA中编程[11-12]实现了32 bit/33 MHz的PCI接口逻辑,实现的主要功能包括:配置空间读写、目标设备I/O映射读写、内存映射端口读写、主设备DMA控制。实际调试中,DMA连续传输速率可达到100 Mbyte/s。

2.3PCI卡驱动程序开发

本系统采用DriverWorks开发的运行于Windows 2000下的WDM(视窗驱动模块)驱动程序。DriverWorks可以向导为用户自动生成驱动程序框架,根据具体的功能,用户可在VC++6.0 SDK的工程下添加自己的代码,DriverWorks将编写WDM驱动程序所需的对内核模式及硬件的访问封装成类,其中KPciConfiguration类用于实现对PCI设备配置空间的访问,KIoRange类用于实现对I/O映射端口的访问,KMemoryRange类用于实现对内存映射端口的访问,KDmaAdapter、KDmaTransfer和 KCommon-DmaBuffer类用于实现DMA操作,Kinterrupt类用于实现中断处理操作。

由于数据采集系统的速率指标为20 Mbyte/s,同时CPU还要在有限的时间里完成数据的实时显示与实时存储,因此数据传输方式采用了DMA结合中断的方式。根据对数据采集量的要求和工控机CPU的实际处理能力,设计时开辟了16 M×32 bit的连续公用缓冲区,一次DMA传输8 K×32 bit的数据,每次DMA传输结束时,采集卡发出中断请求,计算机响应中断,并将公用缓冲区的写地址加上8 K作为下一次DMA传输的起始地址,从而保证了DMA传输的连续性。

2.4连续采集的实现

基于FPGA的雷达信号采集的难点是采集时序控制和数据的实时传输[12]。为了保证数据采集的连续性,设计中采用了FPGA内部双口RAM的乒乓切换技术与计算机公用缓冲区环行存储技术。

采集卡与计算机之间的数据交换以FPGA内部配置的高速双口RAM作为数据传输的缓冲器,采用两片双口RAM乒乓切换的方式进行数据传输。具体方法为:利用FPGA内部配置的两片8 k×32 bit的双口RAM,采集开始时,将采集数据往第1片双口RAM中写,当第1片双口RAM写满时,采集控制模块产生乒乓切换信号,数据自动存入第2片双口RAM中,同时以DMA方式将第1片双口RAM中的采集数据传送给计算机。如此轮换交替,这样DMA传输和接收A/D数据可以同时进行,而DMA的速率远大于A/D采集速率,从而可以有效避免数据丢失。

为了连续不断地接收采集数据,计算机缓冲区采用了环行存储结构。具体方法为:系统初始化时,驱动程序在计算机中申请了16 M×32 bit的公用缓冲区,并将其映射到用户地址空间。对公用缓冲区的读写采用环行指针,当写指针指到缓冲区底端,即缓冲区写满时,写指针又回到缓冲区起始端,将新的采集数据覆盖原来的旧数据,这样便可循环不断地将采集数据写入环行缓冲区。与此同时,应用程序也在循环不断地根据环行读指针将缓冲区中的数据读出进行实时显示。这样环行缓冲区的读写可以同时进行,只要显示的速度满足实时性要求,便可以保证整个采集过程的连续性。

2.5实时显示

雷达天线转速为10 rot/min,脉冲重复频率为700 μs,距离量程设定为50 km,则在采样率为10 MHz情况下,天线转动一圈(6 s)采集到的点数约为300万。这意味着要实现采集数据的实时PPI显示,则必须在6 s完成一屏所有点的数据计算和显示。为此,设计时采用了数据抽取、坐标查表映射和Direct Draw等技术。

由于计算机分辨率所要求的一屏内显示的像素点远小于天线转动一圈所采集的数据点,为减轻计算机负担,对雷达视频回波在周期和距离上进行了“数据抽取”。设计算机显示器的分辨率为1 024× 768,那么一屏内只需显示约80万个点。可见,采用数据抽取方法后数据量降为原来的27%。由于一般雷达回波信号采用的是极坐标体制,而光栅显示器采用的是直角坐标系体制,因此必须进行坐标转换[7]。传统坐标变换中正弦、余弦与乘、除法运算耗时过多,若将坐标转换运算改用坐标查表映射,则可显著提高运算速度。具体方法为:将光栅显示器屏幕点阵赋予距圆心距离值、角度值和颜色值等属性,并将这些属性依据极坐标的特性进行排序做成索引表,并在系统初始化时调入内存,系统工作时无需再作变换,大大节省了CPU的运算时间。

坐标转换机制建立后,鉴于PPI显示对实时画图速度的特殊要求,采用了Direct Draw技术,它可直接对显存操作,具备硬件位操作、硬件覆盖操作和页面切换操作的能力,它绕过了与Windows的图形设备相连的多个层次,直接与硬件的底层打交道,产生快速、平稳的图形。

2.6实时存储

目前高速数据存盘主要有两种方案:第1种方案是采用集成RAID功能控制器的主板;第2种方案是采用普通主板加RAID适配卡,控制数据到磁盘阵列的存储。第1种方案,从以前的使用情况来看,在使用2块SCSI硬盘组成RAID 0阵列和Adaptec公司的SCSI硬盘RAID适配卡情况下,磁盘阵列实测的读写速度达到40 Mbyte/s;第2种方案,在使用普通主板和RAID适配卡时,采用2块IDE硬盘组成RAID 0阵列情况下,磁盘阵列实测的读写速度达到35 Mbyte/s。可见两者性能差别不大,因此,从性能指标需求和设计成本角度考虑,本设计最终选用了普通主板、RAID适配卡和普通IDE硬盘组成磁盘阵列来完成实时存储。

3 运行结果分析

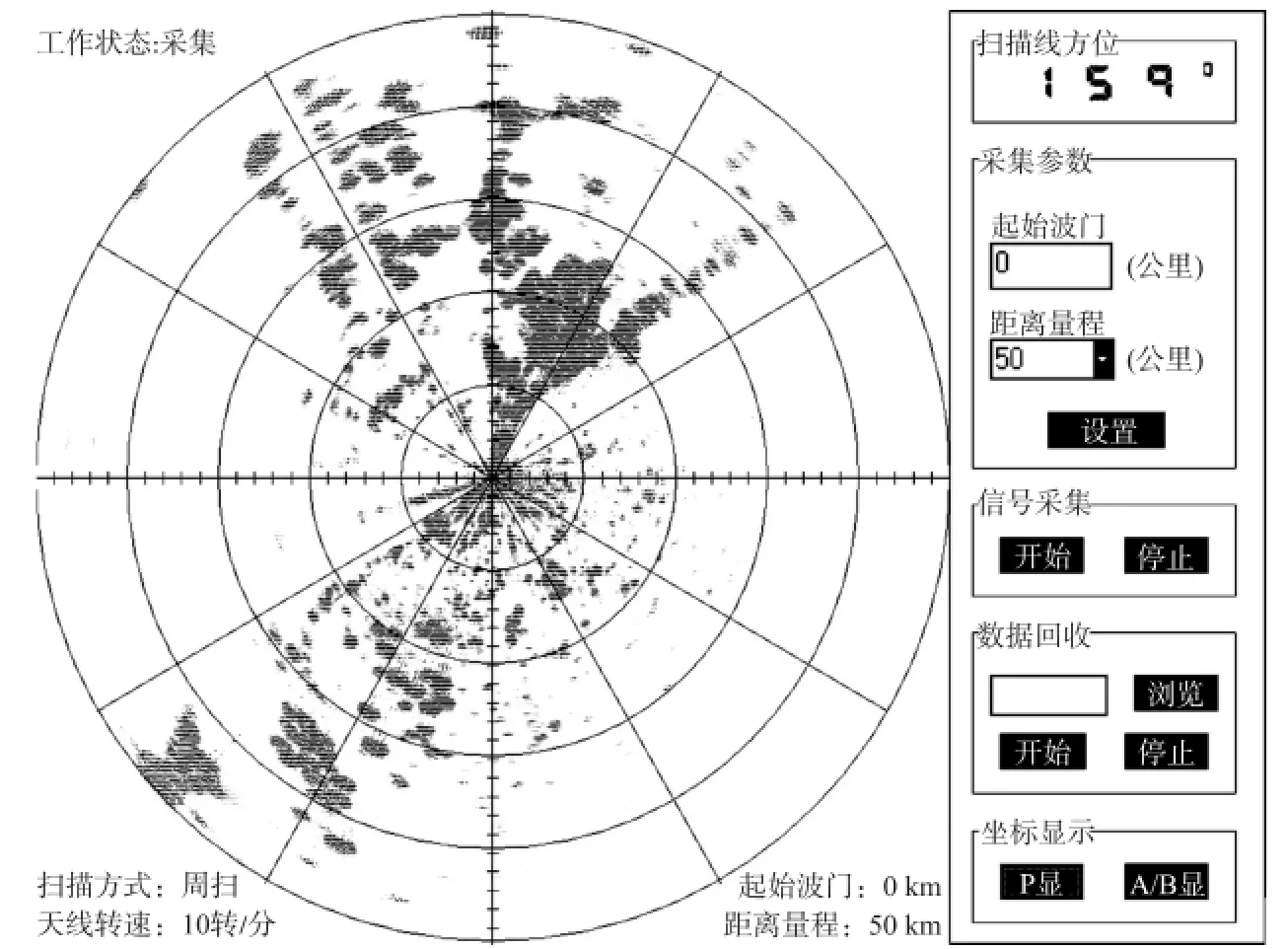

把本系统安装在某型雷达的工控机上,进行了验证性试验数据的采集处理。图5为采集到的真实雷达视频回波信号的PPI显示。

图5 试验中采集到的雷达视频回波信号

试验结果表明:本系统完全能够满足某型雷达所提出的数据处理的技术指标要求,能够对大容量的雷达回波信号进行实时高速连续采集、存储和实时显示。采集的数据能够真实地反映试验目标与周围杂波环境的特性。

[1] 王小谟,张光义.雷达与探测[M].北京:国防工业出版社,2008:7.

[2] 曹永敏,姚亚峰,陈海腾,等.基于TMS320F28335的雷达测速系统的设计[J].电子器件,2014,37(1):45-49.

[3] 汪涵,罗晓平,谢定富.雷达视频回波信号的高速采集与回放显示[J],测控技术,2009(12):126-131

[4] 张华,张蕴玉,胡修林.雷达目标回波高速采集系统的设计[J].华中科技大学学报(自然科学版).2003(10):72-75.

[5] 张鹏,杜彬彬,任勇峰.基于FPGA的超声数据采集装置的设计与实现[J].电子器件,2014,37(1):82-86.

[6] 周骞,陈金树.超高速数据采集存储系统的设计与实现[J].计算机应用研究,2003(8):126-131.

[7][美]Tom Shanley,Don Anderson.PCI系统结构[M].刘晖,冀然然,夏意军,译.北京:电子工业出版社,2001:63-65.

[8] 梁景新,薛余网.PPI雷达信号微机显示中快速极坐标—直角坐标映射[J].上海交通大学学报,2009(1):53-59.

[9] 刘翠海,温东.光栅扫描显示器上实现PPI雷达长余辉仿真[J].计算机仿真,2012(3):42-47.

[10]林良有,张伟.基于FPGA的连续采样的高速PCI采集卡设计[J].计算机测量与控制,2007(6):36-39.

[11]李洪涛,朱晓华,顾陈.Verilog HDL与FPGA开发设计及应用[M].北京:国防工业出版社,2013:125-127.

[12]孙宝鹏.基于FPGA的雷达信号处理算法设计与实现[D].北京:北京理工大学,2014.

孙玉梅(1974-),女,汉族,山东龙口人,硕士,副教授,主要研究方向为数据采集、计算机应用技术,392346519@qq.com;

张彦飞(1966-),男,汉族,黑龙江哈尔滨人,博士,高级工程师,主要研究方向为信号处理、嵌入式系统应用,1458044923@ qq.com。

Design of FPGA-Based Real-Time Radar Signal Acquisition and Display System*

SUN Yumei*,ZHANG Yanfei,WANG Meichun,WANG Xuancheng

(Department of Electrical and Electronic Engineering,Yantai Nanshan Insitute,Yantai Shangdong,265713,China)

The aim of radar signals acquisition is to prepare for radar data processing,target detection,ranging and tracking.The system employs a microcomputer with a RAID card as the acquisition control equipment.A high speed,FPGA-based radar signals acquisition card is designed.The system uses dual-port RAM in FPGA and buffer storage to provide continuous acquisition,and data selection,coordinate inquiry-list mapping technique to implement real-time PPI display on microcomputer monitor.Test result shows that the system can collect,store and realtime display radar signals at a speed of 500 thousands data-sets per second.

radar;signal;data acquisition;FPGA

TN957.51

A

1005-9490(2016)03-0639-05

EEACC:632010.3969/j.issn.1005-9490.2016.03.027