基于FPGA的SFP光纤通信控制器的研究与设计*

2016-08-18王丽娟李锦明杜东海

王丽娟,李锦明,杜东海

(中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051)

基于FPGA的SFP光纤通信控制器的研究与设计*

王丽娟*,李锦明,杜东海

(中北大学电子测试国家重点实验室,仪器科学与动态测试教育部重点实验室,太原030051)

针对高速数据存储器对光纤数据高速率、大容量的要求,设计了一种SFP(Small Form Pluggable)热插拔小封装模块高速光模块控制器。该设计采用Spartan-6 FPGA为核心控制器、高速串行技术为支撑,进行了接口电路的设计,且重点介绍了控制器的自定义协议的设计和仿真。通过分析集成比特误码率测试仪器(IBERT)测试和Chipscope抓取的数据,验证了光纤数据能够以不低于1 Gbit/s的速率进行数据存储。结果表明该设计具有封装小,可移植性强等优点,在某高速数据存储器中已得到了成功应用。

光纤通信;高速串行; FPGA;SFP光模块;高速数据存储

在光纤通信领域,光模块作为光纤通信的关键器件,小型封装可热插拔SFP(Small Form Pluggable)光模块体积小,支持热插拔,且提供了简单的模块运行使用和参数监测手段,所以SFP光模块成为研究人员的热选,最新的光模块速率已经达到10 Gbit/s及以上,且正在朝低噪声、低误码率、远距离传输方向发展。

国内外研究控制光模块多选用光纤收发器与FPGA技术相结合的方案,为了速度的提升,多选用高端FPGA芯片,然而高端的控制平台导致不理想的可扩展性、维护性,使得SFP的开发相对滞后,阻碍了其的广泛使用。

考虑到速率与后期维护使用的平衡,本文采用较易开发的Spartan-6 FPGA为控制核心,基于其内部非常高效的高速串行收发器IP硬核模块对SFP接口电路进行了大量的冗余设计,且其高效的自定义协议的实现也提高了模块的集成度。系统具有易于维护,市场适应性强等优势。

项目来源:国家自然科学基金项目(61335008)

收稿日期:2015-08-17修改日期:2015-09-17

1 高速光模块SFP及其关键技术

1.1高速光模块SFP构造原理

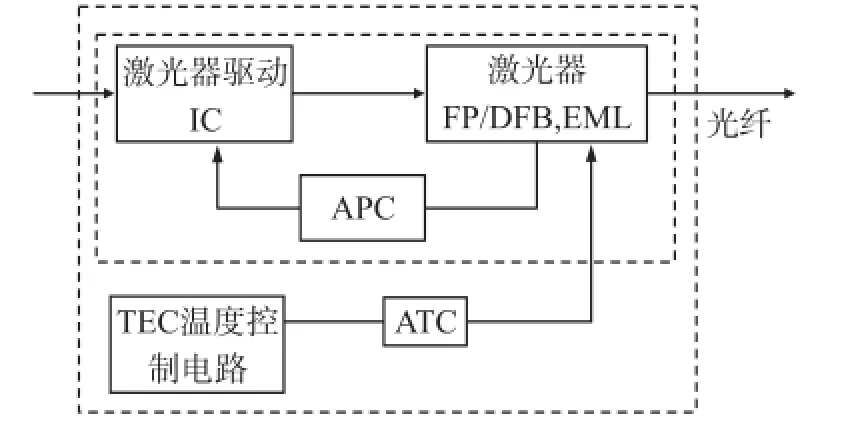

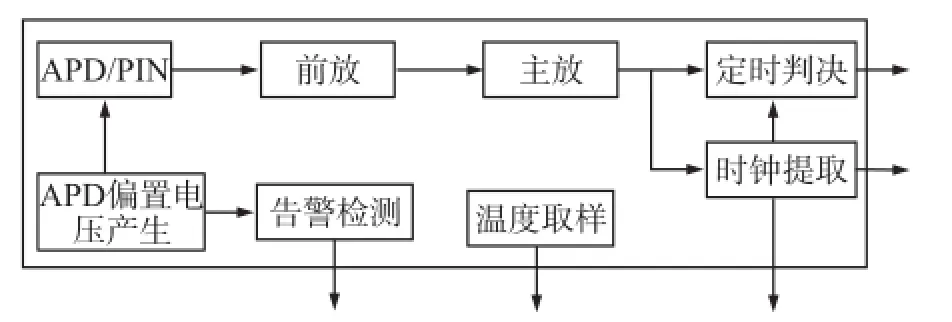

SFP光模块主要是为高速光纤通信链路中提供高速稳定的光电/电光转换功能的模块,其主要由光电发射部分和光电接收两大部分组成;光电发射部分则是用于将高速电信号转化为高速光信号;而光电接收部分则是实现与发射部分互逆的一个过程,主要用于将高速光信号转换为高速电信号,图1为光电发射部分示意图,图2为光电接收部分示意图。

图1 光模块发射部分示意图

图2 光模块接收部分示意图

光模块部分激光器内部流通过的正向电流超过了一定阈值电流后它才能发出激光;APC单元是通过检测背光二极管产生的光电流平均值来实现闭环控制的,用于实现偏置电流平稳进而达到稳定输出光功率的目的;TEC温度控制电路是通过利用温度对激光波长的一种反馈控制电路。光电接收部分APD/PIN主要用于对一定波长范围内的入射光进行光电转化。

2 SFP光电模块硬件电路设计

在本设计中,控制芯片选用xilinx的Spartan-6系列中的SLX100T型号的FPGA,内含101261个逻辑单元,184 304个逻辑的单元,并且含有692个分离RAM和4824个块RAM,其中8个内嵌IP硬核高速串行收发器足够本设计使用。为了保证配置成功的几率和灵活的配置方式,设计了兼容SPI 和BPI的配置芯片挂载方式,支持串行和并行数据的传输。

2.1接口电路设计

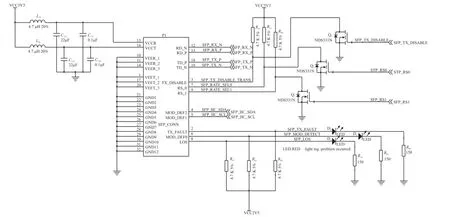

因SFP光电模块属于高速精密器件,其工作频率非常高,为使SFP能正常工作,它要求供电电压的精度保证在±5%以内,供电电流需在300 mA以上,其用于滤波的电感的直流等效阻抗应该小于1 Ω,供电电源所产生的浪涌电流必须小于30 mA,并且电源还必须使用专有的滤波网络,为此对于该部分电路设计务必非常严谨,图3为SFP模块的接口电路原理图。因本设计中选定的FPGA芯片内部集成的高速串行收发器,并且被分配在了两个不同的BANK(Bank123和Bank101)中,本设计的SFP光电模块被设计在Bank123中,并指定其占用编号为0的高速串行收发器。

图3 SFP接口电路

VCCT是用于为SFP模块的发送部分供电的引脚;VCCR是用于为SFP模块的接收部分供电的引脚;TD-/+是发射部分的差分信号输入引脚,进行电路设计时传输链路上应该采用交流耦合方式,同时布线时应该保证差分传输线上的等效阻抗为100 Ω,其传输链路上的差分信号摆幅应该保持在500 mV~2 400 mV范围内;RD-/+为接收部分差分信号输出引脚,在进行电路设计时也必须和TD-/+一样也应该采用交流耦合方式,同时布线时也应该保证差分传输线上的等效阻抗为100 Ω,其传输链路上的差分信号摆幅应该保持在370 mV~2 400 mV范围内;Mod_Def1即是SFP模块内部I2C模块的时钟线引脚;Mod_Def2即是SFP模块内部I2 C模块的数据线引脚;TX_Fault:开集/漏极输出引脚,激光器失效时该引脚表现为高电平,当SFP模块正常工作时该引脚表现为低电平(<0.8 V);TX_Disable:SFP模块发送关断使能输入引脚,当SFP模块关断时该引脚表现为高电平(2 V~3.3 V),当该引脚悬空时其等价于关断模式,当SFP模块正常工作时该引脚表现为低电平(<0.8 V);LOS:开集/漏极输出引脚,当SFP模块的输入光功率低于最差接收光功率时该引脚表现为高电平用于报警提示。

其光纤通路用到的FPGA内部的高速串行收发器对于外部参考时钟的要求时钟频率的误差应该稳定在10×10-6(Parts Per Million)以内,并且要求时钟必须有极低的抖动水平(皮秒(ps)级别),其参考时钟为125 MHz的高速时钟,最终选择了ICS公司的高性能时钟芯片ICS8440241I,ICS8440241I芯片产生的时钟经过一个差分对输出(Q0/NQ0),并且在差分传输线上采用了交流耦合方式,可进一步降低时钟上的高频干扰,布板时要求交流耦合电容必须尽可能靠近时钟输出引脚;该芯片的输出时钟范围为122.5 MHz~170 MHz,并且当采用外部25 MHz晶振用于产生125 MHz时钟时,其相位抖动仅有0.32 ps,其误差稳定在3×10-6以内,可以满足SFP模块的时钟设计要求。

3 SFP光电模块控制程序设计与仿真

3.1SFP光纤链路高速串行收发器例化

Spartan-6系列的FPGA集成了非常高效的高速串行收发器IP硬核模块,该模块需要利用高速串行收发器作为底层物理基础,且本设计中不考虑采用现成的接口协议,所以在此部分对于FPGA底层物理实现只通过IP核生成向导调用一个不带任何协议的裸收发器,也即只包含了基本的物理编码子层(PCS)和物理介质介入子层(PMA)的收发器,对于通信协议将采用自定义的方式实现,图4为一个裸收发器的示意图,并将该裸收发器封装后使其和上层协议控制之间通过GMII接口方式进行数据和命令的交互。

图4 SFP光纤链路高速串行收发器

3.2SFP光纤链路通信协议定制

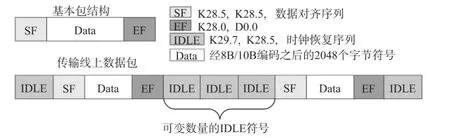

本设计中,光纤有效数据的传输速率即有效载荷速率设定为 1 Gbit/s,故选择传输线的速率为1.25 Gbit/s,则剩余的20%载荷可用于帧头、帧尾以及空闲标志的开销。因为光纤传输时数据传输的两个终端肯定会使用不同的振荡器来驱动各自的收发器,所以必须考虑时钟修正的问题,所以在定制数据帧长度时必须折衷其与时钟修正的矛盾。

为折衷数据帧和时钟修正之间的矛盾,就必须计算二者之间各自的界限,然后在二者之间选取一个中间值。本设计中的数据有效载荷要求为1 Gbit/s,总的带宽为1.25 Gbit/s,假如选择的数据帧中有效载荷为2 048 byte,假设协议字符序列开销为10 byte(帧头:2 byte,帧尾:2 byte,空闲标志:6 byte),则数据流中协议开销率为10/2 058,约为5%,考虑到数据传输带宽,设计要求所能承受的开销为10%,所以就可以将数据帧缩小20倍;然而在进行时钟修正时,则需要数据帧越小越好,假设系统要求高速串行收发器的参考时钟精度要达到20×10-6,若将收发器的时钟对齐符号设置为2个符号宽的空闲标志字符序列,则时钟则最多每隔49 999(1 000 000/20-1=49 999)个字符符号必须进行一次时钟修正。所以,空闲标志字符之间的距离应该小于这个数值,一般情况下要求其值小于最大空闲标志字符距离的1/3,本课题中选择1/24作为最大空闲标志字符距离,即数据包长度约为2 083 byte,本课题选择协议包长度为2 058 byte,而剩余的则全部填充空闲标志序列字符。至此,一个定制的通信协议就已建立。在本模块中,发送器主要负责在传输链路中的高速串行数据流中插入足够多的空闲标志序列字符,而接收器则负责从接收的高速串行数据流中剔除所有的空闲标志序列字符、帧头序列字符和帧尾序列字符。最后,在接口处添加一些自定义的逻辑后再启动8 byte/10 byte的高速串行收发器就可以完成整个协议了,图5显示了自定义协议的基本设置。

图5 自定义协议格式

4 用户接口模块仿真与测试

4.1光纤通信接口模块仿真

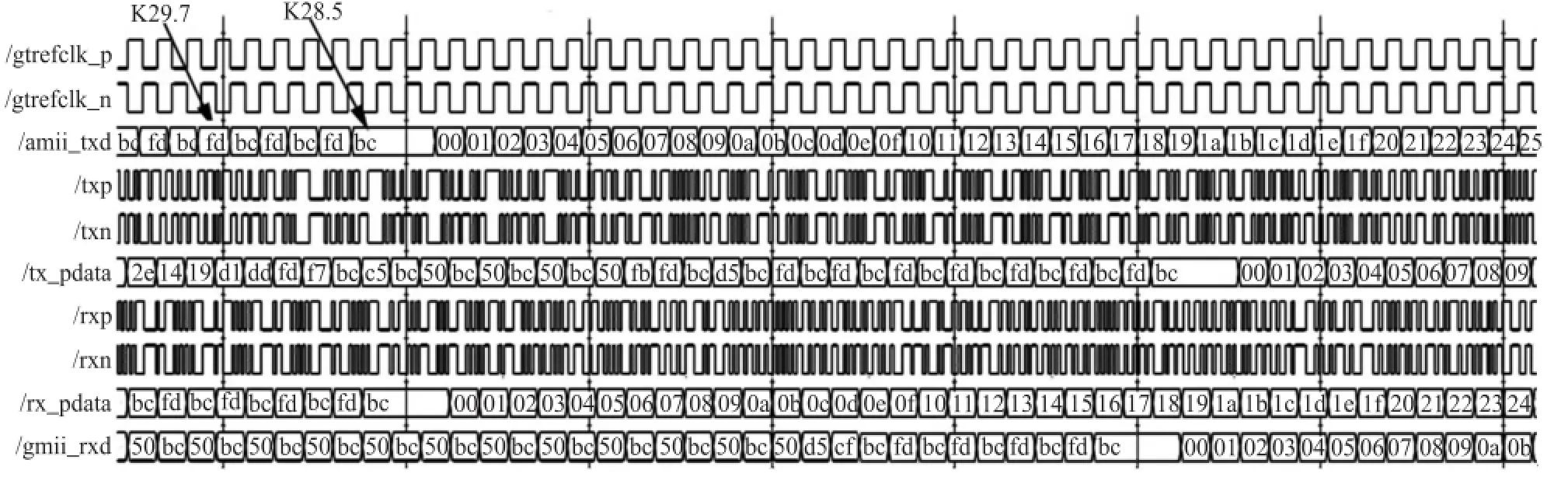

协议定制好之后,遵照协议编写控制程序,然后建立测试文件利用Modelsim仿真工具对该模块进行波形仿真,仿真波形如图6所示。

经过向导调用高速串行IP硬核和在IP硬核基础上架构自定义的通信协议后,建立专门的测试文件(该测试文件的传输数据是连续递增的数据)。通过图6可以看出,gmii_txd的发出数据遵循了自定义的协议包格式(0xfd 0xbc构成IDLE序列:K29.7 K28.5;0xbc 0xbc构成协议包SF序列:K28.5 K28.5;紧接之后的即是连续递增的数据。),同时显示器数据接收端也准确接收到所发送出的数据。对于高速串行接收端,通过将显示器接收的数据传递给接收仿真激励,然后再经过仿真传递给gmii_rxd,通过上图可以看出数据也是按自定协议包格式接收的,故该模块实现了SFP光模块链路的正常通信。

图6 SFP模块仿真图

4.2光纤链路测试

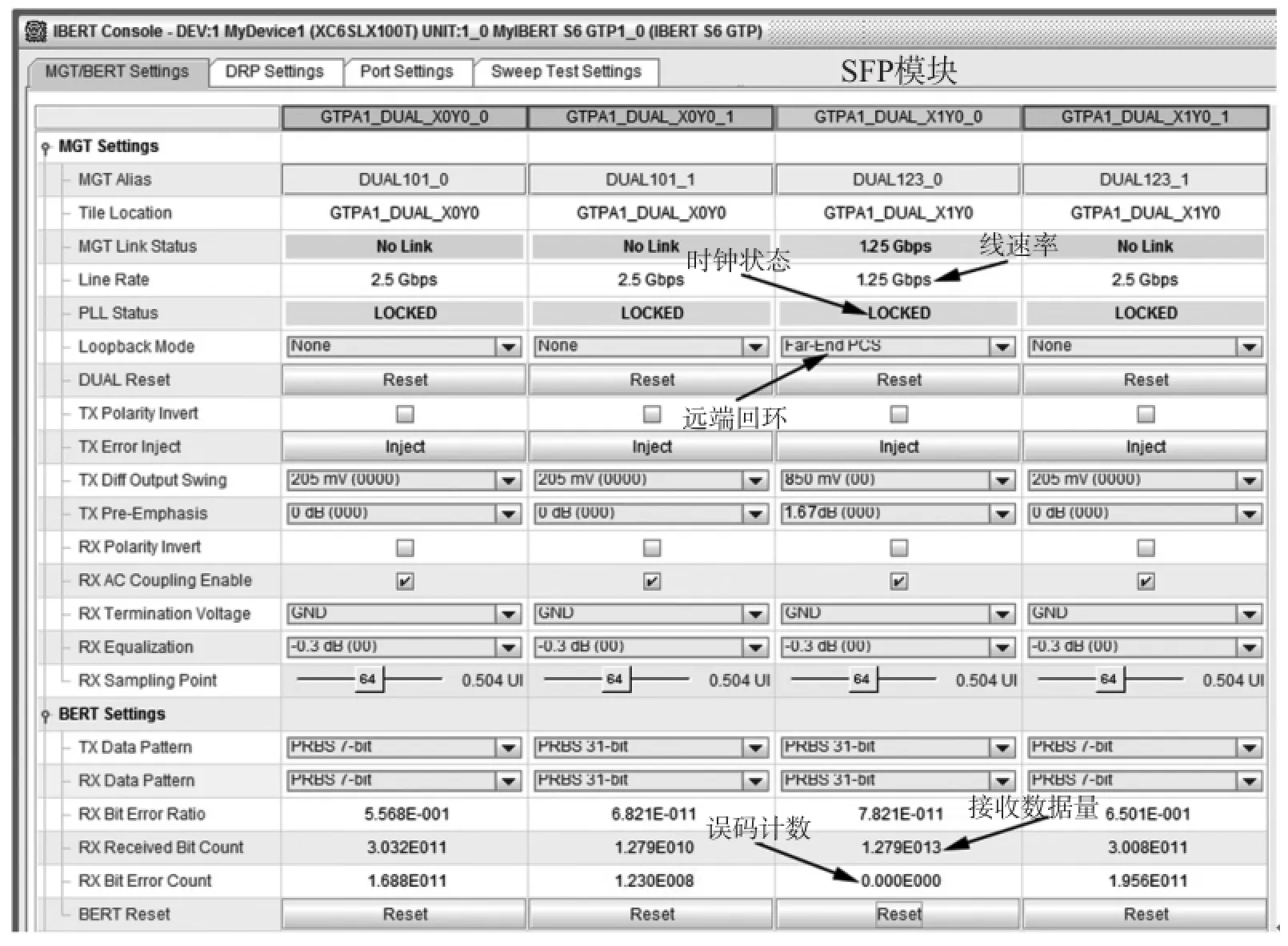

Spartan-6系列的FPGA中集成了非常高效的高速串行收发器IP硬核模块,为了更简洁的使用SFP模块,通过自己定制协议的方式和其他模块进行数据的交流;本设计使用了集成比特误码率测试仪器IBERT(Integrated Bit Error Ratio Tester)作为进行高速串行信号质量测试的辅助工具。首先在FPGA内部产生一个连续的数据流,通过SFP收发器经回环光纤线收发。测试时,先测试该模块的高速串行收发器是否能够正常工作,此步是通过示波器绘制出链路工作时的眼图,通过眼图观测眼图达到测试的目的;其次,通过光模块的回环后,在FPGA内部通过对比发送和接受数据并通关过相应的指示灯进行标识的方式,进而验证整个课题数据源前端的工作准确度和正确性。为保证测试平台中的光纤回环通畅、SFP收发器以及SFP接口能正常工作,首先对光纤链路利用IBERT进行远端回环测试。理论上在误码率保持在 10-10~10-12时,通信距离可以达到10 km及以上,通过图7可以看出,该模块的传输速率被正确锁定,在回环光纤线为5 m时,模块高速通信在传输数据量达到TB级别时,其比特误码计数仍然保持为0。所以该模块能够达到设计要求,可以进行下一步测试。

数据链路正常工作后,按照课题设计的自定义协议包在FPGA内部组织高速数据流,然后发送给高速串行收发器,之后数据流经光纤回环后,再由收发器接收后存储到内部的FIFO,图8是通过Chipscope所抓取的数据图,从该图中可以看出协议包被正确的传送至高速串行收发器的用户数据接口(gmii_txd),之后数据又被正确的接收并且通过收发器另一个用户数据接口(gmii_rxd)传输到FIFO中,故该模块能够以规定的协议进行数据包的传输。

图7 光纤链远端回环测试

图8 光纤链路数据传输Chipscope观测图

5 结论

本文基于 Xilinx公司的Spartan6系列的FPGA,搭建了SFP光纤通信的硬件平台,通过调用FPGA内部的IP硬核GTP收发器,完成了SFP光电模块的用户接口设计,有效地进行海量数据的传输,并且最大限度地减少了误码率的发生,避免数据的丢失,并成功地应用到某高速数据存储器中,并将高速的数据经过以太网传至PC机,验证了该模块以不低于1 Gbit/s的光纤数据能够进行高速存储,在此光纤模块的设计所使用的FPGA成本低,功能强,光纤模块体积小成本低,整个系统的可移植性强,很好地兼容中低端高速存储器,应用前景广阔。

[1] 周东杰,都磊.基于FPGA的新型SFP光模块检测系统[J].计算机系统应用,2013,22(4):161-163.

[2] 白胜月.基于FPGA的光纤传输系统的设计与实现[J].电子质量,2012(2):29-37.

[3] 王妮.基于SFP光模块控制系统的设计和实现[J].光器件,2010(9):36-38

[4] Parklin N,Bartur M,Nesset D,et al.Gigabit SFP Transceiver with Integrated Optical Timedomain Reflectometer for Ethernet Access Services[D].IET Conference Publications,2013:161-163

[5] 张莉,夏振中,秦艳,等.10 Gbit/s SFP+短距离光模块的温度补偿技术[J].光通信研究,2015(1):31-34.

[6] Pereira R C,Combo A,Correia M,et al.Ultra High-Frequency Data Acquisition AMC Module for Highperformance Applications[J].Fusion Engineering and Design,2013,8(6):1409-1413.

[7] 王增福.高速串行传输关键技术的研究与设计[D].西安:西安电子科技大学,2012.

[8] 唐兴,唐宁.光纤通道8B/10B编码的ASIC研究与设计[J].电子器件,2011,34(2):210-214.

[9] 张杰.一种高速数据存储方法的研究[D].中国科学技术大学,2013.

[10]瞿鑫,吴云峰,李华栋,等.基于FPGA的千兆以太网数据传输的设计与实现[J].电子器件,2014,37(4):662-664.

[11]Ibala C S C.Arsha K K.Predicting and Controlling FPGA Device Hat Using System Monitor and IBERT(Internal Bit Error Ratio Tester),United States:IEEComputer Society,2009:370-374.

[12]孙科林,周维超,吴钦章.基于FPGA的高速串行光纤图像传输检测平台[J].光电技术应用,2012,33(2):283-285.

[13]胡庆红.SFP光收发模块测试平台的研究与设计[D].武汉:武汉理工大学,2013.

王丽娟(1989-)女,汉族,山西运城人,中北大学仪器与电子学院,硕士在读,电路与系统专业,wlj_lab@sina.com;

李锦明(1971-),男,汉族,重庆垫江人,中北大学仪器与电子学院,博士,副教授,主要从事电路设计及性能测试等相关领域等方面的教学与科研工作,ljm_lab@sina.com。

The Research and Design of SFP Optical Fiber Communication Controller Based on FPGA*

WANG Lijuan*,LI Jinming,DU Donghai

(National Key Laboratory for Electronic Measurement Technology,Key Laboratory of Instrumentation Science&Dynamic Measurement of Ministry Education,North University of China,Taiyuan 030051,China)

Aiming at the requirement of high speed data storage to optical data with high speed and large capacity,a new SFP(small form pluggable)hot swap small package module with high speed optical module is designed.The design adopted spartan-6 FPGA as the core controller,high-speed serial technology as technical support,accomplished the hardware design of interface circuit and focused on the design and Simulation of the custom protocol of the controller.It is verified that the optical data package is correctly transmitted to user data interface of the highspeed serial transceiver with the speed rate more than 1 Gbit/s through test of the integration of the bit error rate test instrument(IBERT)and data captured by Chipscope.The results show that the design has the advantages of small package,wide portability,etc.and it has been successfully applied in a high speed data storage.

optical fiber communication;high-speed serial;fpga;sfp optical module;high speed data storage

TN919.34

A

1005-9490(2016)03-0605-06

EEACC:6260;6150C10.3969/j.issn.1005-9490.2016.03.021