环路滤波器中运放参数对锁相环性能影响分析

2016-08-01张大鹤

张大鹤

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

环路滤波器中运放参数对锁相环性能影响分析

张大鹤

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

摘要为了研究锁相环路滤波器中运算放大器的非理想性的影响,分析了运算放大器的单位增益带宽、等效输入噪声电压密度、输入噪声电流密度、转换速率、输入输出电压范围、稳定性、输入偏置电流和电源抑制比等参数,以及这些参数对锁相环的相位噪声、杂散和稳定性等指标的影响。对部分理论分析结果进行了试验验证,试验结果与理论分析基本一致。

关键词锁相环;运算放大器;频率合成;相位噪声;相位余量;杂散

0引言

频率合成器当前广泛采用锁相频率合成的方式。各种锁相环中,应用最广泛的是电荷泵锁相环[1],其有电压型和电流型2种形式。为了保证电压型电荷泵鉴相器的输出电压恒定[1],或者扩展电流型电荷泵鉴相器的控制电压输出范围,经常需要使用运放来搭建有源环路滤波器。

运放的部分参数对于锁相环的性能指标有很大影响。而在锁相环设计过程中,运放的大部分参数不便仿真,设计时往往将运放理想化,导致很多问题未能预见,严重影响了设计质量。当前,国内尚未发现这方面进行综合分析的文章,进行理论分析很有必要。

本文对运放部分参数的影响进行理论分析,提出了运放选型和电路设计的要点,并设计试验方案对分析结果进行验证。

1运放参数对锁相环影响的原理

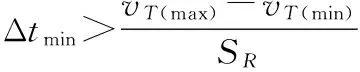

以电流型电荷泵锁相环为例,一个典型的二阶有源环路低通滤波器主要由运放、积分滤波器和辅助低通滤波器组成,电路图如图1所示。

图1 典型二阶有源环路低通滤波器电路

运放有多个参数,下面主要对影响较大的几个参数进行分析。

1.1单位增益带宽(fT)

实际运放的直流增益虽然很大,但其开环-3 dB带宽非常小,通常只有几~几十 Hz[2]。随着频率的提高,运放的增益迅速下降。运放的增益降到1时的频率称为运放的单位增益带宽(fT)。

在有源环路低通滤波器中,如果运放的增益不足,则环路低通滤波器的理想积分作用不能实现,环路无法实现对参考信号相位的正常跟踪,甚至造成环路失锁。所以,应当选用fT足够的运放,其fT应远大于环路的设计带宽。

在有源环路低通滤波器中,运放的增益对阻带抑制度影响很大。频率超过fT后,运放的增益降到1以下,则阻带抑制接近消失。对高频干扰有抑制需求时,可选用fT远大于干扰频率的运放,或者视情况增加辅助低通滤波器。

1.2等效输入噪声电压密度(vn)

运放的输出噪声电压直接调制到VCO的输出,叠加到VCO的相位噪声中。VCO的数学模型为:

ω=ω0+Kvu(t)。

(1)

通过式(1)可以推导出,开环状态下,在频偏f处,理论上输出噪声电压vn(f)在VCO上产生的相位噪声P(f)为:

(2)

由式(2)可见,运放的输出噪声电压造成的影响与VCO的压控灵敏度和噪声的偏移频率相关。

环路锁定后,环路带宽内的VCO噪声由于受到环路反馈的抑制,通常可以忽略,应主要考虑环路带宽附近和环路带宽以外的相位噪声影响。

1.3输入噪声电流密度(in)

运放的输入噪声电流不直接调制到VCO的输入端,而是通过环路滤波器的积分作用,转化成噪声电压,间接调制到VCO上。对于环路带宽外的噪声被环路低通滤波器滤除,主要影响环路带宽内的相位噪声。

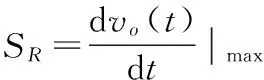

1.4转换速率(SR)

运放的转换速率SR是指放大电路在闭环状态下,输入为大信号时,输出电压对时间的最大变化速率。其定义[4]为:

(3)

有源环路滤波器中,运放的输出电压提供给VCO调谐使用,所以SR是锁相环的换频时间的一个限制条件。锁相环的最短换频时间Δtmin满足:

(4)

式中,vT为VCO的调谐电压。

1.5输出电压范围

大部分运放的输出电压范围不能接近供电电压区间。如果VCO需要的调谐电压已经接近运放的供电电源电压,则应该考虑选用具有电压轨到轨(Rail-to-Rail)输出的运放。

1.6输入电压范围

与输出电压范围类似,大部分运放的设计输入电压范围不能接近供电电压区间。如果输入电压超出该范围,可能影响指标,甚至造成输出反向而无法工作。

为了保证环路正常捕捉,如果失锁条件下鉴相器的输出电压可能接近运放的供电电源电压,可以考虑选择可支持该输入电压的运放,或者在电路设计时采用调整预置电压、减小电荷泵的输出电流等措施来保证运放的输入电压不超范围。

1.7开环电压增益参数

运放的开环电压增益参数可以用波特图来描述。有源环路滤波器作为一种闭环反馈系统,必然存在稳定性的问题。当运放的相位余量不足时,系统容易发生不稳定的情况。

目前商业化集成运算放大器内部基本上都进行了频率补偿,但不一定都能保证在深度负反馈条件下稳定工作[2]。

有源环路滤波器设计时,应参考运放的波特图,选用稳定性好的型号,工程上应保证运放在单位增益时相位余量至少在20°以上[5]。也可以考虑电路中增加相位补偿的方式,保证运放稳定工作。

1.8增益带宽积(GBW)

锁相环路的相位余量不足时,系统容易发生不稳定的情况,在环路带宽附近的相位噪声曲线会出现鼓包,输出频谱变差[6]。运放自身参数带来的相移直接影响到环路的相位余量。

对于具有相对恒定增益带宽积GBW的运放来说,GBW≈fT。如果环路带宽为LBW,则运放带来的相移为[7]:

φ=arctan(LBW/GBW)。

(5)

也就是说,环路的相位余量减少φ度,设计时应计算在内。

1.9输入偏置电流(ib)

输入偏置电流ib是指运放正常工作状态下输入端吸收的电流。在锁相环中,该电流需要由鉴相器的电荷泵提供,这样就增加了电荷泵的输出时间,加重了鉴相纹波干扰。

运放的ib与输入电压有关。BJT输入级的运放的输入偏置电流一般在nA级以上,甚至达到μA级,相对来说比较大。FET输入级的运放,其输入偏置电流大多在100 pA以下,基本上不造成影响。

锁相频率合成器中,为了抑制鉴相纹波干扰,可以考虑选择fT远高于鉴相频率的运放。也可以在环路滤波器中增加一级或多级辅助低通滤波器进行抑制。

1.10电源抑制比(PSRR)

运放的供电电源存在噪声和干扰时,运放会输出来自电源的噪声电压,调制到VCO的输出频率上。

运放的电源抑制比PSRR定义为电源干扰电压与运放输出干扰电压的比值[2]。PSRR一般随干扰信号频率升高而降低,频率提供到一定程度后基本不再有抑制。

设计中主要需考虑环路带宽附近和带宽外的电源噪声的影响。运放的供电电源噪声较大时,可考虑选用高电源抑制比的运放。由于运放工作电流普遍很小,加强电源的滤波处理也很方便。

2试验方案

为了验证前面的分析,选择了下面几种运放进行试验:ADI公司的AD8033ARZ、OP184ES、AD797ARZ和TI公司的OPA211AID。

受限于测试条件,本次试验主要测试对于相位噪声和杂散指标影响较大的几个参数:单位增益带宽(fT)、等效输入噪声电压密度(vn)和输入偏置电流(ib)。根据厂家提供的资料,其相关技术指标如表1所示。

表1 试验选用运放的相关指标

试验中,锁相环路输出频率为10 GHz,鉴相频率100 MHz。为了便于验证,环路滤波器采用较为简单的二阶有源环路滤波器,环路带宽50 kHz,相位余量60°,原理图如图2所示。

图2 试验电路原理

图2中鉴相器选用ADI公司的ADF4106BRUZ。VCO选用Hittite公司的HMC512LP5E,输出10 GHz时相噪-86 dBc/Hz@10 kHz、-110 dBc/Hz@100 kHz,压控灵敏度为200 MHz/V,对应调谐电压5 V。

3测试结果

相位噪声与杂散指标的测试结果如表2所示。

表2 相位噪声与杂散指标测试结果

3.1相位噪声测试结果分析

总相位噪声主要取决于鉴相器、VCO和运放的噪声的叠加[8]。

(6)

测试结果表明,使用不同型号运放进行测试,环路带宽内相位噪声影响较小。环路带宽附近和带外相位噪声差别较大,使用vn较低的运放时相位噪声有明显优势。这些都与1.2节中的分析一致。

3.2杂散抑制测试结果分析

输出杂散主要是鉴相频率干扰[1]。测试结果表明,虽然AD797的ib较大,但是使用AD797时鉴相频率干扰最小。根据1.1节中的分析,这是由于其fT高于本次试验的鉴相频率(100 MHz),对鉴相频率干扰有了一定的抑制。

使用AD8033时鉴相频率干扰稍大,应该是由于锁定后噪声较差,导致电荷泵输出时间变化造成的是整个环路反馈控制的综合结果。

另外,使用AD797时,频偏大约39 MHz处有高达-14 dBc的杂散。根据厂家提供的开环电压增益参数图,AD797不能保证单位增益下稳定工作,自激后带来杂散,这与根据1.7节中的分析一致。

4结束语

分析了运放的多个参数对锁相环路各项指标的影响,给出了相关公式,并通过试验进行了验证。文中是以常用的电流型电荷泵锁相环、二阶有源环路滤波器为例进行分析,但对于电压型电荷泵锁相环和其他有源环路滤波器形式也基本适用。

测试结果与理论分析结果基本一致。对于锁相环路中运放的选型和有源环路滤波器设计具有一定的指导意义。

参考文献

[1]王福昌,鲁昆生.锁相技术[M].武汉:华中科技大学出版社,1997.

[2]康华光,陈大钦.电子技术基础:模拟部分(第4版)[M].北京:高等教育出版社,1999.

[3]LEE P.Low Noise Amplifier Selection Guide for Optimal Noise Performance[R].Analog Devices,2009:4-8.

[4]CARTER B,MANCINI R.运算放大器权威指南(第3版)[M].姚剑清,译.北京:人民邮电出版社,2010.

[5]SIMPSON C.Linear Regulators:Theory of Operation and Compensation[R].National Semiconductor,2000:2-5.

[6]杨新功,宋庆辉.超宽带低相噪频率合成器的实现[J].无线电通信技术,2006,32(3):39-41.

[7]Analog Devices Inc.Ultra-Fast Settling PLL with RF to 13 GHz[R].Analog Devices,2013:3.

[8]蔡鹏飞,李青平,杨懿,等.基于谐波混频技术的宽带频综的设计[J].无线电通信技术,2013,39(8):73-75.

doi:10.3969/j.issn.1003-3106.2016.07.17

收稿日期:2016-04-25

中图分类号TN722.7+7

文献标志码A

文章编号1003-3106(2016)07-0064-03

作者简介

张大鹤 男,(1984—),工程师。主要研究方向:频率合成技术。

Analysis of Influence on PLL Performance by OP AMP’s Parameters in PLL Filter

ZHANG Da-he

(The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China)

AbstractIn order to research the influence of OP AMP’s non-ideal characteristics in PLL filter,some parameters of OP AMP are analyzed,including unity-gain bandwidth,input voltage noise density,input current noise density,slew rate,input/output voltage range,stability,input bias current and PSRR.The influence of the parameters on phase noise,spurious rejection and stability of the PLL is deduced.An experiment is conducted in order to verify some of the theoretical results.Experiment results are generally coincident with theoretical ones.

Key wordsPLL;OP AMP;frequency synthesis;phase noise;phase margin;spurious

引用格式:张大鹤.环路滤波器中运放参数对锁相环性能影响分析[J].无线电工程,2016,46(7):64-66,88.